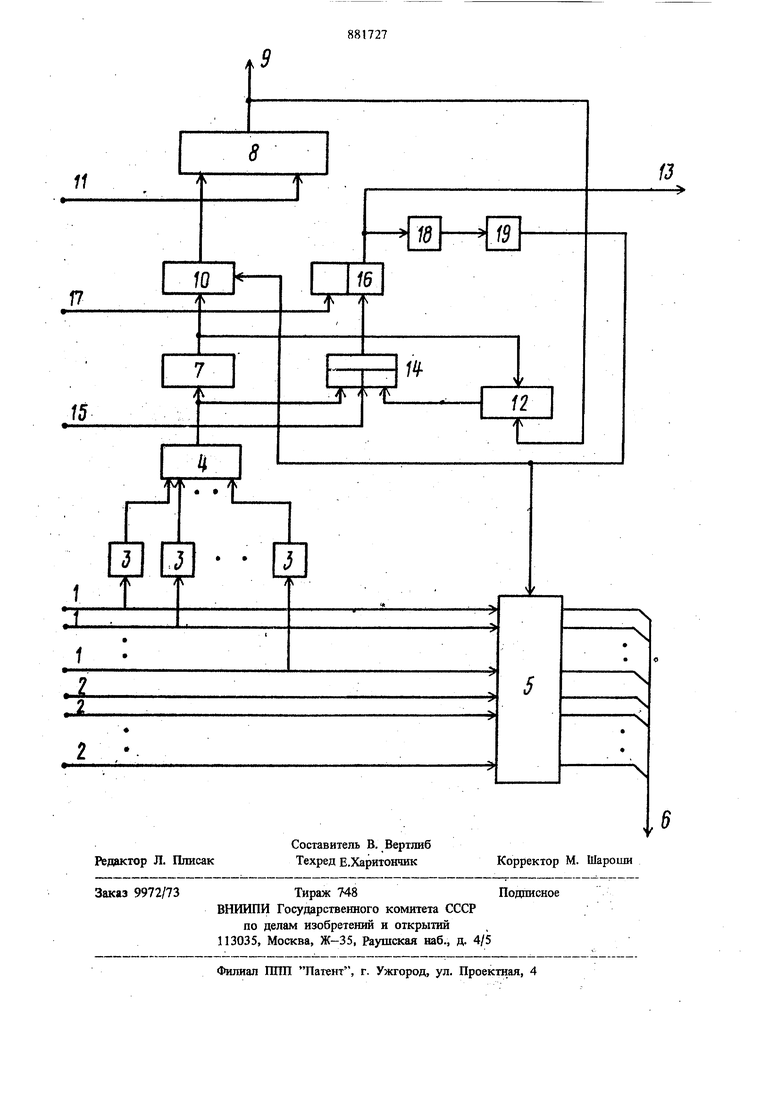

Изобретение относится к вы«шслительной технике и может быть использовано для сняти и записи в память ЭВМ диаграмм функционирования цифровых объектов для целей исследования и контроля. Известны устройства для сбора дискретной информации, работающие по принципу последовательного циклического опроса точек контактирования с источником информации (дискретным датчиком, узлом ЭВМ и т.п.) и содержание коммутатор точек наблюдения или каналов, счетчик адресов точек наблюдения, связанный с коммутатором, схему сравнения и блок местного управления 1. Недостаток зтих устройств состоит в ограниченной области применения, так как использование последовательного циклического опроса не позволяет применять их при высоких частотах смены информации и большом числе информационных каналов из-за того, что за время опроса могут произойти неоднократные изменения информации и, следовательно, ее потери. Наиболее близким к изобретению по сущ;Ности технического решения является устройство для сбора данных от двухпозиционных датчиков, содержащее регистр адреса, соединен ный выходом со входами блока сопряжения с ЭВМ и дешифратора, выходами подключенного ко входам блока памяти и триггера, второй вход которого соединен с формирователем импульса, генератор импульсов, переключатель режима работы, коммутатор, соединенный соответствующими входами с выходами регистра и блока памяти, а выходом - с первыми входами регистра сдвига и блока сравнения, второй вход которого подключен к выходу элемента ИЛИ, а выход - ко входу дополнительного переключателя. 2. Недостаток данного устройства состоит в низкой достоверности работы, что обусловлено возможностью потери информации. Цель изобретения - повышение достоверности работы устройства. Поставленная цель достигается тем, что в устрой,ство, содержащее регистр адреса, выход которого является выходом адреса устройства. григгер управления, формирователь импульсов, коммутатор, схему сравнения и память, введены группа формирователей импульсов, элемент ИЛИ, счетчик, элемент И и элемент задержки, причем выход элемента ИЛИ соединен со входом счетчика и первым входом коммутатора, а каждый вход через соответствующий формирователь импульсов группы - с соответствующим входом первой группы входов устройства, второй и третий входы коммутатора подключены соответственно к входу пере ключения режима работы устройства и выходу схемы сравнения, первый вход которой соединен с выходом счетчика и первым входом элемента И, а второй - с выходом регистра адреса, первый и второй входы которого соединены соответственно со входом адреса устройства и выходом элемента И, вторым входом подключенного ко входу памяти через последовательно соединенные формирователь импульсов и элемент задержки к выходу триг гера управления и выходу управления устройства, входы триггера управления соединены соответственно со входом обнуления устройства и выходом коммутатора, первая и вторая группы входов и группа выходов памяти соединены соответственно с первой и второй группами входов и группой выходов устройств На чертеже представлена блок-схема устройства. Устройство содержит группу входов 1 для дискретной информации от входов исследуемой схемы (ИС), группу входов 2, подключаемых к выходам ИС, формирователи 3 импульсов перехода входов объекта в новое состояние, вырабатьшающие короткие импульсы под воздействием входного сигнала с О на Г или с 1 на О, элемент ИЛИ4, память 5 для запоминания входного слова и хранения входной информации на время ее передачи в ЭВМ, группу выходов 6 устройства, счетчик 7, предназначенный для присвоения каждому входному слову порядкового номера, регистр 8 адреса, предназначенный для запоминания номера слова, используемого при размещении входного слова в оперативной памяти ЭВМ, выход 9 адреса, элемент И 10, вход 11, посту пающий из ЭВМ и используемый при повторно записи информации с ИС, схему сравнения 12) вырабатьшающую сигнал для записи в ЭВМ входного слова, пропущенного в предыдущем цикле записи, выход 13 управления, коммутатор 14, вход 15 переключения режима работы устройства, триггер 16 управления, предназначенный для взаимной синхронизации работы устройства и ЭВМ, вход 17 обнуления, элеменх задержки 18, формирователь 19 импульса, который реагирует только на положительный фронт сигнала и предназначен для формирова74ния сигнала разрешения записи информации в регистры памяти 5 и регистр 8. Устройство работает следующим образом. Устройство имеет два режима работы, установка которого производится сигналом по входу 15. В режиме записи информации на вход 15 на ЭВМ поступает сигнал, обеспечивающий прохождение через коммутатор 14 импульсов с выхода элемента ИЛИ 4. Изменение логического состояния хотя бы на одном из входов ИС воздействует на соответствующий формирователь 3, с выхода которого на вход элемента ИЛИ 4 поступает короткий импульс. Сигнал с выхода элемента ИЛИ 4 вызывает приращение на единицу счетчика 7 и через коммутатор 14 производит установку триггера 16 в единичное состояние, которое по.выходу 13 передается в ЭВМ и воспринимается ей как команда на вьшолнение программы записи входного слова. При этом формирователь 19 под воздействием положительного фронта сигнала с триггера, задержанного элементом задержки 18, формирует сигнал, который производит запись информации в память 5 и переписывает новое содержимое счетчика 7 в регистр адреса. Необходимость введения задержки импульса записи обусловлена переходными процессами как в самой ИС, так и в счетчике 7. Получив команду, ЭВМ вьшолняет программу записи входного слова, при этом сначала считывается значение адресной информации с выхода 9, затем с выхода 6 считьшается входное слово и записывается в ячейку памяти, номер которой обусловлен считанным адресом. В процессе вьшолнения данной программы появление нового слова на входах устройства вызывает приращение кода счетчика 7 на единицу, но не меняет состояние триггера управления. Сброс триггера 16 осуществляется ЭВМ после вьшолнения программы записи импульсом, поступающим на вход 17, что переводит устройство в состояние ожидания нового входного слова. Очередной импульс с выхода элемента ИЛИ 4, обусловленный изменением кода на входах 1, вновь вызьтает. программу записи в ЭВМ, при этом адрес записи смещается на число пропущенных слов. По окончании программы функционирования ИС в памяти ЭВМ хранится массив информапда, в котором зафиксированы изменения логических состояний всех точек контактирования ИС с устройством. Возможные потери информации, возникающие в процессе записи из-за конечного быстродействия ЭВМ, проявляются в виде пробелов в массиве ОЗУ. Восстановление пропущенной информации, т.е. заполнение этих пробелов, производится в процессе повторных циклов функционирования

ИС, при этом устройство переводится в режим восстановления информации путем смены сигнала на входе 15, что обеспечивает прохождение через коммутатор 14 сигналов со схемы сравнения 12.

Перед началом очередного цикла ИС устанавливается в исходное состояние, и в ЭВМ производится поиск первой незаполненной ячейки массива ОЗУ и запись ее адреса в регистр 8 по входу 11. В каждом цикле функционирования ИС код адреса первой пустой ячейки массива с выхода регистра 8 сравнивается схемой сравнения 12 с текущим значени% ем содержимого счетчика 7, и при равенстве и кодов со схемы сравнении выдается сигнал, под действием которого триггер управления переходит в единичное состояние, что вызьтает формирование импульса разрешения записи информации в блок 5 и запуск в ЭВМ по выходу 13 программы записи.

Необходимое число повторных циклов функционирования для полного восстановления пропущенной информации определяется общим количеством незаполненных ячеек в отведенном для записи массиве ОЗУ.

Таким образом, предложенное устройство способно регистрировать повторяющиеся процессы функционирования ИС, превыпающие по быстродействию применяемую ЭВМ, так как максимально допустимая скорость этих процессов не определяется быстродействием машины, а ограничена только разрешающей способностью данного устройства, которая повышается как минимальное время между моментами поступления двух соседних слов, при котором устройство еще способно различить их как два самостоятельных слова. В данном устройстве эта характеристика складывается из времени переходного процесса в счетчике номера состояний и времени записи информации в регистры.

Формула изобретения Устройство для сбора дискретной информации, содержащее регистр адреса, выход которого является выходом адреса устройства, триг5 гер управления, формирователь импульсов, коммутатор, схему сравнения и память, о тличающееся тем, что, с целью повыш ения достоверности работы устройства, в него введены группа формирователей импуль0 сов, элемент ШШ, счетчик, элемент И и элемент задержки, причем выход элемента ИЛИ соединен со входом счетчика и первым входом коммутатора, а каждый вход через соответствующий формирователь импульсов группы -

5 с соответствующим входом первой группы входов устройства, второй и третий входы коммутатора подключены соответственно ко входу переключения режима работы устройства и выходу схемы сравнения, первый вход которой соединен с выходом счетчика и пер0вым входом элемента И, а второй - с выходом регистра адреса, первый и второй входы которого соединены соответственно со входом адреса устройства и выходом элемента И, вторым входом подключенного ко входу памя5ти через последовательно соединенные формирователь импульсов и элемент задержки к выходу триггера управления и выходу управления устройства, входы триггера управления соединены соответственно со входом обнуле0ния устройства и выходом коммутатора, первая и вторая группы входов и группа выходов памяти соединены соответственно с первой и второй группами входов и группой выходов устройства.

5Источники информации,

принятые во внимание при экспертизе 1. Каган Б. М. и др. Система связи УВМ с объекталш управления в АСУТП, М., Советское радио 1978.

& 2. Авторское свидетельство СССР по заявке № 2709043/18-24, кл. G 06 F 3/04, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Устройство для сопряжения электронных вычислительных машин | 1984 |

|

SU1257653A2 |

| Устройство для сопряжения двух электронных вычислительных машин (эвм) | 1984 |

|

SU1187172A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

Авторы

Даты

1981-11-15—Публикация

1980-03-20—Подача