Изобретение относится к вычислительной технике и может быть использовано в качестве устройства управле ния ЭВМ. Известно микропрограммное управля ющее устройство, содержащее два запоминающих блока, регистры адресов, элементы И Cl Недостатком устройства является низкая функциональная надежность, Наиболее близким к изобретению по технической сущности является микропрограммное устройство управления, содержащее два блока памяти, два регистра адреса, два элемента ИЛИ, два элемента И, коммутатор и R-S-триггер нулевой выход которого соединен с первым входом первого элемента И, выход первого регистра адреса соединен с первым входом первого блока памяти, второй вход которого соединен с выходом второго элемента И, первый вход которого является тактовым входом устройства, выход второ го регистра адреса соединен с первым входом второго блока памяти . Однако данному устройству присуща низкая функциональная надежность. Цель изобретения - повышение функциональной надежности устройства. Эта цель достигается тем, что в микропрограммное устройство управления дополнительно введены третий, четвертый и пятый элементы И, третий и четвертый элементы ИЛИ, блок контроля и блок элементов И, выход которого соединен с первыми входами первого и второго элементов ИЛИ, выходы которых соединены со входами соответственно первого и второго регистров адреса, первый и второй выходы коммутатора соединены со вторыми входами соответственно первого и второго элементов ИЛИ, третий выход коммутатора соединен с первым входом блока элементов И, второй вход которого является входом логических условий устройства, выходы логических условий, меток ветвления и адреса первого блока памяти и нулевой выход R-S-триггера соединены с первой группой входов коммутатора, выходы логических условий, меток ветвления и адреса второго блока памяти и единичный выход R-S-триггера соединены со второй группой входов коммутатора, выходы микроопераций

первого и второго блоков памяти соединены с первыми входами соответственно третьего и четвертого элементов И, выходы которых соединены соответственно с первыми и вторыми входами третьего элемента ИЛИ, выход которого.является выходом устройстваi выход второго элемента И соединен со вторым входом второго блока памяти и со счетным входомR-S-триггера,единичный выход которого соединен со вторым входом четвертого и входом пятого элементов И, второй вход третьего элемента И соединен с нулевым выходом Я-З-триггера, выходы микроопераций, логических условий, меток ветвления и адреса первого блока памяти соединены с группой входов пятого элемента И, выходы микроопераций, логических условий, меток ветвления и адреса второго блока памяти соединены с группой входов Первого -элемента И, выходы первого и пятого элементов И соединены соответственно с первым и вторым входами четвертого элемента ИЛИ,выход которого соединен со входом блока контроля, выход которого соединен со вторым входом второго элемента И,

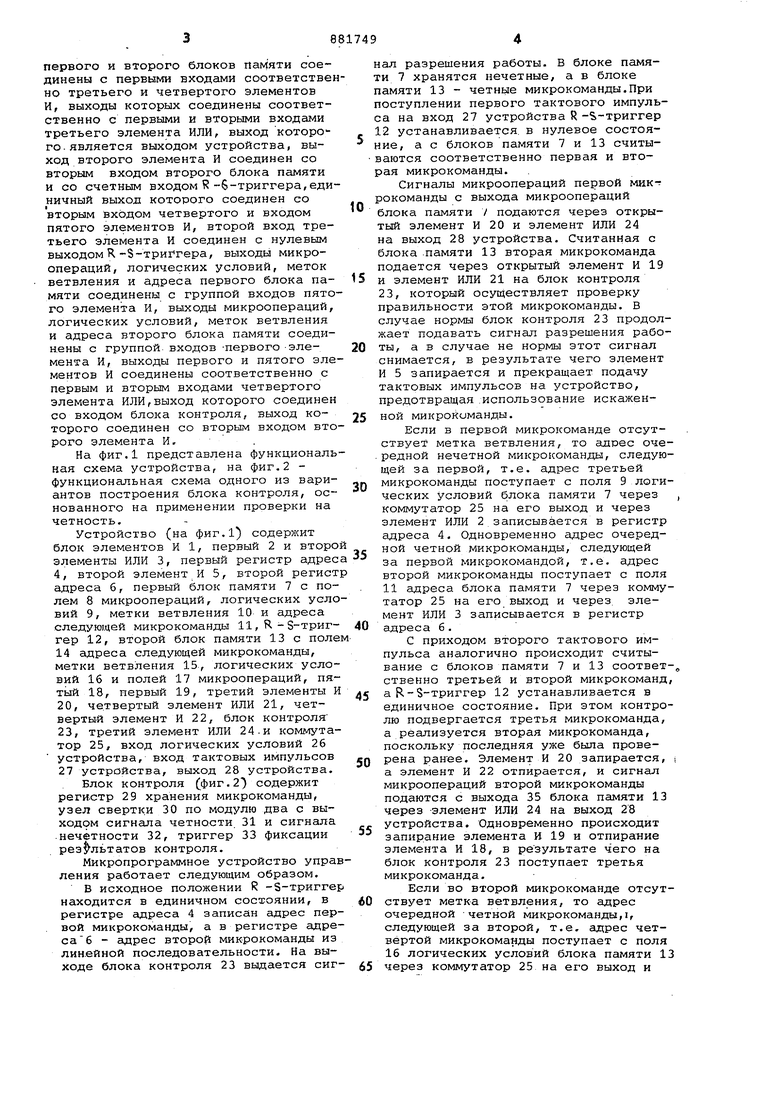

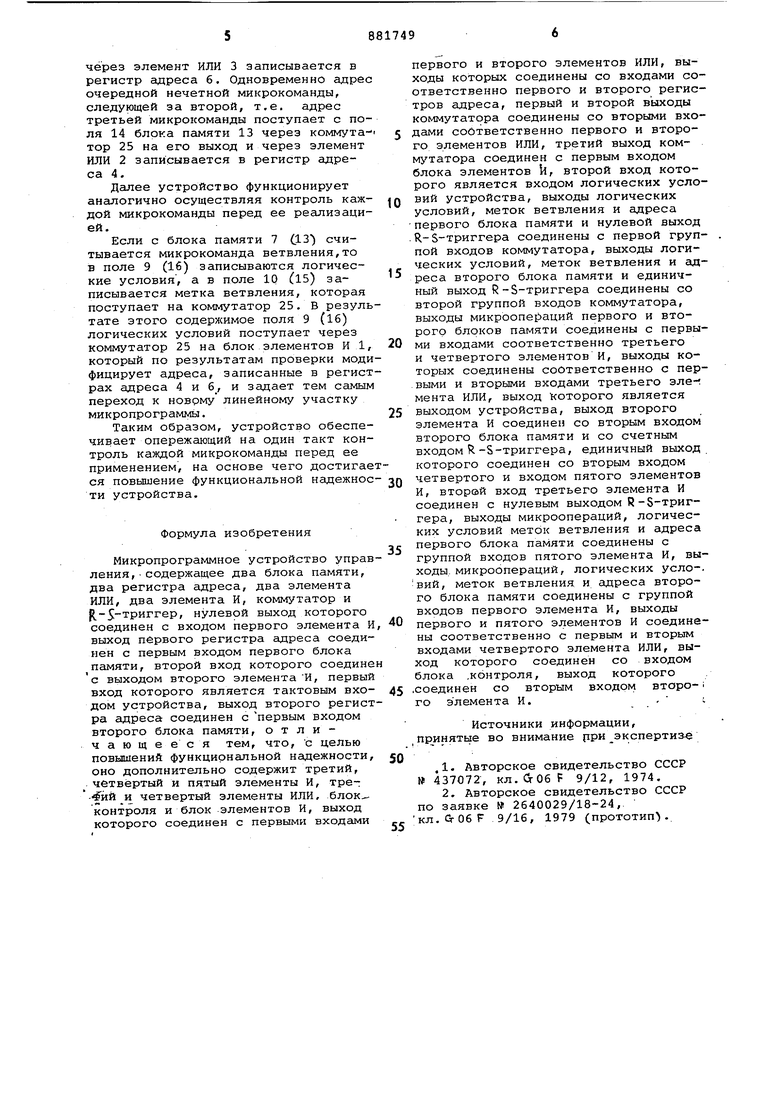

На фиг.1 представлена функциональная схема устройства, на фиг.2 функциональная схема одного из вариантов построения блока контроля, основанного на применении проверки на четность.

Устройство (на фиг.1) содержит блок элементов И 1, первый 2 и второ элементы ИЛИ 3, первый регистр адрес 4, второй элемент И 5, второй регист адреса б, первый блок памяти 7 с полем 8 микроопераций, логических условий 9, метки ветвления 10 и адреса следующей микрокоманды 11,Я-3-триггер 12, второй блок памяти 13 с поле 14 адреса следующей микрокоманды, метки ветвления 15, логических условий 16 и полей 17 микроопераций, пятый 18, первый 19, третий элементы И 20, четвертый элемент ИЛИ 21, четвертый элемент И 22, блок контроля 23, третий элемент ИЛИ 24.и коммутатор 25, вход логических условий 26 устройства, вход тактовых импульсов 27 устройства, вьлход 28 устройства.

Блок контроля (фиг. 2) содержит регистр 29 хранения микрокоманды, узел свертки 30 по модулю два с выходом сигнала четности 31 и сигнала нечетности 32, триггер 33 фиксации рез льтатов контроля.

Микропрограммное устройство управления работает следующим образом.

В исходное положении R -S-триггер находится в единичном состоянии, в регистре адреса 4 записан адрес первой микрокоманды, а в регистре адреса б - адрес второй микрокоманды из лин.ейной последовательности. На выходе блока контроля 23 выдается сигнал разрешения работы. В блоке памяти 7 хранятся нечетные, а в блоке памяти 13 - четные микрокоманды.При поступлении первого тактового импульса на вход 27 устройства R-S-триггер 12 устанавливается, в нулевое состояние, ас блоков памяти 7 и 13 считываются соответственно первая и вторая микрокоманды.

Сигналы микроопераций первой мик- рокоманды с выхода микроопераций блока памяти / подаются через открытый элемент И 20 и элемент ИЛИ 24 на выход 28 устройства. Считанная с блока .памяти 13 вторая микрокоманда подается через открытый элемент И 19 и элемент ИЛИ 21 на блок контроля 23, который осуществляет проверку правильности этой микрокоманды. В случае нормы блок контроля 23 продолжает подавать сигнал разрешения работы, а в случае не нормы этот сигнал снимается, в результате чего элемент И 5 запирается и прекращает подачу тактовых импульсов на устройство, предотвращая .использование искаженной микрокоманды.

Если в первой микрокоманде отсутствует метка ветвления, то алрес оче.редной нечетной микрокоманды, следующей за первой, т.е. адрес третьей микрокоманды поступает с поля 9 логических УСЛОВИЙ блока памяти 7 через коммутатор 25 на его выход и через элемент ИЛИ 2 записывается в регистр адреса 4. Одновременно адрес очередной четной микрокоманды, следующей за первой микрокомандой, т.е. адрес второй микрокоманды поступает с поля 11 адреса блока памяти 7 через коммутатор 25 на его выход и через элемент ИЛИ 3 записывается в регистр адреса 6.

С приходом второго тактового импульса аналогично происходит считывание с блоков памяти 7 и 13 соответ ственно третьей и второй микрокоманд aR-S-триггер 12 устанавливается в единичное состояние. При этом контролю подвергается третья микрокоманда, а реализуется вторая микрокоманда, поскольку последняя уже была проверена ранее. Элемент И 20 запирается, а элемент И 22 отпирается, и сигнал микроопераций второй микрокоманды подаются с выхода 35 блока памяти 13 через элемент ИЛИ 24 на выход 28 устройства. Одновременно происходит запирание элемента И 19 и отпирание элемента И 18, в результате чего на блок контроля 23 поступает третья микрокоманда.

Если во второй микрокоманде отсутствует метка ветвления, то адрес очередной -четной микрокоманды,, следующей за второй, т.е. адрес четвёртой микрокоманды поступает с поля 16 логических условий блока памяти 1 через коммутатор 25 на его выход и через элемент ИЛИ 3 записывается в регистр адреса 6. Одновременно адре очередной нечетной микрокоманды, следующей за второй, т.е. адрес третьей микрокоманды поступает с по ля 14 блока памяти 13 через коммута тор 25 на его выход и через элемент ИЛИ 2 записывается в регистр адреса 4, Далее устройство функционирует аналогично осуществляя контроль каж дои микрокоманды перед ее реализаци ей. Если с блока памяти 7 О-З) считывается микрокоманда ветвления,то в поле 9 (16) записываются логические условия , а в поле 10 15) записывается метка ветвления, которая поступает на коммутатор 25. В резул тате этого содерхшмое поля 9 (16) логических условий поступает через коммутатор 25 на блок элементов И 1 который по результатам проверки мод фицирует адреса, записанные в регист рах адреса 4 и 6, и задает тем самым переход к новрму линейному участку микропрограммы. Таким образом, устройство обеспечивает опережающий на один такт контроль каждой микрокоманды перед ее применением, на основе чего достигае ся повышение функциональной надежное ти устройства. Формула изобретения Микропрограммное устройство управ ления, содержащее два блока памяти, два регистра адреса, два элемента ИЛИ, два элемента И, коммутатор и Р.-5 триггер, нулевой выход которого соединен с входом первого элемента И выход первого регистра адреса соединен с первым входом первого блока памяти, второй вход которого соедине с выходом второго элемента И, первый вход которого является тактовым входом устройства, выход второго регист ра адреса соединен с первым входом второго блока памяти, отличающееся тем, что, с целью повышений функциональной надежности, оно дополнительно содержит третий, четвёртый и пятый элементы И, тре- йй и четвертый элементы ИЛИ, блок контроля и блок элементов И, выход которого соединен с первыми входами первого и второго элементов ИЛИ, выходы которых соединены со входами соответственно первого и второго регистров адреса, первый и второй выходы коммутатора соединены со вторыми входами соответственно первого и второго элементов ИЛИ, третий выход коммутатора соединен с первым входом блока элементов Vl, второй вход которого является входом логических условий устройства, выходы логических условий, меток ветвления и адреса первого блока памяти и нулевой выход R-S-триггера соединены с первой группой входов коммутатора, выходы логических условий, меток ветвления и гщреса второго блока памяти и единичный выход R-S-триггера соединены со второй группой входов коммутатора, выходы микроопе1 аций первого и второго блоков памяти соединены с первыми входами соответственно третьего и четвертого элементов И, выходы которых соединены соответственно с первыми и вторыми входами третьего эле-f мента ИЛИ, выход Которого является выходом устройства, выход второго элемента И соединен со вторым входом второго блока памяти и со счетным входом i-S-триггера, единичный выход которого соединен со вторым входом четвертого и входом пятого элементов И, вторсай вход третьего элемента И соединен с нулевым выходом R-S-триггера, выходы микроопераций, логических условий меток ветвления и адреса первого блока памяти соединены с группой входов пятого элемента И, выходы микроопераций, логических уело-. ВИЙ, меток ветвления и адреса второго блока памяти соединены с группой входов первого элемента И, выходы первого и пятого элементов И соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выход которого соединен со входом блока .контроля, выход которого соединен со вторым входом второ- го элемента И.. i Источники информации, Принятые во внимание рри экспертиэе ,1. Авторское свидетельство СССР № 437072, кл.СтОбР 9/12, 1974. 2. Авторское свидетельство СССР по заявке № 2640029/18-24, кл.СтОбР 9/16, 1979 (прототип

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1100625A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1183964A1 |

| Микропрограммное устройство управления с контролем | 1980 |

|

SU920727A1 |

| Микропрограммное устройство управления с контролем | 1982 |

|

SU1038944A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

Авторы

Даты

1981-11-15—Публикация

1979-12-26—Подача