1

ti.

Л и л 14 25 26 i-f t 11 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Генератор функциональных зависимостей | 1983 |

|

SU1130853A1 |

| Ассоциативное запоминающее устройство | 1982 |

|

SU1043750A1 |

| Генератор последовательности импульсов | 1983 |

|

SU1231583A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1211811A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1985 |

|

SU1288751A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

Изобретение относится к вычислительной технике, в частности к эа- поминаьэщим устройствам, и может быть использовано в запоминающих устройствах микроэвм или микрокалькуляторов. Целью изобретения является увеличение информационной емкости и упроще

ОС

со со сх го

со

ние устройства. Устройство содержит накопитель , два регистра 9, 10 поразрядного сдвига, первый регистр 2,числа, входы М которого являются информационными входами устройства, со второго по четвертый регистры 3, 4, 5 числа, регистр 6 адреса, коммутатор 7, блок 8 управления. Каждое число записывается в накопитель 1. из регистра 2 в обратном коде, считывается на регистр 4, затем записьша- ется в прямом коде и снова считывается на регистр 4. Регистр Д, выполненный из счетных триггеров, выполняет поразрядное суммирование по модулю два прямого и обратного кодов считанного числа и на его выходах формируется код наличия ошибки, содержащий нуль в разряде, соответству1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано в запоминающих устройствах микроэвм или микрокалькуляторов

Цель изобретения - увеличение информационной емкости и упрощение устройства.

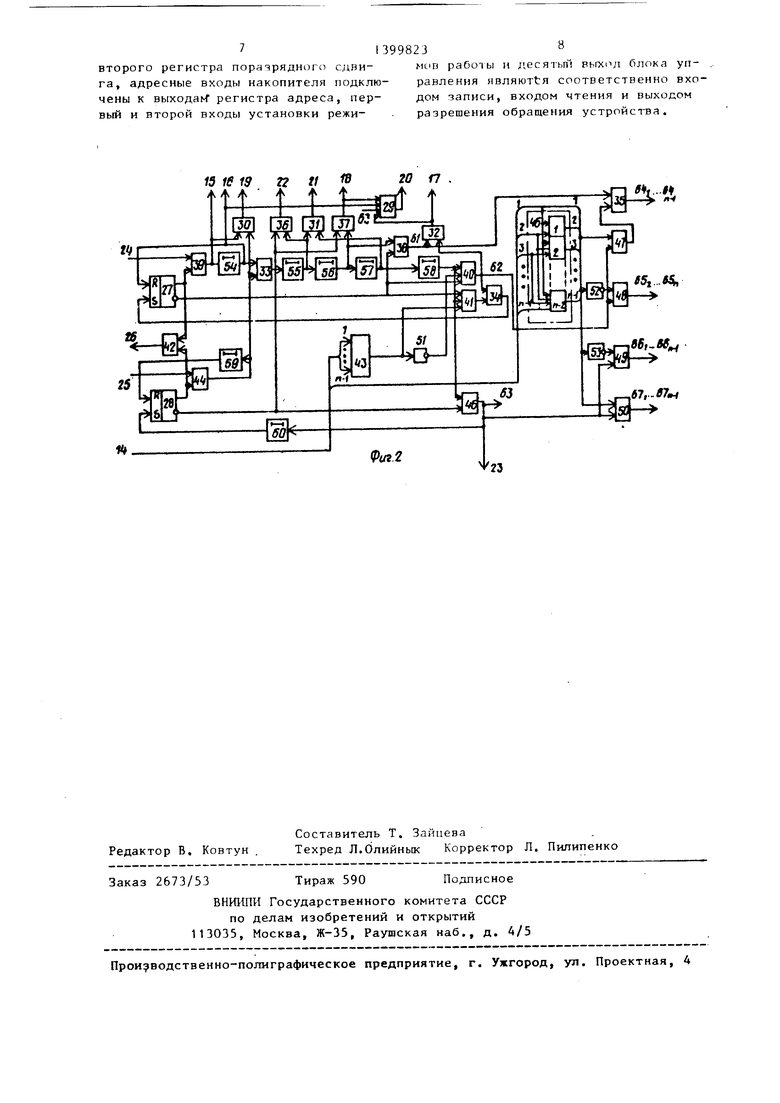

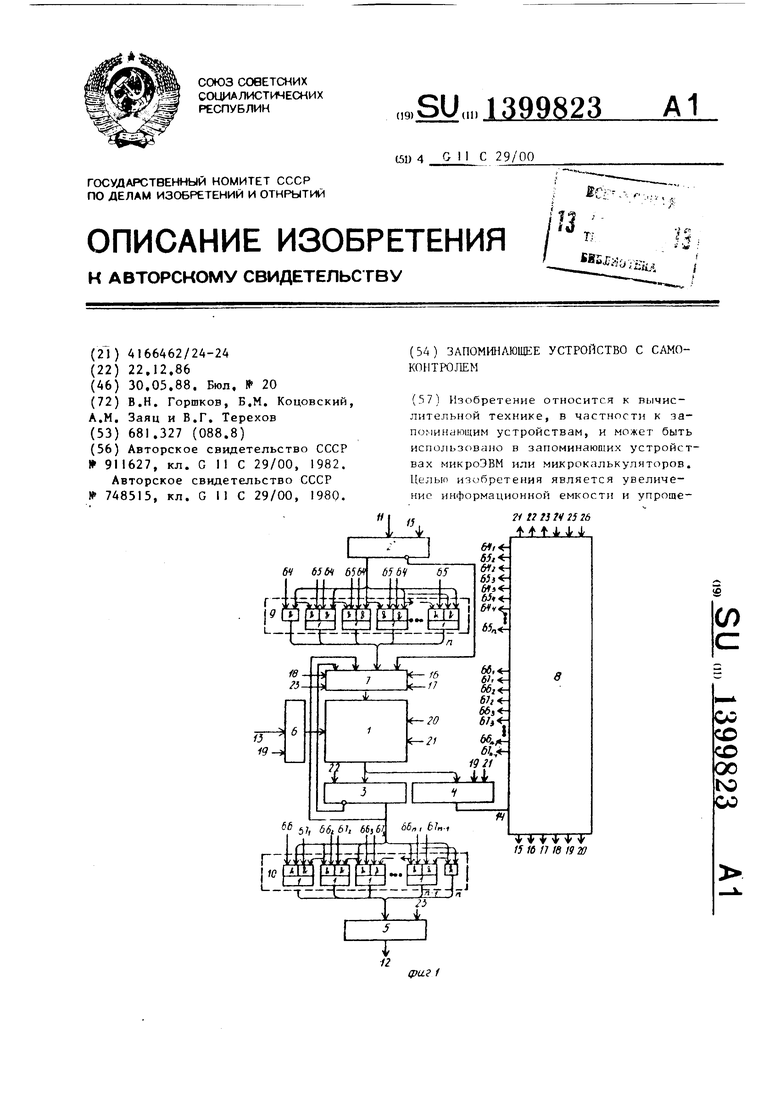

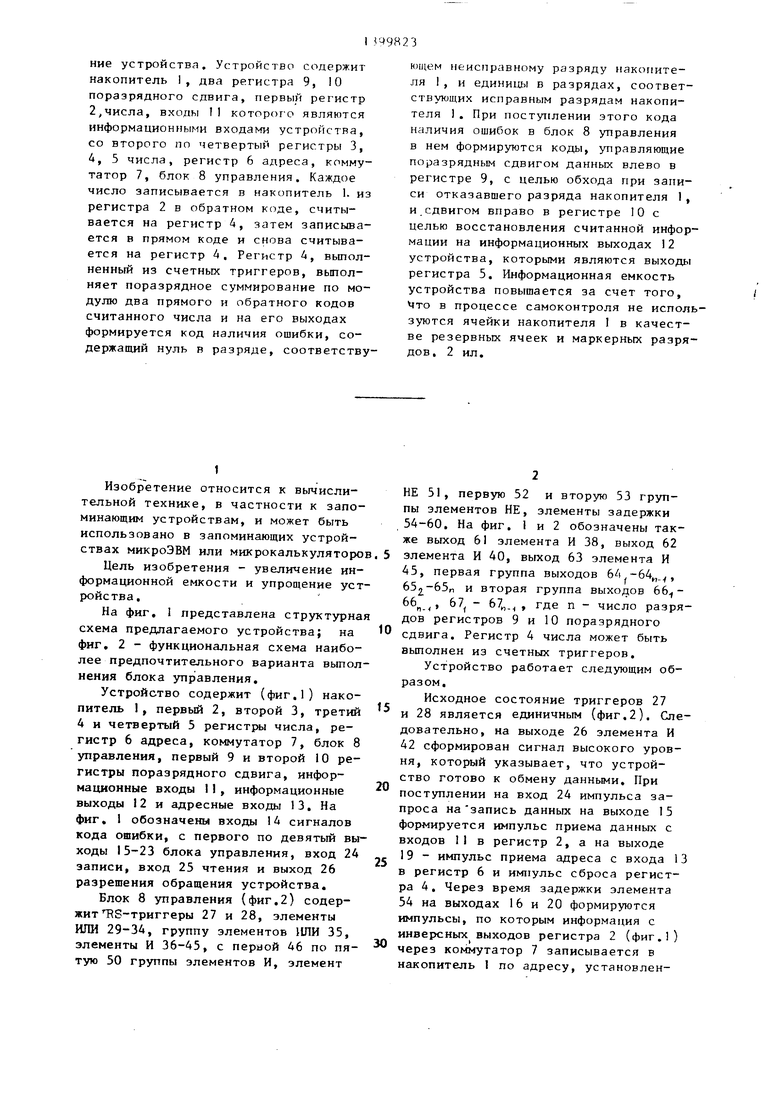

На фиг, 1 представлена структурная схема предлагаемого устройства; на фиг, 2 - функциональная схема наиболее предпочтительного варианта выполнения блока управления.

Устройство содержит (фиг,1) накопитель 1, первый 2, второй 3, третий 4 и четвертый 5 регистры числа, регистр 6 адреса, коммутатор 7, блок 8 управления, первый 9 и второй 10 регистры поразрядного сдвига, информационные входы 1I, информационные выходы 12 и адресные входы 13, На фиг, 1 обозначены входы 14 сигналов кода ошибки, с первого по девятый выходы 15-23 блока управления, вход 24 эаписи, вход 25 чтения и выход 26 разрешения обращения устройства.

Блок 8 управления (фиг,2) содержит Т Б-триггеры 27 и 28, элементы ИЛИ 29-34, группу элементов 1ШИ 35, элементы И 36-45, с периой 46 по пя- тую 50 группы элементов И, элемент

ющем неисправному разряду накопителя 1, и едини1Д)1 в разрядах, соответствующих исправным разрядам накопителя 1. При поступлении этого кода наличия ошибок в блок 8 управления в нем формируются коды, управляющие поразрядным сдвигом данных влево в регистре 9, с целью обхода при записи отказавшего разряда накопителя 1, и сдвигом вправо в регистре 10 с целью восстановления считанной информации на информационных выходах 12

устройства, которыми являются ВЫХОДЬ

регистра 5. Информационная емкость устройства повышается за счет того, Что в процессе самоконтроля не используются ячейки накопителя I в качестве резервных ячеек и маркерных разрядов, 2 ил.

НЕ 51, первую 52 и вторую 53 группы элементов НЕ, элементы задержки 54-60, На фиг, 1 и 2 обозначены также выход 61 элемента И 38, выход 62 элемента И 40, выход 63 элемента И 45, первая группа выходов 6Д,-64„, 652-65п и вторая группа выхо(ов , 67 - 67,, , где п - число разрядов регистров 9 и 10 поразрядного сдвига. Регистр 4 числа может быть вьшолнен из счетных триггеров.

Устройство работает следующим образом.

Исходное состояние триггеров 27 и 28 является единичным (фиг,2). Следовательно, на выходе 26 элемента И 42 сформирован сигнал высокого уровня, который указывает, что устройство готово к обмену данными. При поступлении на вход 24 импульса запроса на запись данных на выходе 15 формируется импульс приема данных с входов 11 в регистр 2, а на выходе 19 - импульс приема адреса с входа 13 в регистр 6 и импульс сброса регистра 4, Через время задержки элемента 54 на выходах 16 и 20 формируются импульсы, по которым информация с ииверюных выходов регистра 2 (фиг,1) через коммутатор 7 записывается в накопитель 1 по адресу, установленному в регистре 6. Импульс с выхода 16 также переключает триггер 27 в нулевое состояние, тем самьт на выходе 26 устанавливается низкий уровень сигнала, означаюший запрет на очередное обращение к устройству.

Через время задержки элемента 55 на выходе 21 формируется импульс, по которому записанная информация в обратном коде считывается из накопителя 1 и записывается в регистр 4. Через время задержки элемента 56 на выходе 16 формируется единичньш импульс, который поступает на выходы i7, 20 и на входы элементов ИЛИ 35 и вырабатывает управляющий код П С П С FIj

С...С, 101010,...О, причем сигналы на выходах 64,-64. равны единице, а сигналы С на

15 значе ние п-го разряда теряется, т.е. точность записанного информационного кода ухудшается на 2 (для чисел с фиксированной запятой). Импульс с выхода 62 элемента М 40 также поступавыходах 0 ет через элемент ИЛИ 34 на вход триг- нулю. По этим импульсам с прямых вы- 2 информация без измеходов регистра нений передается через регистр 9, коммутатор 7 и записывается в накопитель 1 . Через время зад°ержки элемента 56 на выходе 21 формируется импульс, по которому записанная информация в прямом коде считывается из накопителя 1 и записывается в регистр 4, на выходе которого формируется сумма по модулю два считанных обратного и прямого кодов. Если в данной ячейке накопителя I отказавших разрядов -нет, то сигналы на всех разрядах регистра 4 числа равны единице, т,е, О X, Х Xj Х ,.,,,Х, 1 1 11,.,., . В этом случае на выходе элемента И 43 формируется сигнал высокого уровня. Через время задержки элемента 58 открьшается элемент И 41, с выхода которого управляющий импульс через элемент ИЛИ 34 поступает на вход установки триггера 27 и переключает триггер в единичное состояние. На вы- .ходе 26 элемента И 42 формируется сигнал высокого уровня, который разрешает обращение к устройству для очередного обмена данными.

Если в данной я ейке накопителя 1 отказал один разряд, например третий, то, соответственно сигнал на выходе третьего разряда регистра 4 равен нулю, т,е, X Х., Xj Х , ,, ,Х 1 1 01 ,, , ,,1 , Тогда через время задержки элемента 58 открывается элемент И 40 и на его выходе 62 формируется импульс, по которому нп вьгх(-)дах 17 и 20 появляются управляю1лие имтгульсы, а на выходах

25

гера 27, перключает его в единичное состояние и на выходе 26 элемента И 42 формируется сигнал высокого уровня, который разрешает обращение к устройству для очередного обмена данными , I

При поступлении на вход 25 импульса запроса на чтение данных на выхо30 де 19 формируется импульс, по которому происходит прием адреса с входов 13 в регистр 6 и гащение содержимого регистра 4, Через время задержки элемента 59, меньшее времени заog держки элемента 56, импульс поступает на вход сброса триггера 28 и переключает его в нулевое состояние, тем самым на выходе 26 устанавливается низкий уровень сигнала, что за40 прещает поступление очередного запроса на обращение к устройству. Через время задержки элемента 55 на выходах 21 и 22 формируются импульсы, 10 которым происходит считывание пря45 мого кода информации из накопителя 1 в регистры 3 и 4, Через время задержки элемента 56 на выходах 18 и 20 формируются импульсы, по которым ин- (}юрмация инверсных выходов регистра

5Q 3 через коммутатор 7 записьгоается в данную ячейку накопителя I, Через время задержки элемента 57 на выходе 21 формируется импульс, по которому происходит считывание обратного кода из накопителя 1 и запись его в регистр 4, на выходе которого формируется сумма по модулю два прочитанных прямого и обратного кодов информации из накопителя 1, Через время

55

65, - .65

n-l

66,,

формируется код

101 001 О,. . ,, 1 которыГ) у11равл 1ет сдвигом в регистре 2, В эт(.)м под воздействием сформированного

упрапляющего кода на выходах 65-66 ,

информация с прямых выходов регистра

2через регистр 9 и коммутатор 7 записывается в накопитель I, Причем первые два разряда информации пере даются без изменений, а разряды с третьего по п сдвигаются вправо на один разряд в регистре 9. Тем самым осутлествляется обход отказавшего разряда ячеГжи накопителя , При этом

значе ние п-го разряда теряется, т.е. точность записанного информационного кода ухудшается на 2 (для чисел с фиксированной запятой). Импульс с выхода 62 элемента М 40 также поступа 0 ет через элемент ИЛИ 34 на вход триг-

25

гера 27, перключает его в единичное состояние и на выходе 26 элемента И 42 формируется сигнал высокого уровня, который разрешает обращение к устройству для очередного обмена данными , I

При поступлении на вход 25 импульса запроса на чтение данных на выхо30 де 19 формируется импульс, по которому происходит прием адреса с входов 13 в регистр 6 и гащение содержимого регистра 4, Через время задержки элемента 59, меньшее времени заog держки элемента 56, импульс поступает на вход сброса триггера 28 и переключает его в нулевое состояние, тем самым на выходе 26 устанавливается низкий уровень сигнала, что за40 прещает поступление очередного запроса на обращение к устройству. Через время задержки элемента 55 на выходах 21 и 22 формируются импульсы, 10 которым происходит считывание пря45 мого кода информации из накопителя 1 в регистры 3 и 4, Через время задержки элемента 56 на выходах 18 и 20 формируются импульсы, по которым ин- (}юрмация инверсных выходов регистра

5Q 3 через коммутатор 7 записьгоается в данную ячейку накопителя I, Через время задержки элемента 57 на выходе 21 формируется импульс, по которому происходит считывание обратного кода из накопителя 1 и запись его в регистр 4, на выходе которого формируется сумма по модулю два прочитанных прямого и обратного кодов информации из накопителя 1, Через время

55

задержки элемента 58 на выходе 63 гЗлемента И 45 формируется импульс, который поступает на выход 23 блока 8 и разрешает выдачу на выходы 66, 67| 67 кода, управляющего сдвигом в регистре 10. Причем, в случае отсутствия отказавших разрядов в данной ячейке накопителя 1, т.е. если содержимое регистра 4 Х . ., ,...I , то управляющий йдви гом код равен ,..., 10101 О,...О и информация с прямых выходов регистра 3 через регистр 10 без изменений передается в ре- гистр 5 и на выходы 12 устройства. Если обнаружен отказавший разряд в ячейке накопителя 1, например третий то управляющий сдвигом код равен

njc;n c ii c,...,n с;;.101001,...pi

и информация через регистр 10 в регистр 5 передается без изменений, например первый и второй разряды, а с четвертого по п разряды сдвигаются на один разряд влево. При этом зна- чение п-разряда принудительно устанавливается в о.

Импульс с выхода 63 также поступает через элемент ИЛИ 29 на выход 20 Под воздействием импульсов на вы- ходах 20 и 23 информация с прямых выходов регистра 3 через коммутатор 7 записывается в накопитель 1, т.е. производится восстановление прямого кода в ячейке накопителя 1.

Через время задержки элемента 60 импульс с выхода 63 элемента И 45 поступает на вход триггера 28 и переключает его в единичное состояние, при этом на выходе 26 формируется сигнал высокого уровня, т,е. устройство готово обслуживать очередной запрос на обращение к нему,,

Следует отметить, что в предлагаемом устройстве не используются в про- цессе самоконтроля ячейки накопителя 1 в качестве резервных ячеек, а также дополнительные маркерные разряды, что позволяет увеличить информационную емкость устройства,

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее накопитель, с первого по четвертый регистры числа, ре- гистр адреса, блок управления и коммутатор, информационные входа первой группы которого подключены к инверсным выходам первого регистра числа,

разрядные входы которого являются информационными входами устройства, адресными входами которого являются разрядные входы регистра адреса, причем выходы накопителя соединены с разряднь(ми входами второго регистра числа, выходы с первого по четвертый блока управления подключены соответственно к управляющему входу первого регистра числа, к первому, второму и третьему управляющим входам коммутатора, пятый выход блока управления подключен к входу сброса третьего регистра числа и входу управления регистра адреса, шестой выход блока управления соединен с входом записи накопителя, выход чтения которого и вход разрешения приема информации третьего регистра числа соединены с седьмым выходом блока управления, восьмой выход которого подключен к входу управления второго регистра числа, отличающе еся тем, что, с целью увеличения информационной емкости и упрощения устройства, в него введены первый и второй регистры поразрядного сдвига, причем информационные входы и выходы первого регистра поразрядного сдвига подключены соответственно к прямым выходам первого регистра числа и к информационным входам второй группы коммутатора, выходы которого соединены с информационными входами накопителя, информационные выходы которого подключены к информационным входам третьего регистра числа, выходы которого подключены к входам сигналов кода ошибки блока управления, девятый выход которого соединен с управляющим входом четвертого регистра числа и четвертым управляющим входом коммутатора, информационные входы третьей и четвертой групп которого подключены соответственно к прямым и инверсным выходам второго регистра числа, прямые выходы которого подключены к информационным входам второго регистра поразрядного сдвига, выходы которого соединены с информационными входами четвертого регистра .числа, выходы которого являются информационными выходами устройства, входы управления сдвигом первого регистра поразрядного сдвига подключены к выходам первой группы блока управления, выходы втЬрой группы которого соединены с входами управления сдвигом

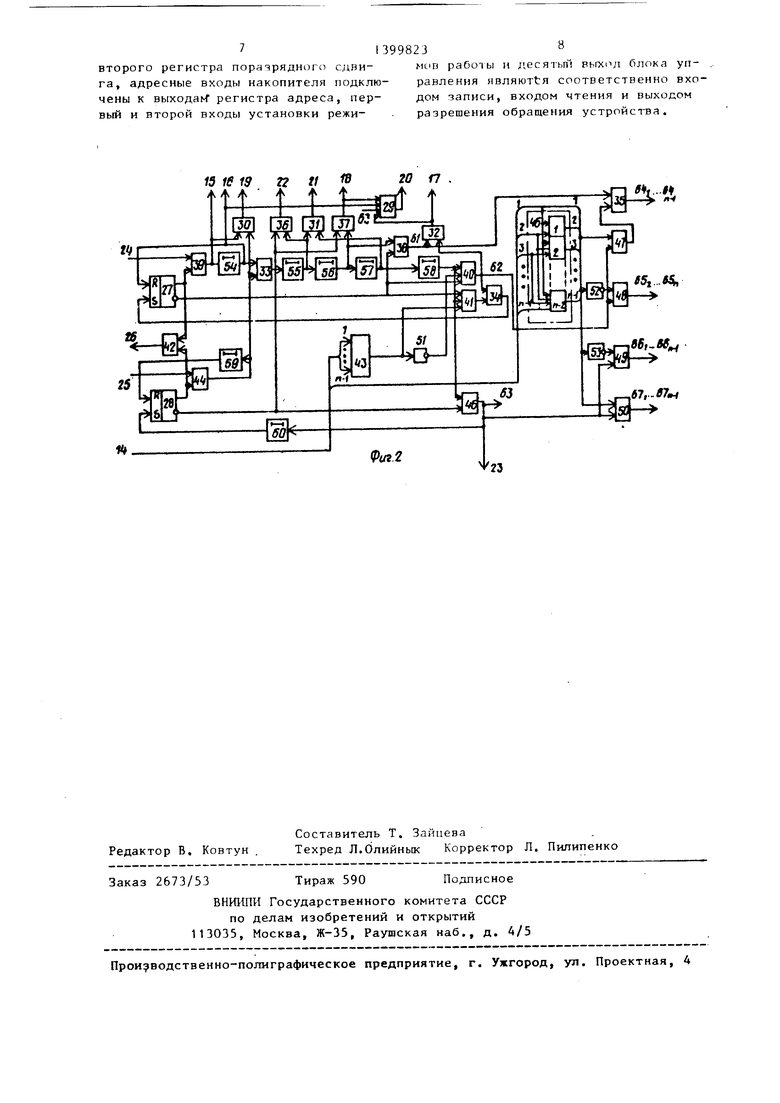

га, адресные входы накопителя подключены к выходаг регистра адреса, первый и второй входы установки режи15 ie 19 гг ti 1В

равления являютtя соответственно входом записи, входом чтения и выходом разрешения обращения устройства.

20 Г7 .

I

| Запоминающее устройство с самоконтролем | 1980 |

|

SU911627A2 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU748515A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-22—Подача