Изобретение относится к вычиспитепь,ной технике и дискретной автоматике н может быть использовано при построении цифровой аппаратуры повышенной надежности. Известен модуль двоичного счетчш а, содержащий генератор тестовых сигналов и четыре разряда, каждый из которых состоит из триггера, выход которого соединен с первым Ёходом элемента И, вькод которого подключен к первому вхо ду триггера последующего разряда 3J Недостатком известного устройства является отсутствие проверки контропьных элементов на отказ Ложная едкница, т. е. на тот отказ, при котором соответствующие логические нули не могут быть выданы и вместо них выдаются единицы. Цепь изобретения - повьшение надежности работы устройства. Для достижения указанной цели в модуль двоичного счетчика, содержащий генератор тестовых сигналов и четыре разряда, каждый из которых состоит из триггера, выход которого соединен с первым входом элемента И, вьхход которого подключен к первому входу триггера последующего разряда, введены дешифратор, элементы совпадения, элементы ИЛИ и НЕ, а в каждый разряд - дополнитепь- . ные элементы И и элементы И-НЕ, при этом В каждом разряде ко второму входу триггера подключены последовательно , два допопниатепьньк элемента И, к третьему входу триггера - выход третьего дополнительного элемента И, ко второму входу элемента И - выход элемента И-НЕ, а первые входь второго и третьего дополнительных элементов И и эпемента И-НЕ объединены, при этом два первых выхода генератора тестовых сИ1 налов подключены ко входам дешифратора, третий выход - ко второму, входу третьего дополнительного элеме1 та И каждого разряда непосредственно и тсо второму входу первого дополнительного элемента И каждого разряда через

первый элемент НЕ, четвертый выход ко второму входу элемента И-НЕ каждого разряда непосредственно и ко второму входу второго дополнительного элемента И каждого разряда через второй элемент НЕ, первый вьссод дешифратора соединен со входом первого разряда, второй выход дешифратора - со входом второго разряда и с первым входом первого элемента совпадения, третий выход дешифратора - с первым входом второго элемента совпадения и- с первым входом первого элемента ИЛИ, выход которого подключен ко входу третьего разряда, а четвертьй выход дешифратора - с первым входом второго элемента ИЛИ, второй вход которого подключен к выходу второго элемента совпадения, третий вход - к выходу первого элемента совпадения и jto второму входу первого элемента ИЛИ, а выход к входу четвертого разряда, причем вторые входы элементов совпадения соединены с пятым выходом генератора тестовых сигналов.

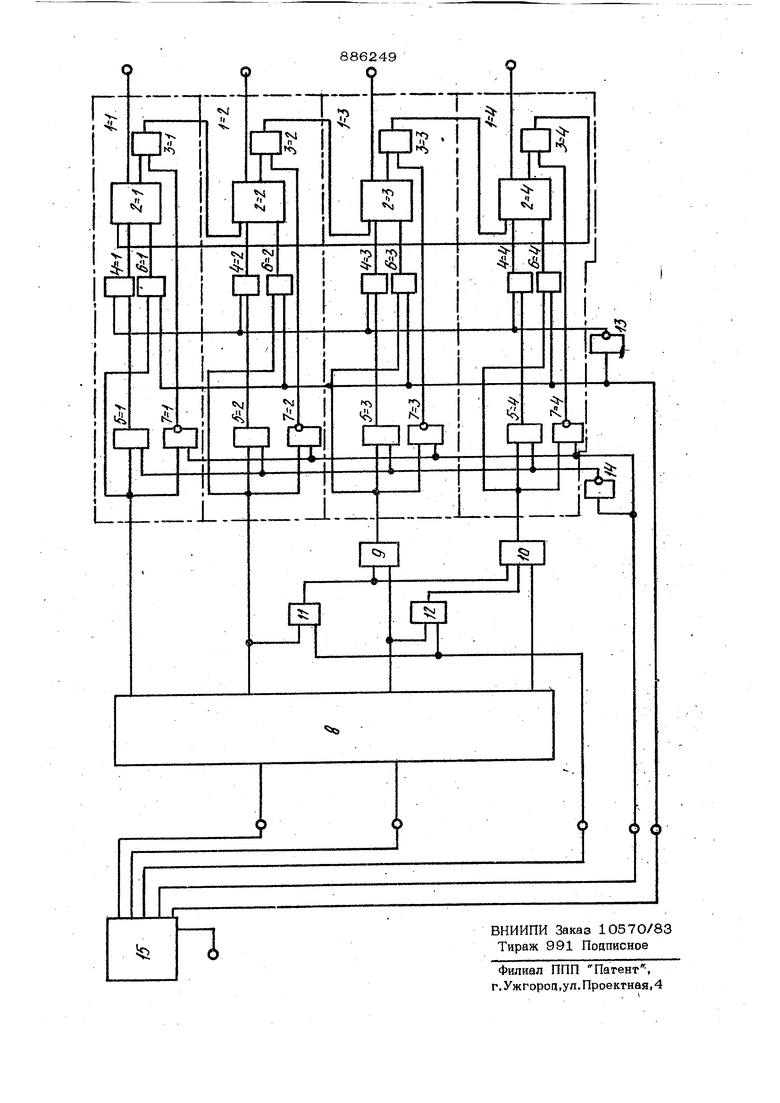

На чертеже представлена структурная электрическая схема модуля двоичного счетчика.

Устройство содержит разряды 1-1 1-4 модуля двоичного счетчика, которые состоят из триггеров 2-1-2М, элементовИ 3--- 1-3-4, дополнительных элементов И 4-1 - 4-4, 5-1 - , 6 и элементов И-НЕ 7 1 , 7 4, дешифратор 8, элементы ИЛИ 9 и 10, элементы 11 и 12 совпадения и элементы НЕ 13 и 14, генератор 15 тестовых сигналов.

Устройство работает спедующим образом.

Входная информация подается независимо в модуль. В режиме записи информации в модуле.производится разрью цепей переноса от младшего разряда к старшему. Разрьш цепи переноса в модуле между старшим и младшим разрядами 1 4 и 1 1 производится подачей cHorvнала с вьрсодов генератора 15 тестовых Сигналов, при этом с первого, второго, третьего и четвертого выходов дешифратора 8 вьшается вьссодная информация (О,0,О,i), а на первые входы элементов ИЛИ 9 и 10 поступает О, на второй вход элемента ИЛИ 9 поступает О на второй вход элемента ИЛИ 1О поступает О, а на третий вход элемента ИЛИ Ю поступает -1. Тогда с вьрсодов элементов ИЛИ 9 и 10 выдается

соответственно 0,1, с выходов элементов и 13 выдается соответгственно 0,1, при этом с выходов элементов И 5 1, И-НЕ 7 1,И 5 2, И-НЕ 7 2, И 5 3,И-НЕ 7 3,И 5 4, И-НЕ 7 4 выдается соответственно (О,1,0,1,0,1,О,О). Тем самым на вторые входы элементов И3 поступают сигналы соответственно (1,1, 1,0), -при этом рвется цепь переноса между триггерами 2 4 и 2 1 модуля двоичного счетчика.

Разрьш цепи переноса в модуле между старшим и младшим разрядами, которым соответствуют триггера 2 2 и , производится подачей сигнала с вьрсода генератора (0,i,O,i,6), при этом с первого, второго, третьего и четвертого вькодов дешифратора 8 выдает-Г ся информация (0,1,6,0), на первые входы элементов ИЛИ 9 и 10 поступает 1 Тогда с, вькодов элементов ИЛИ 9 и Ю выдается соответственно (О,0), с выходов элементов НЕ 14 и 13 выдается соответственно (0,1), при этом с выходов элементов И 5 1, И-НЕ 7 1, И 5 2, И-НЕ 7 2, И 5 3, И-НЕ 7 3,И 5 4, И-НЕ 7 4 выдается соответственно (0,1,0,0,0,1,0,1), Тем самым на вторые входы элементов 3 1-3 4 поступают сигналы соответственно (1,0,Ijl), при этом рвется цепь переноса между триггерами 2 2 и 2 3 модуля.

Разрыв цепи переноса в модуле между старшим и младшим разрядами, которым со отве3х;твуют триггера 2 3 и , производится подачей сигаала с

генератора 15 (1,0,0,1,0), при этом с первого, второго, третьего и четвертого ввкодов дешифратора 8 выдается информация (0,0,1,0), а на первые входь элементов ИЛИ 9 и 10 поступает О, на

вторые входы элементов ИЛИ 9 и Ю поступают соответственно 1,О, а на третий вход элеменаа ИЛИ 10 поступает О. При этом с выходов элементов ИЛИ 9 и 10 вьщается соответственно

(1,О), с выходов элементов НЕ 14 и 13 выдается соответственно (0,1), а с выходов элементов И 5 1, И-НЕ 7 1,И 5 2,И-НЕ 7 2,И 5 3, И-НЕ 7 3,И 5 4,И-НЕ 7 ..4 j bjДаются соответственно (0,1,0,1,0,0,0,1). Тем самым на вторые входы элементов 3 1-3 4 поступают сигналы соответственно (1,1,0,1), при этом рвется цепь переноса между триггерами ,2 и 2 4 модуля. Далее производится запись информаци в разряды модуля. В режиме контроля сяачала происходи разрыв цепей переноса между триггерами и выделение таким образом контрольных триггеров с целью, осуществления косвенного контроля каждого модуля. Для осуществления косвенного конт роля модуля необходимо разорвать сначала цепи переноса между триггерами 2 2 4,2 3 и 2 4,2 4 и 2 1, так как контрольными триггера ми данного модуля являются триггеры 2 . 3,2 4. С этой целью с генератора 15 .подается сигнал (0,1,1, 1,0) соответственно, тфи этом с первого, второго, третьего и четвертого выходов дещифратора 8 выдается соответственно (0,1,0,0). Тогда на первые ;вхо ды элементов ИЛИ 9 и 10 поступает I, на вторые входы элементов ИЛИ 9 и 10 поступает О, а на третий ; вход элемента ИЛИ 1О поступает О, |При этом с выходов элемента ИЛИ 9 и 10 выдается (1,1) с выходов эпемен .тов НЕ 14 и 13 вьшается (оД), ас выходов элементов. И 5 1, И-НЕ , И 5 2. И-НЕ J 2,И 5 3,И-НЕ 7 3, и 5 4, И-НЕ 7. 4 выддется соответственно (O,l,O,0,0,O,O,Ci). Таким образом, на вторые .входы элементов ИЗ 1-. 3 -4 поступают сигналы соответственно (1,О,0,0), и тем саMbHvi рвутсяцепи переносов между тригг рами 2 -- 2 и 2 - 3, 2 - 3 и 2 - 4, 2 - 4 и 2 1 модуля. Анапогично1контроП1фуются модулу, входящие в состав двоичного счетчика. Ф о р м л а изобретения Модуль двоичного счетчика, содержащий генератор тестовых сиг налов и четыре разряда, каждый из которых состоит из триггера, выход которого соединен с первым входом элемента И, выход которого подключен к первому ходу трттера последующего разряда, о РЛ. ичающийся тем, что, с целью повышения надежности работы устройства, в него введены дещифратор, элементы совпадения, элементы ИЛИ и НЕ, а в каждый разряд - Дополнительные элементы И .и элементы И-НЕ, при этом в каждом разряде ко второму входу трнг гера подключены последовательно два дополнительных элемента И, к третьег у входу триггера - выход третьего дополнительного элемента И, ко второму входу элемента И выход элемента И-НЕ, а первые входы второго и третьего дополнительных элементов И и элемента И-НЕ объединены, при этом два первых выхода з енератора тестовых сигналов подключены ко аходам дешифратора, третий выход - ко второму входу -третьего дополнительного элемента И каждого разряда непосредственно и ко второму входу первого дополнительного элемента И каждого разряда через первый элемент . . НЕ, четвертьй выход ко второму .входу элемента И-НЕ -каждого разряда йе- Посредственно и ко второму входу второго дополнительного элемента И ка кдого разряда через второй элемент НЕ, первый выход дешифратора соединен со входом первого разряда, второй выход дешифратора - со входом второго разря- . Да и с первым входом первого элемента совпадения, третий вькод дешифратора с первым иходом второго эпемен.та совпадения н с первым входом первого элемента ИЛИ, выход которого пршслючен ко входу третьего разряда, а четвертый выход дешифратора - с первьш входом второго элемента ИЛИ, второй вход которого подключен к выходу второго элемента совпадения, третий вход - к вьссоду первого элемента совпадения и ко второму Bxof первого элемента ИЛИ, а выход - к входу четвертого разряда, причем вторые входы элементов совпадения соединены с пятьхм вькодом генератора тестовых сигналов. Источники информации, пр(шятые во внимание при экспертизе 1. Авторасое свидетельство СССР по заявке № 2668864/21, кл.н 03 К 23/24, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигнала прерывания | 1984 |

|

SU1241242A1 |

| Регистр сдвига | 1979 |

|

SU858107A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1196692A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Устройство формирования сигнала прерывания | 1983 |

|

SU1112365A1 |

| УСТРОЙСТВО ФАЗОВОГО ПУСКА | 2002 |

|

RU2240655C2 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

| Устройство формирования сигнала прерывания | 1985 |

|

SU1290327A1 |

Авторы

Даты

1981-11-30—Публикация

1979-07-26—Подача