(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1043652A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

| Микропрограммное устройство управления | 1980 |

|

SU888120A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Реконфигурируемое устройство с программным управлением | 1981 |

|

SU1007108A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1983 |

|

SU1120337A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Микропрограммное вычислительное устройство | 1981 |

|

SU1008741A1 |

| Микропрограммное устройство управления | 1980 |

|

SU938283A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах управления ЭВМ,

Известно перестраиваемое микропрограммное устройство.управления, содеря(ащее два блока памяти, два регистра, два коммутатора, два триг-. гера, элементы ИЛИ и элементы . .

Однако устройство обладает низкой отказоустойчивостью, обусловленной структурной корреляцией ;адрес-. . ных и операционных частей микрокоманд при идентификации отказов в них, большим количеством оборудования, обусловленным дублированием информации в ячейках блоков памяти при наличии в микропрограмме повторяющихся микрокоманд, низким быстродействием, .обусловленным снижением частоты выдачи микрокоманд на выхо де устройства при отказе.одного из блоков памяти. . . .

Наиболее близким к предлагаемому по технической сущности и положительному эффекту является перестраиваемое микропрограммное устройство уп-. равления, которое содержит два блока Пс1мяти, два коммутатора, два регистра, два элемента И, два триггера, . два элемента И, блок элементов ИЛИ,

причем группы адресных выходов первого и второго блоков памяти соединены с первыми группами информационных входов соответственно первого и второго .регистров, первые группы выходов которых соединены с группами адрес-, ных.входов второго и первого блоков памяти.соответственно, причем установочные входы первого и второго ре10гистров соединены с выходами неисправности первого и второго блоков памяти соответственно, входы второй группы информационных входов первого и второго регистров соединены с

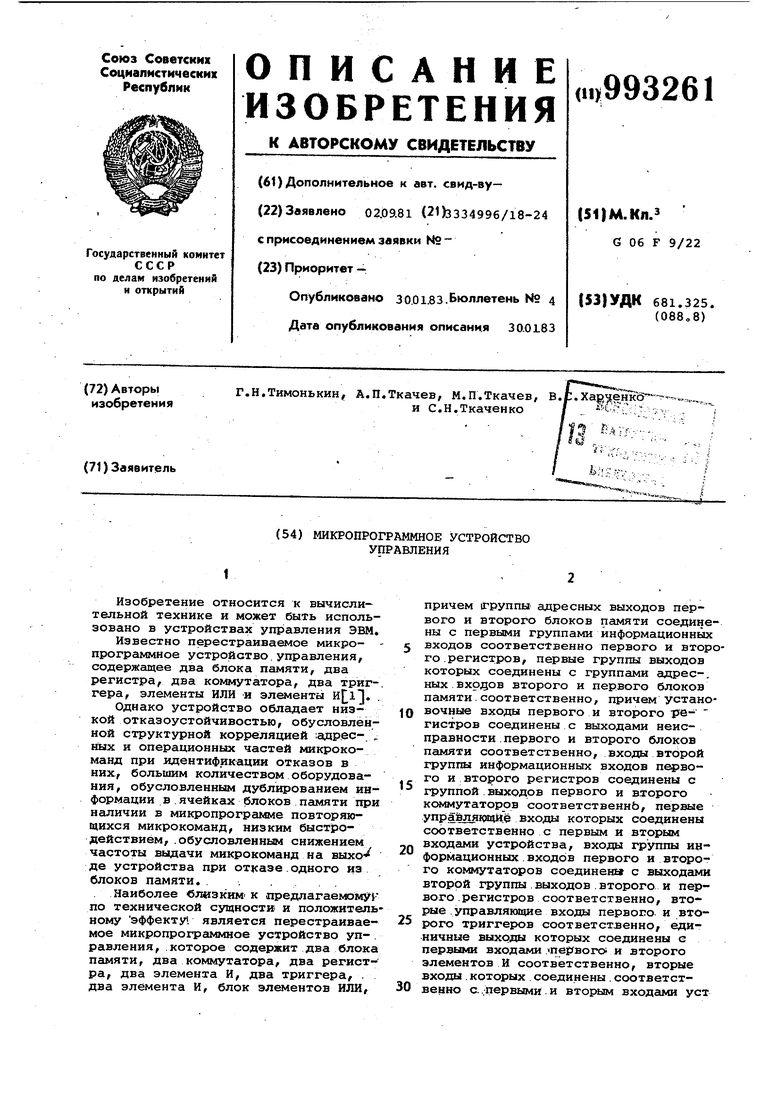

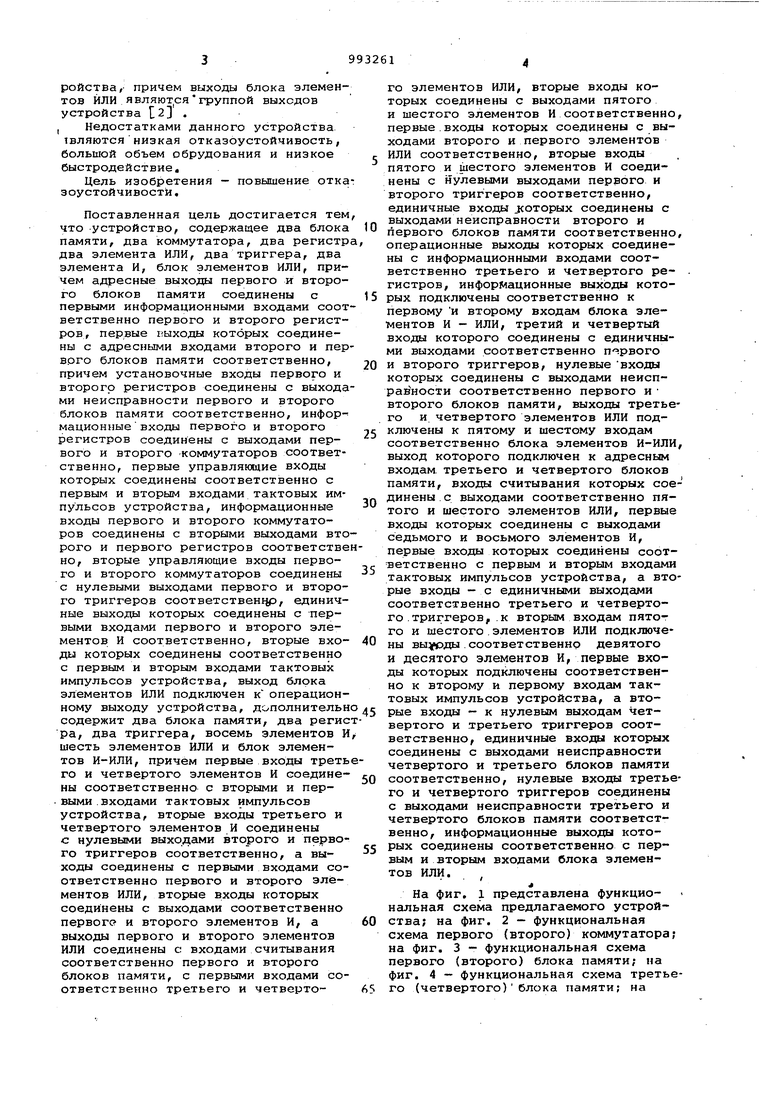

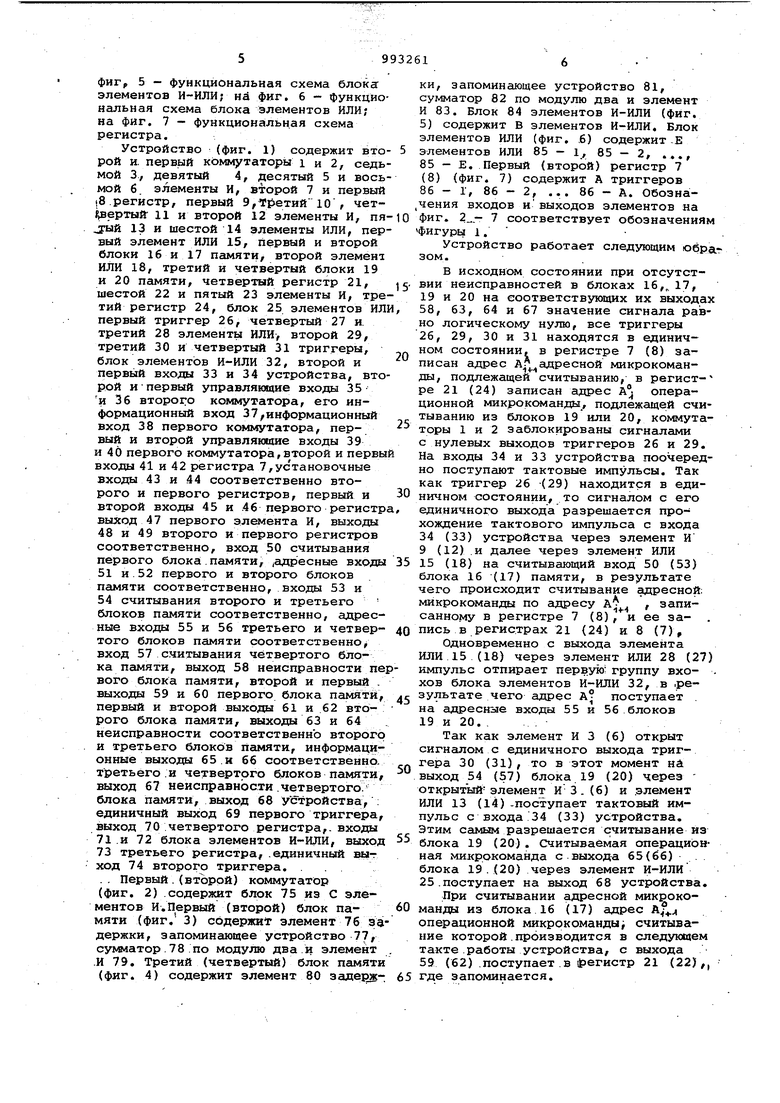

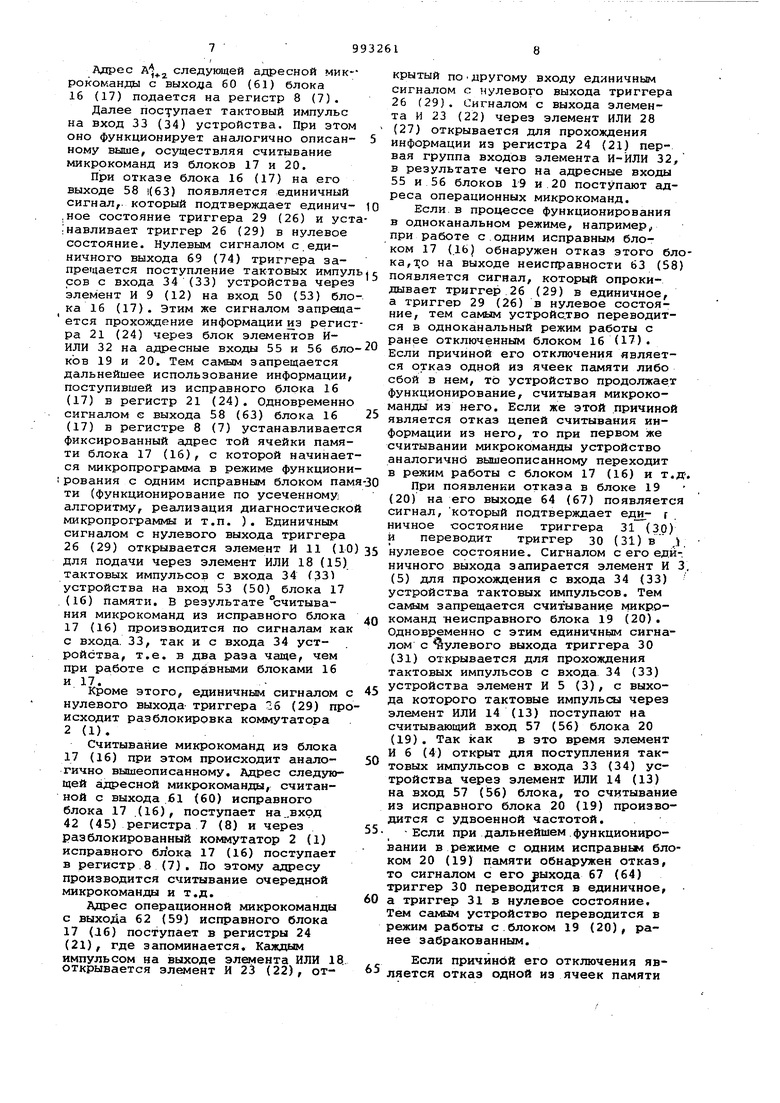

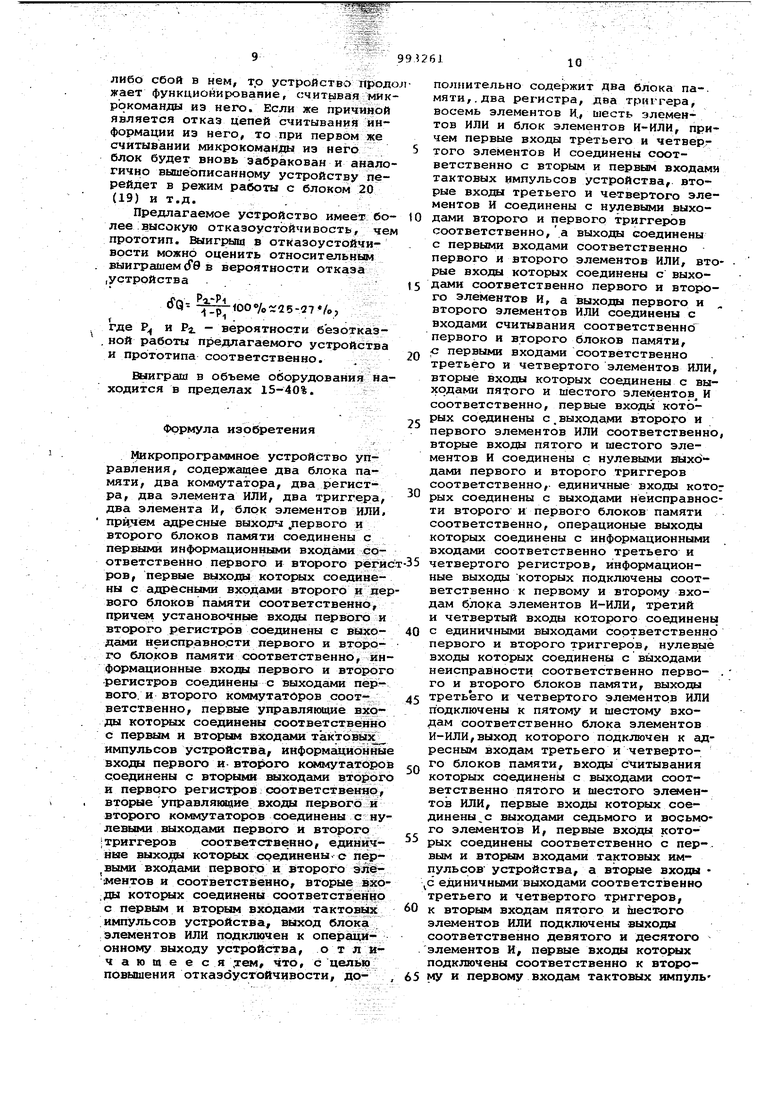

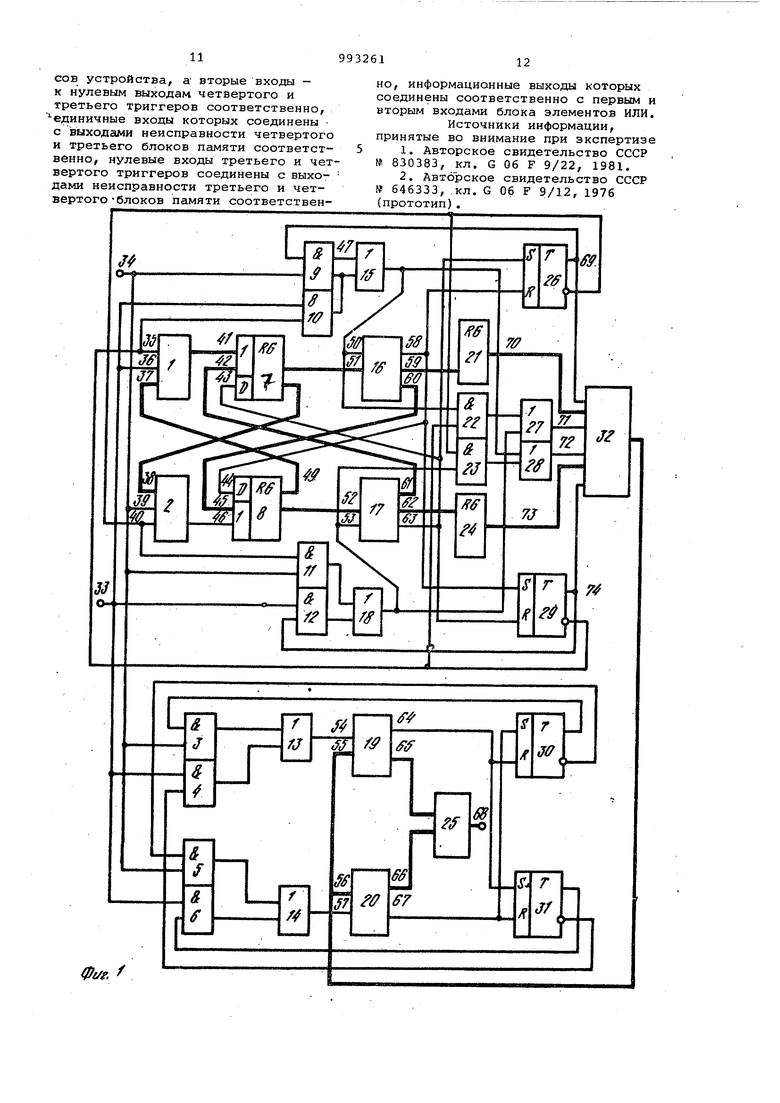

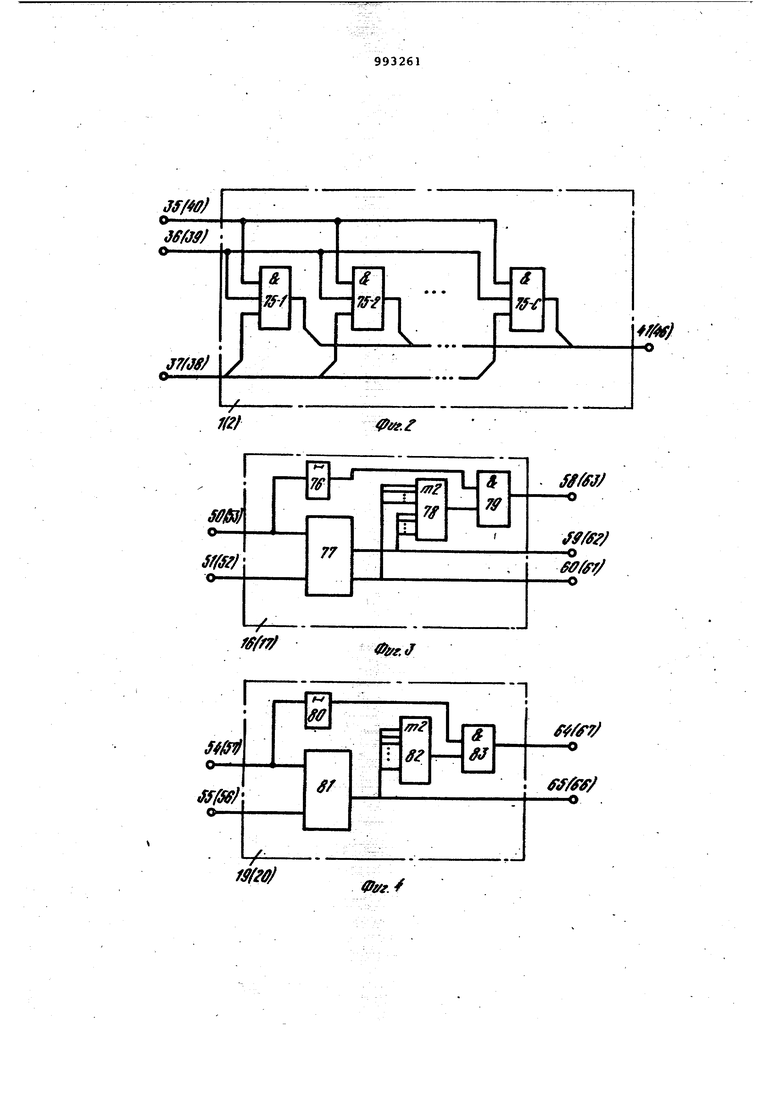

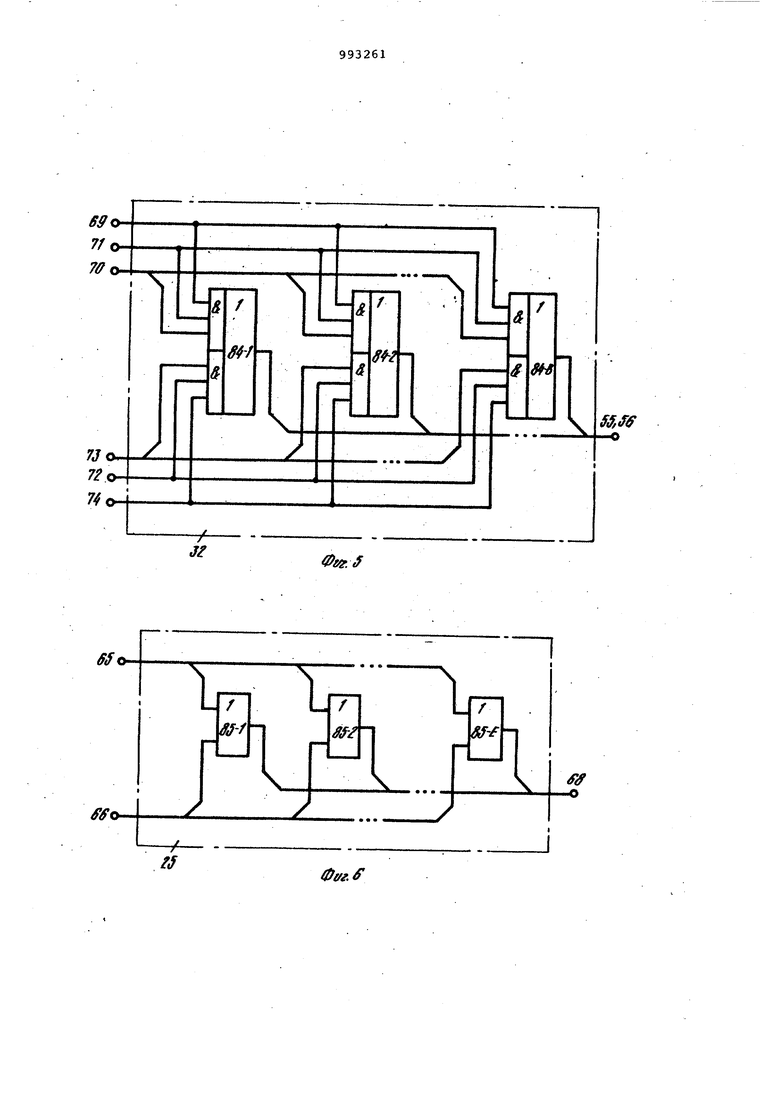

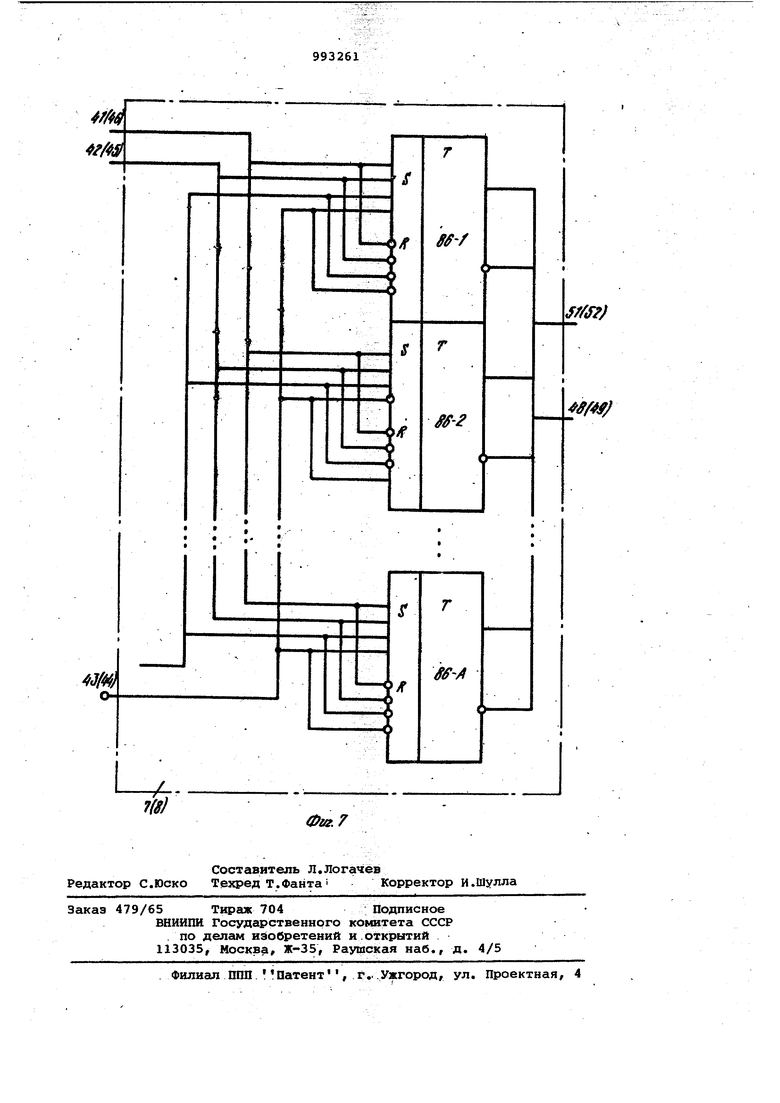

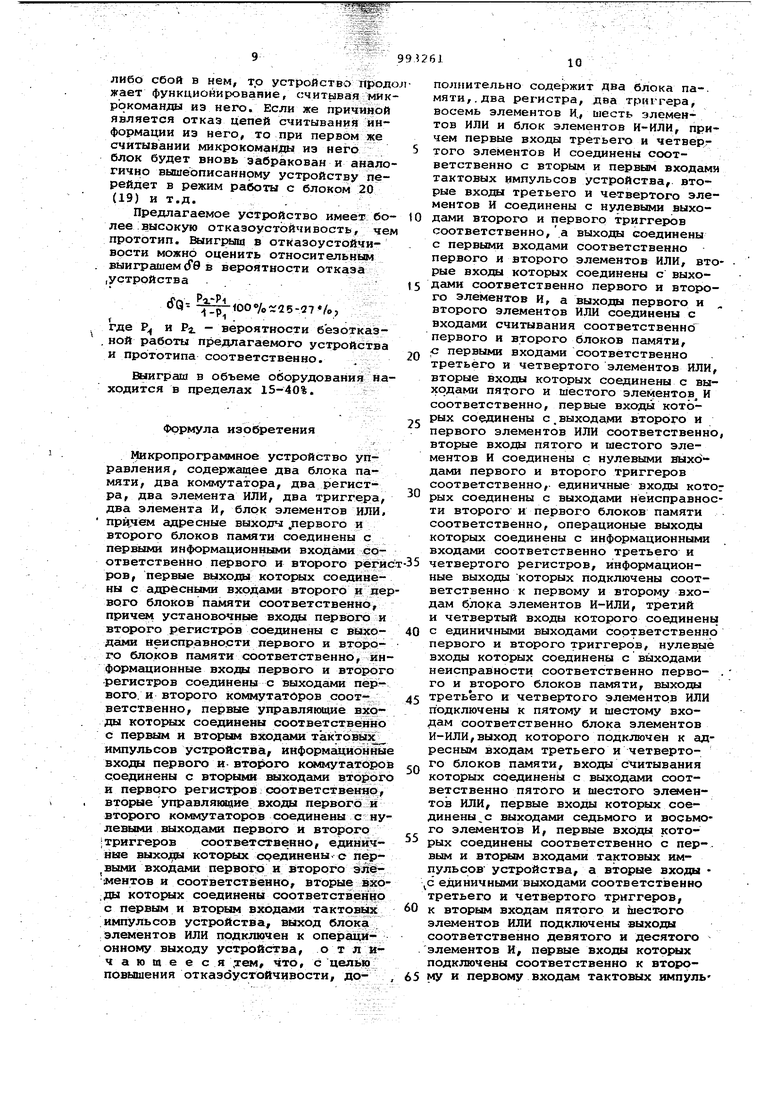

15 группой выходов первого и в.торого кс 1мутаторов соответственнЬ, первые управляквдиё входы которых соединены соответственно с первым и вторым входами устройства, входы группы ин20формационных входов первого и второго коммутаторов соединена с выходами второй группы.выходов.второго и первого .регистров соответственно, вторые управляющие входы первого и вто25рого триггеров соответственно, единичные выходы которых соединены с первыми входги и . и второго элементов И соответственно, вторые входы.которых соединены.соответст30венно с. ..первыми и вторым входаими уст ройства,- причем выходы блока элементов ИЛИ я вляют сягруппой выходов устройства ЕЗ . , Недостатками данного устройства 1ВЛЯЮТСЯ низкая отказоустойчивость, большой объем обрудования и низкое быстродействие. Цель изобретения - повышение отка зоустойчивости. Поставленная цель достигается тем что устройство, содержащее два блока памяти, два коммутатора, два регистр два элемента ИЛИ, два триггера, два элемента И, блок элементов ИЛИ, причем адресные выходы первого и второго блоков памяти соединены с первыми информационными входами соот ветственно первого и второго регистров, первые пыходы которых соединены с адресными входами второго и пер вого блоков памяти соответственно, причем установочные входы первого и второго регистров соединены с выхода ми неисправности первого и второго блоков памяти соответственно, информационныевходы первого и второго регистров соединены с выходами первого и второго -коммутаторов соответственно, первые управляющие входы которых соединены соответственно с первым и вторым входами тактовых импульсов устройства, информационные входы первого и второго коммутаторов соединены с вторыми выходами вто рого и первого регистров соответстве но, вторые управляющие входы первого и второго коммутаторов соединены с нулевыми выходами первого и второго триггеров соответственчр, единичные выходы которых соединены с первыми входами первого и второго элементов И соответственно, вторые входы которых соединены соответственно с первым и вторым входами тактовых импульсов устройства, выход блока элементов ИЛИ подключен к операционному выходу устройства, дополнительн содержит два блока памяти, два регис ра, два триггера, восемь элементов И шесть элементов ИЛИ и блок элементов И-ИЛИ, причем первые входы треть го и четвертого элементов И соединены соответственно с вторыми и первыми, входами тактовых импульсов устройства, вторые входы третьего и четвертого элементов И соединены с нулевыми выходами второго и первого триггеров соответственно, а выходы соединены с первыми входами соответственно первого и второго элементов ИЛИ, вторые входы которых соединены с выходами соответственно первогс и второго элементов И, а выходы первого к второго элементов ИЛИ соединены с входами считывания соответственно первого и второго блоков памяти, с первыми входами соответственно третьего и четвертого элементов ИЛИ, вторые входы которых соединены с выходами пятого и шестого элементов И соответственно, первые.входы которых соединены с выходами второго и первого элементов ИЛИ соответственно, вторые входы пятого и шестого элементов И соединены с н улевыми выходами первого и второго триггеров соответственно, единичные входы J(oтopыx соединены с выходами неисправности второго и первого блоков памяти соответственно, операционные выходы которых соединены с информационными входами соответственно третьего и четвертого регистров, информационные выходы которых подключены соответственно к первому и второму входам блока элементов И - ИЛИ, третий и четвертый входы которого соединены с единичными выходами соответственно п рвого и второго триггеров, нулевые входы которых соединены с выходами неисправности соответственно первого и второго блоков памяти, выходы третьего и четвертого элементов ИЛИ подключены к пятому и шестому входам соответственно блока элементов И-ИЛИ, выход которого подключен к адресным входам третьего и четвертого блоков памяти, входы считывания которых соединены, с выходами соответственно пятого и шестого элементов ИЛИ, первые входы которых соединены с выходами седьмого и восьмого элементов И, первые входы которых соединены соответственно с первым и вторым входами тактовых импульсов устройства, а вторые входы - с единичными выходами соответственно третьего и четвертого .триггеров, .к вторым входам пятого и шестого.элементов ИЛИ подключены соответственно девятого и десятого элементов И, первые входы которых подключены соответственно к второму и первому входам тактовых импульсов устройства, а вторые входы - к нулевым выходам четвертого и .третьего триггеров соответственно, единичные входы которых соединены с выходами неисправности четвертого и третьего блоков памяти соответственно, нулевые входы третьего и четвертого триггеров соединены с выходами неисправности третьего и четвертого блоков памяти соответственно, информационные выходы которых соединены соответственно с первым и вторым входами блока элементов ИЛИ. , На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема первого (второго) коммутатора; на фиг. 3 - функциональная схема первого (второго) блока памяти; на фиг. 4 - функциональная схема третьего (четвертого)блока памяти; на фиг, 5 - функциональная схема блока: элементов И-ИЛИ; ни фиг, 6 - функциональная схема блока элементов ИЛИ; на фиг. 7 - функциональная схема регистра. Устройство (фиг. 1) содержит вто рой и. первый коммутаторы i и 2, седьмой 3., девятый 4, десятый 5 и вось мой б. элементы И, второй 7 и первый |8 регистр, первый 9,Т1 етий10 , чет|;вертый 11 и второй 12 элементы И, пя рый 13 и шестой 14 элементы ИЛИ, пер вый элемент ИЛИ 15, первый и второй блоки 16 и 17 памяти, второй элемент ИЛИ 18, третий и четвертый блоки 19 и 20 памяти, четвертый регистр 21, шестой 22 и пятый 23 элементы И, тре тий регистр 24, блок 25 элементов ИЛ первый триггер 26, четвертый 27 и третий 28 элементы ИЛИ, второй 29, третий 30 и четвертый 31 триггеры, блок элементов И-ИЛИ 32, второй и первый входы 33 и 34 устройства, вто рой и первый управляющие входы 3 5 и 36 второго коммутатора, его информационный вход 37,информационный вход 3 8 первого коммутатора, первый и второй управляющие входы 39 и 40 первого коммутатора, второй и первы входы 41 и 42 регистра 7,установочные вхогда 43 и 44 соответственно второго и первого регистров, первый и второй входы 45 и 46 первого регистр выход 47 первого элемента И, выхода 48 и 49 второго и первого регистров соответственно, вход 50 считывания первого блока памяти, адресные входы 51 и 52 первого и второго блоков памяти соответственно, входы 53 и 54 считывания второго и третьего блоков памяти соответственно, адресные входы 55 и 56 третьего и четвертого блоков памяти соответственно вход 57 считывания четвертого блока памяти, выход 58 неисправности пе вого блока памяти, второй и первый . выходы 59 и 60 первого блока памяти, первый и второй выходы 61 и 62 второго блока памяти, выходы 63 и 64 неисправности соответственно второго и третьего блоков памяти, информационные выходы 65 и 66 соответственно. третьего.и четвертого блоков памя:ти, выход 67 неисправности .четвертого блока памяти, выход 68 устройства, : единичный выход 69 первого триггера, выход 70 четвертого регистра,, входы 71 .и 72 блока элементов И-ИЛИ, выход 73 третьего регистра,.единичный выт ход 74 второго триггера. . . .. Первый.(второй) коммутатор (фиг. 2).содержит блок 75 из С элементов И,Первый (второй) блок памяти (фиг. 3) содержит элемент 76 за держки, эапоминающее устройство 77, сумматор.78 по модулю два и элемент .И 79. Третий (четвертый) блок памяти (фиг. 4) содержит элемент 80 эадещки, запоминающее устройство 81, сумматор 82 по модулю два и элемент И 83. Блок 84 элементов И-ИЛИ (фиг. 5) содержит В элементов И-ИЛИ. Блок элементов ИЛИ (фиг. ,6) содержит-Е элементов ИЛИ 85 - 1, 85-2, ..., 85- Е. Первый (второй) регистр 7 (8) (фиг. 7) содержит А триггеров 86- 1, 86-2, ... 86 - А. Обозначения входов ивыходов элементов на фиг. 7 соответствует обозначениям фигуры 1. Устройство работает следующим образом. В исходном состоянии при отсутствии неисправностей в блоках 16,, 17, 19 и 20 на соответствующих их выходах 58, 63, 64 и 67 значение сигнала равно логическому нулю, все триггеры 26, 29, 30 и 31 находятся в единичном состоянии, в регистре 7 (8) записан адрес А| адресной микрокоманды, подлежащей считыванию, в регистре 21 (24) записан адрес A° операционной микрокоманды, подлежащей считыванию иэ блоков 19 или 20, коммутаторы 1 и 2 заблокированы сигналами с нулевых выходов триггеров 26 и 29. На входы 34 и 33 устройства поочередно поступают тактовые импульсы. Так как триггер 26 (29) находится в единичном состоянии, то сигналом с его единичного выхода разрешается прохождение тактового импульса с входа 34 (33) устройства через элемент И 9 (12).и далее через элемент ИЛИ 15 (18) на считывающий вход 50 (53) блока 16 (17) памяти, в результате чего происходит считывание адресной; микрокоманды по адресу А записанному в регистре 7 (8) , ее запись в регистрах 21 (24) и 8 (7), Одновременно с выхода элемента ИЛИ. 15. (18) через элемент ИЛИ 28 (27) импульс отпирает первую; группу вхохов блока элементов И-ИЛИ 32, в .результате чего адрес А| поступает . на адресные входы 55 и 56.блоков 19 и 20. Так как элемент ИЗ (6) открыт сигналом с единичного выхода триггера 30 (31), то в этот момент ни выход 54 (57) блока 19 (20) через открытый-элемент ИЗ. (6) и .элемент ИЛИ 13 (14) -поступает тактовый импульс с входа 34 (33) устройства. Этим салллм разрешается считывание из блока 19 (20). Считываемая операционная микрокоманда с выхода 65(66) блока 19. (20) через элемент И-ИЛИ 25.поступает на выход 68 устройства. При считывании адресной микрокоманды из блока 16 (17) адрес А операционной микрокоманды; считывание которой.производится в следующем такте работы устройства, с выхода 59 (62) .поступает в егистр 21 (22),, где запоминается. Адрес A.j следующей адресной микрокоманды с выхода 60 (61) блока 16(17) подается на регистр 8 (7). Далее поступает тактовый импульс на вход 33 (34) устройства. При этом оно функционирует аналогично описанному выше, осуществляя считывание микрокоманд из блоков 17 и 20. При отказе блока 16 (17) на его выходе 58 (63) появляется единичный сигнал,, который подтверждает единич.ное состояние триггера 29 (26) и уст :навливает триггер 26 (29) в нулевое состояние. Нулевым сигналом с.единичного выхода 69 (74) триггера запрещается поступление тактовых импул сов с входа 34 (33) устройства через элемент И 9 (12) на вход 50 (53) бло ка 16 (17). Этим же сигналом запреада ется прохождение информации из регист ра 21 (24) через блок элементов ИИЛИ 32 на адресные входы 55 и 56 бло ков 19 и 20. Тем самым запрещается дальнейшее использование информации, поступившей из исправного блока 16 (17) в регистр 21 (24). Одновременно сигналом с выхода 58 (63) блока 16 (17) в регистре 8 (7) устанавливаетс фиксированный адрес той ячейки памяти блока 17 (16) , с которой начинает ся микропрограмма в режиме функциони рования с одним исправным блоком пам ти (функционирование по усеченному алгоритму, реализация диагностическо микропрограммы и т.п. ). Единичным сигналом с нулевого выхода триггера 26 (29) открывается элемент И 11 (10 для подачи через элемент ИЛИ 18 (15) тактовых импульсов с входа 34 (33) устройства на вход 53 (50) блока 1 (16) памяти, В результате считывания микрокоманд из исправного блока 17(16) производится по сигналам как с входа. 33, так и с входа 34 устройства, т.е. в два раза чаще, чем при работе с исправными блоками 16 Кроме этого, единичным сигналом с нулевого выхода триггера 26 (29) про исходит разблокировка коммутатора 2 (1). Считывание микрокоманд из блока 17 (16) при этом происходит аналогично вышеописанному, Ацрес следующей адресной микрокоманды, считанной с выхода 61 (60) исправного блока 17 .(16), поступает на..вхрд 42 (45) регистра 7 (8) и через разблокированный коммутатор 2 (1) исправного блЪка 17 (16) поступает в регистр 8 (7). По этому адресу производится считывание очередной микрокоманды и т.д. Адрес операционной микрокоманды с выхода 62 (59) исправного блока 17 (Дб) поступает в регистры 24 (21), где запоминается. Каждым импульсом на выходе элемента ИЛИ 18. открывается элемент И 23 (22), открытый по-другому входу единичным сигналом с нулевого выхода триггера 26 (29). Сигналом с выхода элемента и 23 (22) через элемент ИЛИ 28 (27) открывается для прохождения информации из регистра 24 (21) первая группа входов элемента И-ИЛИ 32, в результате чего на адресные входы 55 и 56 блоков 19 и 20 поступают адреса операционных микрокоманд. Если.в процессе функционирования в одноканальном режиме, напримерj, при работе с.одним исправным блоком 17 (.16) обнаружен отказ этого блока,то на выходе неисправности 63 (58) появляется гигпяп появляется сигнал который опрокидывает триггер 26 (29) в единичное, а триггер 29 (26) в нулевое состояние, тем самым устройство переводится в одноканальный режим работы с ранее отключенным блоком 16 (17). Если причиной его отключения является отказ одной из ячеек памяти либо сбой в нем, то устройство продолжает функционирование, считывая микрокоманды из него. Если же этой причиной является отказ цепей считывания информации из него, то при первом же считывании микрокоманды устройство аналогично вышеописанному переходит в режим работы с блоком 17 (16) и т.д. При появлении отказа в блоке 19 (20) на его выходе 64 (67) появляется сигнал, который подтверждает f ничное состояние триггера 31 (30) и переводит триггер ЗО (31) в нулевое состояние. Сигналом с его единичного выхода запирается элемент И 3, (5) для прохождения с входа 34 (33) устройства тактовых импульсов. Тем самым запрещается считывани.е микрокоманд неисправного блока 19 (20), Одновременно с этим единичным сигналом с Нулевого выхода триггера 30 (31) открывается для прохождения тактовых импульсов с входа. 34 (33) устройства элемент И 5 (3), с выхода которого тактовые импульсы через элемент ИЛИ 14 (13) поступают на считывающий вход 57 (56) блока 20 (19). Так как в это время элемент И 6 (4) открыт для поступления тактовых импульсов с входа 33 (34) устройства через элемент ИЛИ 14 (13) на вход 57 (56) блока, то считывание из исправного блока 20 (19) производится с удвоенной частотой, - Если при дальнейшем функционировании в режиме с одним исправньм блоком 20 (19) памяти обнаружен отказ, то сигналом с его ыхода 67 (64) триггер 30 переводится в единичное, а триггер 31 в нулевое состояние. Тем самым устройство переводится в режим работы с блоком 19 (20), ранее забракованным. Если причиной его отключения является отказ одной из ячеек памяти либо сбой в нем, тр устройство прод жает функционирование, считывая мик рокоманды из него. Если же причиной является отказ цепей считывания информахдаи иэ него, то при первом же считывании микрокоманду иэ него блок будет вновь забракован и анало гично вышеописанному устройству перейдет в режим работы с блоком 20 (19) и т.д. . Предлагаемое устройство имеет бо лее : высокую отказоустойчивость, че прототип. Выигрыш в отказоустойчивости можно оценить относительным . выиграшем{Гв в вероятности отказа .устройства ... 9- t OOo/o-26-27 /., . где Р и Ра. - вероятности безотказ, ной работы предлагаемого устройства и прототипа соответственно. Выиграш в объеме оборудования на ходится в пределах 15-40%. Формула изобретения Микропрограммное устройство управления, содержащее два блока памяти, два коммутатора, два регистра, два элемента ИЛИ, два триггера, два элемента И, блок элементов ИЛИ, причём адресные выходч .первого и второго блоков памяти соединены с первыми информационными входами со- ответствейно первого и второго реги ров, первые выходы которых соединены с адресными входами второго и ле вого блоков памяти соответственно, причем установочные входа первого и второго регистров соединены с выходами неисправности первого и второго блоков памяти соответственно, ин формационные входы первого и второг регистров соединены с выходами первого, и второго коммутаторов соответственно, первые угфавлякнцие входы которых соединены соответственно с первым и вторым входами тактовых импульсов устройства, информационны входы первого и- второго коммутаторо соединены с вторыми шаходами второг и первого регистров соответственно, вторые управляющие входы первого и второго коммутаторов соединены с ну левыми выходами первого и второго ;триггеров соответственно, единичные выхо которых соединены, с пер,выми входами первого и второго элементов и соответственно, вторые вхо ,ды которых соединены соответственно с первым и вторым входами тактовых импульсов устройства, выход блока элементов ИЛИ подключен к операционному выходу устройства, о т л ич аюше е ся .тем, что, с целью повышения отказоустойчивости, до99 26J.

10 полиительно содержит два блока па-. мяти,.два регистра, два триггера, восемь элементов И., шесть элементов ИЛИ и блок элементов И-ИЛИ, причем первые входы третьего и четвертого элементов И соединены соответственно с вторым и первым входами тактовых импульсов устройства, вторые входы третьего и четвертого элементов И соединены с нулевыми выходами второго и первого триггеров соответственно,а выходы соединены с первыми входами соответственно первого и второго элементов ИЛИ, вторые входы которых соединены с выходами соответственно первого и второго элементов И, а выходы первого и второго элементов ИЛИ соединены с входами считывания соответственно первого и второго блоков памяти, о первыми входами соответственно третьего и четвертого элементов ИЛИ, вторые входы которых соединены с выходами пятого и шестого элементов И соответственно, первые входы которых соединены с,выходами второго и первого элементов ИЛИ соответственно, вторые входда пятого и шестого элементов И соединены с нулевыми выходами первого и второго триггеров соответственно,, единичные входы котог рых соединены с выходами неисправности второго и первого блоков памяти соответственно, операционые выходы которых соединены с информационными . входами соответственно третьего и четвертого регистров, информационные выходы которых подключены соответственно к первому и второму входам блока элементов И-ИЛИ, третий и четвертый входы которого соединены с единичными выходами соответственно первого и второго триггерс в, нулевые входы которых соединены с выходами неисправности соответственно перво- . го и второго блоков памяти, выходы третьего и четвертого элементов ИЛИ подключены к пятому и шестому входам соответственно блока элементов И-ИЛИ,выход которого подключен к адресным входёил третьего и четвертого блоков памяти, входы считывания которых соединены с выходами соответственно пятого и шестого элементов ИЛИ, первые входы которых соединены с выходами седьмого и восьмого элементов И, первые вхЬды которых соединены соответственно с пер-. вым и вторым входами тактовых импульсов устройства, а вторые входы с единичными выходами соответственно третьего и четвертого триггеров, к вторым входам пятого и шестого элементов ИЛИ подключены выходы соответственно девятого и десятого элементов И, первые входы которых подключены соответственно к второму и первому входам тактовых импульсов устройства, а вторые входы - к нулевым выходам четвертого и третьего триггеров соответственно, единичные входы которых соединены с выходами неисправности четвертого и третьего блоков памяти соответственно, нулевые входы третьего и четвертого триггеров соединены с выхо- дами неисправности третьего и четвертого -блоков памяти соответственно, информационные выходы которых соединены соответственно с первым и вторым входами блока элементов ИЛИ.

Источники информации, принятые во внимание при экспертизе

)

J7M

т

fffif7

Ш)

о

ЙК/

&f.J

г5йг. /

/

Л

;г1

f т

/ Wf

IPL

//

Фуг.

ss-f

sy

o

Авторы

Даты

1983-01-30—Публикация

1981-09-02—Подача