1

Изобретение относится к технике связи и может быть использовано в автоматике, телемеханике и вычислительной технике, в частности для передачи информации между процессорами и ОЗУ в вычислительных комплексах.

Известно устройство для двусторонней передачи информации 1. Каждый приемопередающий узел этого устройст,ва содержит источник информации, усилители передаваемого и принимаемого сигналов, комплексное сопротивление, двухпроводную линию. Поскольку в такой системе отсутствуют параллельнопоследовательные преобразователи, то передача информации осуществляется параллельным кодом, что требует значительных затрат кабеля и является недостатком данной системы.

Известно также устройство для передачи сигнала ,2, содержащее счетчик генерируемых импульсов, схему управления счетчиком, линии связи, регистр, счетчик принимаемых импульсов, схему управления принятым сигналом. Недостатком данного устройства является то, что после воздействия помех на линии связи в счетчики устройства не обеспечивается автоматической восстанавливаемости и требуется общий сброс. Это приводит к тому, что нельзя обеспечить передачу непрерывного потока сообщений. Таким образом, область применения устройства ограничена модулями, обмен информацией между которыми может быть приостановлен.

Известно устройство для передачи информации , которое содержит на

10 передающей стороне блок управления, выходы которого соединены соответственно с первыми входами триггера и элемента И, первым входом счетчика и первым входом преобразователя парал15лельного кода в последовательный, выход которого подключен к первой линии связи, второй вход триггера подключен к второй линии связи, выход триггера соединен с вторым входом

20 элемента И, выход которого подключен к третьей линий связи и вторым входам преобразователя параллельного кода в последовательный и счетчика, выходы, преобразователя соединены соот2Sветственно с третьим входом элемента И и третьим входом преобразователя. На приемной стороне устройство содержит преобразователь последовательного кода в параллельный, входы которого подключены к первой и третьей линиям связи, выход - к первому входу блока памяти, счетчик, первый вход которого подключен к третьей лин«и связи, выход соединен с первыми входами коммутатора и первого элемента И, выход которого соединен через первый одновибратор с первым входом эл§.мента ИЛИ и непосредственно с входом триггера, выход триггера соединен с вторым входом элемента ИЛИ, вторым входом первого элемента И и вторым входом колшутатора, первый выход которого соединен с третьим входом элемента ИЛИ, второй выход - через второй одновибратор с первым входом второго элемента И, второй вход которого соединен с выходом элемента ИЛИ, выход подключен к второй линии связи

Целью изобретения является повышение информативности и быстродействия устройства.

Поставленная цель достигается тем, что .в устройство для передачи и приема информации, содержащее на передающей стороне блок управления, первый выход которого соединен с первым входом триггера, выход триггера соединен с первым входом первого элемента И, выход которого подключен к первой линии связи, второй выход блока управления через преобразователь параллельного кода в последовательный подключен к второй линии связи, на приемной стороне - счетчик, вход .которого подключен к первой линии связи, триггер, выход которого соединен с первым входом элемента ИЛИ, подключенного к третьей линии связи, и первый UJiOK , введены четвертая линия связи, на передающей стороне - формирователь импульсов, второй и третий элементы И, вход формирователя импульсов соединен с первы.м выходом блока управления, первый выходс вторым входом первого элемента И, второй выход - с первым входом второго элемента И, выход которого подключен к четвертой линии связи, второй вход второго элемента И объединен с Бходом блока управления и подключен к выходу триггера, третий выход блока управления соединен с первым входом третьего элемента И, второй вход которого подключен к третьей линии связи, выход - соединен с вторым входом первого устройства, на приемной стороне введены регистры адреса, второй блок памяти и сумматор по модулю два, выход которого соединен с вторым входом элемента ИЛИ, первый вход сумматора по модулю два объединен с первыми входами первого и второго блоков памяти, вторые входы которых объединены и подключены к второй линии связи, третий вход .второго блока памяти объединен с первым входом первого регистра адреса и входом триггера и подключен к четвертой линии связи, третий вход первого блока

памяти объединен с первым входом второго регистра адреса и подключен к первой линии связи, выход счетчика соединен с объединенными вторыми входами первого регистра адреса и сумматора по модулю два, выход первого регистра адреса соединен с четвертым входом первого блока памяти и вторым входом второго регистра адреса, выход которого соединен с четвертым входом второго блока памяти.

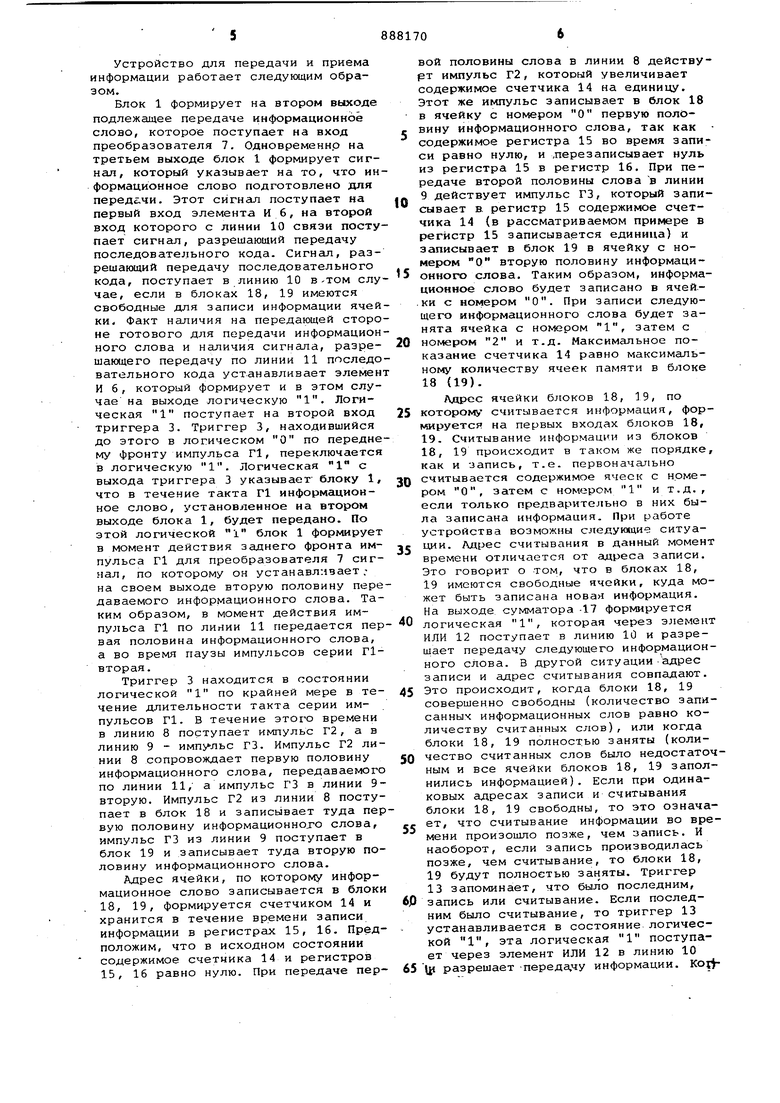

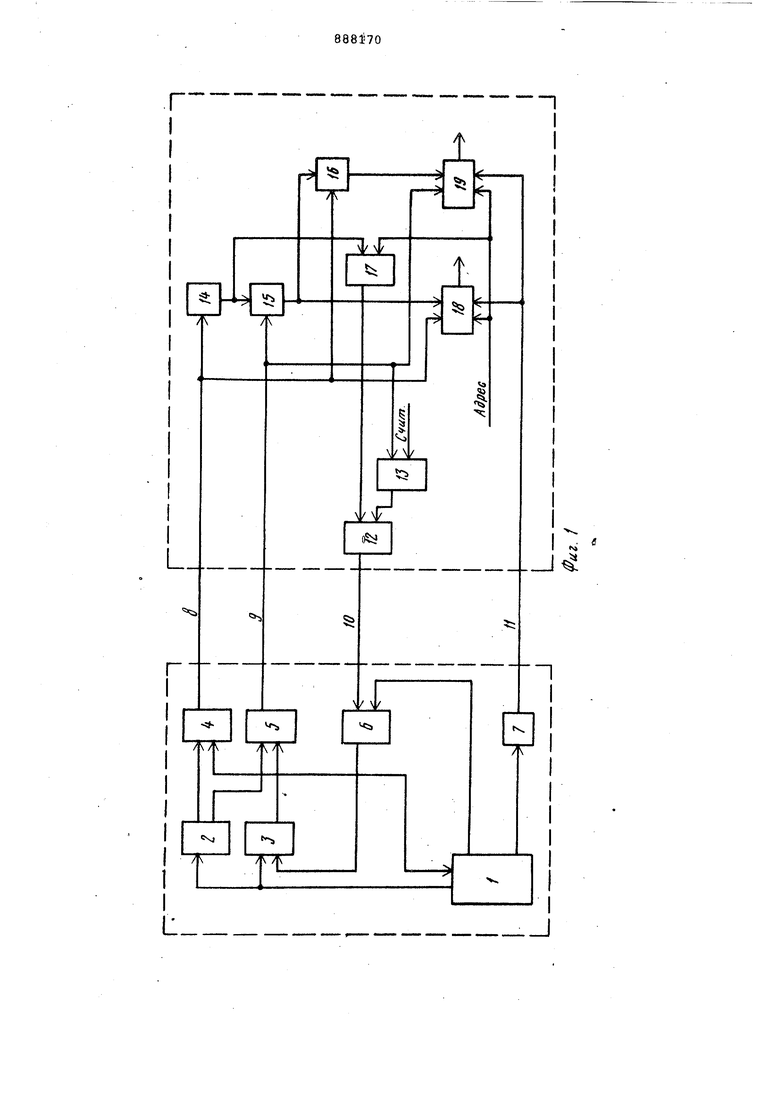

Блок-схема устройства для передачи и приема информации приведена на фиг. 1; на фиг. 2 - временные диаграммы работы устройства. Передающая и приемная стороны устройства условно выделены пунктирной линией (фиг.1

На передающей стороне устройство содержит блок 1 управления, формирователь 2 импульсов, триггер 3, элементы И 4, 5, б, преобразователь 7 параллельного кода в последовательный. Передающая и приемная стороны соединены линиями связи 8, 9, 10, 11 На приемной стороне содержится элемент ИЛИ 12, триггер 13, счетчик 14, первый 15 и второй 16 регистры адреса, сумматор 17 по модулю два, первый 18 и второй 19 блоки памяти.

Для объяснения механизма передачи и приема информации сделаем следующие пояснения.

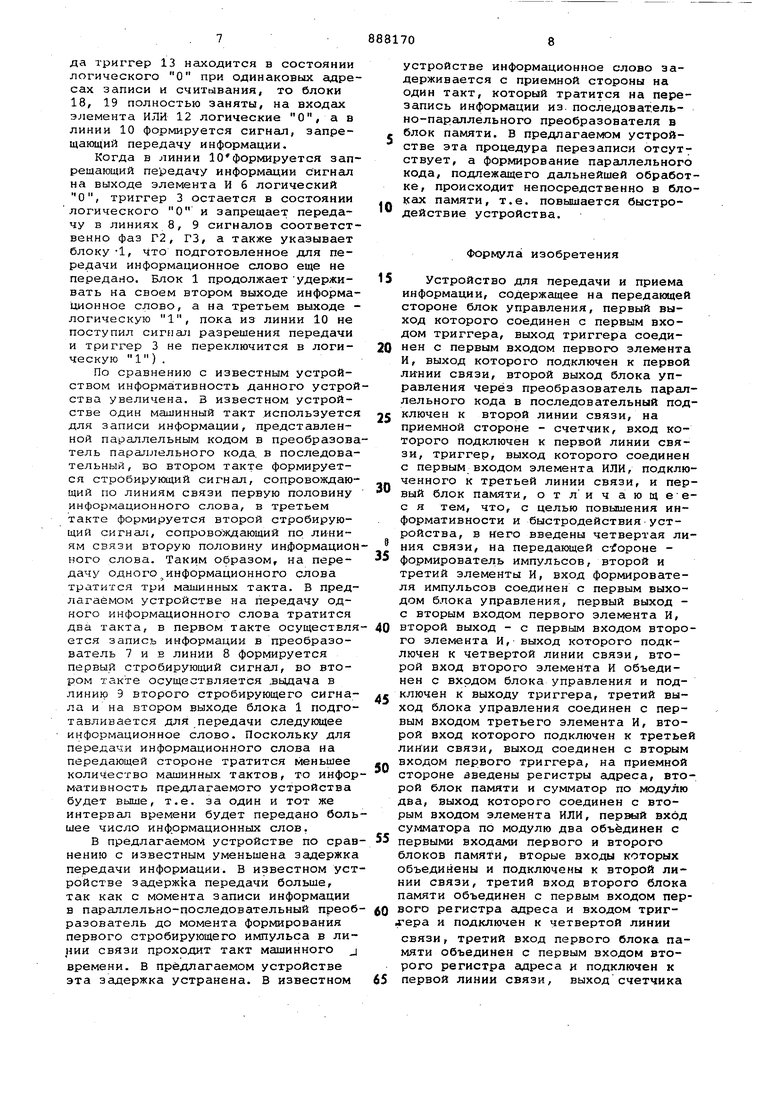

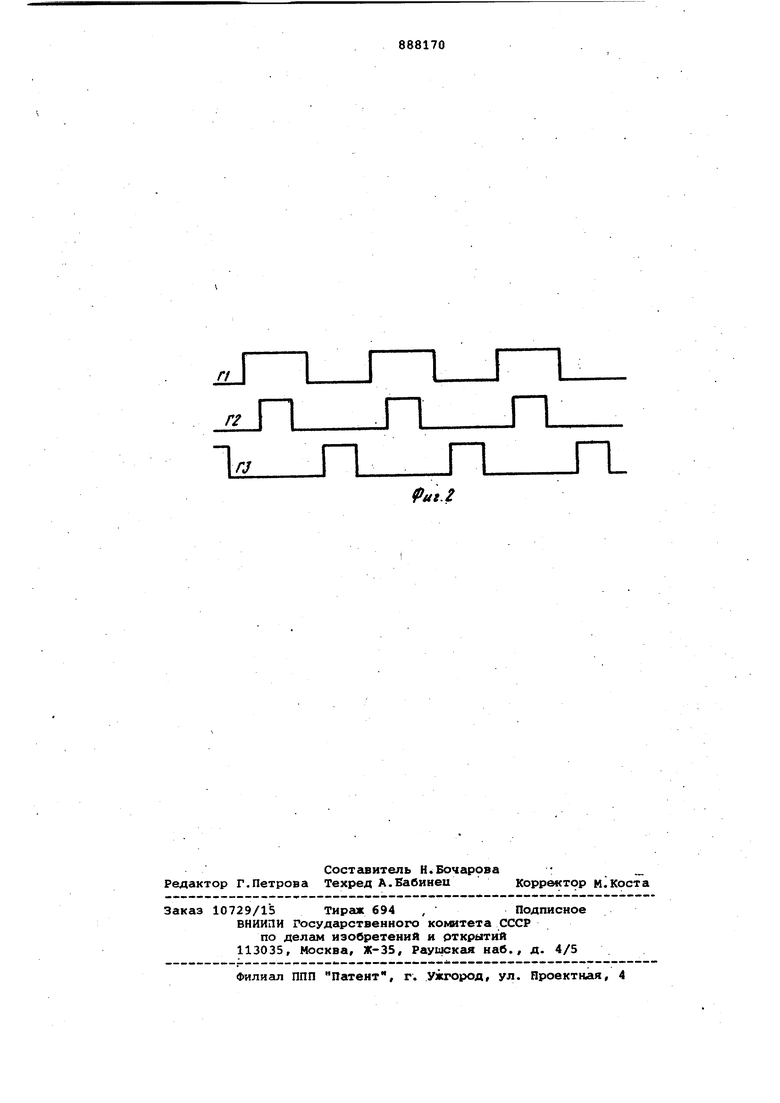

Блок 1, используя задающий гаНератор вычислительной системы (на фиг не показан) формирует на своем первом выходе последовательнос ь (серию прямоугольных импульсов Г1 1фиг. 2). Формирователь 2, используя ее, формирует на своих выходах две серии имлульсов (две фазы) Г2, ГЗ, действующих во времени синхронно с импульсами П. В первом 15 и втором 16 регистрах адреса хранятся адреса ячеек блоков 18, 19, по которым осуществляется запись информации. Адрес ячейки в которую записывается информация, с выходов регистров 15, 16 поступает на соответствующие входы блоков 18/ 19. Адрес ячейки блоков памяти, по которому осуществляется считывание информации из этих блоков, формируется на других входах блоков памяти. Сум;чатор 17 по модулю два формирует на своем выходе сигнал, отождествляемый с наличием информации (предположим, логическую 1), если логические сигналы на его входах отличаются Преобразователь 7 осуществляет преобразование параллельного кода в последовательный. Передаваемое информационное слово разделяется: преобразователем 7 на две половины. Первоначаль но на выходе преобразователя 7 устанавливается первая половина передаваемого слова, а затем вторая. Первая половина передаваемого информационного слова всегда записывается в блок 18, а вторая половина - в |блок 19;

Устройство для передачи и приема информации работает следующим образом.

Блок 1 формирует на втором выходе подлежащее передаче информационное слово, которое поступает на вход преобразователя 7. Одновременно на третьем выходе блок 1 формирует сигнал, который указывает на то, что информационное слово подготовлено для перед.чи. Этот сйгнгш поступает на первый вход элемента И 6, на второй вход которого с линии 10 связи поступает сигнсш, разрешающий передачу последовательного кода. Сигнал, разрешающий передачу последовательного кода, поступает в линию 10 в-том случае, если в блоках 18, 19 имеются свободные для записи информации ячейки. Факт наличия на передающей стороне готового для передачи информационного слова и наличия сигнала, разрешающего передачу по линии 11 последовательного кода устанавливает элемен И 6, который формирует и в этом случае на выходе логическую 1. Логическая 1 поступает на второй вход триггера 3. Триггер 3, находившийся до этого в логическом О по переднему фронту импульса Г1, переключается в логическую 1. Логическая 1 с выхода триггера 3 указывает блоку 1, что в течение такта Г1 информационное слово, установленное на втором выходе блока 1, будет передано. По этой логической 1 блок 1 формирует в момент действия заднего фронта импульса Г1 для преобразователя 7 сигнал, по которому он устанавливает : на своем выходе вторую половину передаваемого информационного слова. Таким образом, в момент действия импульса Г1 по линии 11 передается первая половина информационного слова, а во время паузы импульсов серии Г1вторая.

Триггер 3 находится в состоянии логической 1 по крайней мере в течение длительности такта серии импульсов Г1. В течение этого времени в линию 8 поступает импульс Г2, а в линию 9 - импульс ГЗ. Импульс Г2 линии 8 сопровождает первую половину информационного слова, передаваемого по линии 11, а импульс ГЗ в линии 9вторую. Импульс Г2 из линии 8 поступает в блок 18 и записывает туда первую половину информационного слова, импульс ГЗ из линии 9 поступает в блок 19 и записывает туда вторую половину информационного слова.

Адрес ячейки, по которому информационное слово записывается в блоки 18, 19, формируется счетчиком 14 и хранится в течение времени записи информации в регистрах 15, 16. Предположим, что в исходном состоянии содержимое счетника 14 и регистров 15, 16 равно нулю. При передаче первой половины слова в линии 8 действурт импульс Г2, КОТОРЫЙ увеличивает содержимое счетчика 14 на единицу. Этот же импульс записывает в блок 18 в ячейку с номером О первую половину информационного слова, так как содержимое регистра 15 во время записи равно нулю, и .перезаписывает нуль из регистра 15 в регистр 16. При передаче второй половины слова в линии 9 действует импульс ГЗ, который запи0сывает в. регистр 15 содержимое счетчика 14 (в рассматриваемом примере в регистр 15 записывается единица) и записывает в блок 19 в ячейку с номером О вторую половину информаци5онного слова. Таким образом, информационное слово будет записано в ячей..ки с номером О. При записи следующего информационного слова будет занята ячейка с номером 1, затем с

0 номером 2 и т.д. Максимальное показание счетчика 14 равно максимальному количеству ячеек памяти в блоке

18(19).

Адрес ячейки блоков 18, 19, по

5 которому считывается информация, форNSHpyeTCH на первых входах блоков 18, 19. Считывание информации из блоков 18, 19 происходит в таком же порядке, как и запись, т.е. первоначально считывается содержимое ячеек с номеDром О, затем с номером 1 и т.д., если только предварительно в них была записана информация. При работе устройства возможны следующие ситуации. Адрес считывания в данный момент

5 времени отличается от адреса записи. Это говорит о том, что в блоках 18,

19имеются свободные ячейки, куда может быть записана новая информация. На выходе сумматора -17 формируется

0 логическая 1, которая через элемент ИЛИ 12 поступает в линию 10 и разрешает передачу следующего информационного слова. В другой ситуации -адрес записи и адрес считывания совпадают. Это происходит, когда блоки 18, 19

5 совершенно свободны (количество записанных информационных слов равно количеству считанных слов), или когда блоки 18, 19 полностью заняты (количество считанных слов было недостаточ0ным и все ячейки блоков 18, 19 заполнились информацией). Если при одинаковых адресах записи и считывания блоки 18, 19 свободны, то это означает, что считывание информации во вре5мени произошло позже, чем запись. И наоборот, если запись производилась позже, чем считывание, то блоки 18,

19 будут полностью заняты. Триггер 13 запоминает, что было последним,

0 запись или считывание. Если последним было считывание, то триггер 13 устанавливается в состояние логической 1, эта логическая 1 поступает через элемент ИЛИ 12 в линию 10 разрешает переда,чу информации. Ко05

да триггер 13 находится в состоянии логического О при одинаковых адресах записи и считывания, то блоки 18, 19 полностью заняты, на входах элемента ИЛИ 12 логические О, а в линии 10 формируется сигнал, запрещающий передачу информации.

Когда в линии 10 формируется запрещающий передачу информации сигнал на выходе элемента И б логический О, триггер 3 остается в состоянии логического О и запрещает передачу в линиях 8, 9 сигналов соответственно фаз Г2, ГЗ, а также указывает блоку-1, что подготовленное для передачи информационное слово еще не передано. Блок 1 продолжает удерживать на своем втором выходе информационное слово, а на третьем выходе логическую 1, пока из линии 10 не поступил сигнал разрешения передачи и триггер 3 не переключится в логическую 1) .

По сравнению с известным устройством информативность данного устройства увеличена. 3 известном устройстве один машинный такт используется для записи информации, представленной параллельным кодом в преобразователь параллельного кода, в последовательный, во втором такте формируется стробирующий сигнал, сопровождающий по линиям связи первую половину информационного слова, в третьем такте формируется второй стробирующий сигнал, сопровождающий по линиям связи вторую половину информационного слова. Таким образом, на передачу одного информационного слова тратится три машинных такта. В предлагаемом устройстве на передачу одного информационного слова тратится два такта, в первом такте осуществляется запись информации в преобразователь 7 и в линии 8 формируется первый стробирующий сигнал, во втором такте осуществляется .выдача в линию Э второго стробирующего сигнала и на втором выходе блока 1 подготавливается для передачи следуюцее информационное слово. Поскольку для передачи информационного слова на передающей стороне тратится меньшее количество машинных тактов, то информативность предлагаемого устройства будет выше, т.е. за один и тот же интервал времени будет передано большее число информационных слов.

В предлагаемом устройстве по сравнению с известным уменьшена задержка передачи информации. В известном устройстве задержка передачи больше, так как с момента записи информации в параллельно-последовательный преобразователь до момента формирования первого стробирующего импульса в линии связи проходит такт машинного j времени. В предлагаемом устройстве эта задержка устранена. В известном

устройстве информационное слово задерживается с приемной стороны на один такт, который тратится на перезапись информации из. последовательно-парс1ллельного преобразователя в блок памяти. В предлагаемом устройстве эта процедура перезаписи отсутствует, а формирование параллельного кода, подлежащего дальнейшей обработке, происходит непосредственно в блоках памяти, т.е. повышается быстродействие устройства.

Формула изобретения

Устройство для передачи и приема информации, содержащее на передающей стороне блок управления, первый выход которого соединен с первым входом триггера, выход триггера соединен с первым входом первого элемента И, выход которого подключен к первой ли-нии связи, второй выход блока управления через преобразователь параллельного кода в последовательный подключен к второй линии связи, на приемной стороне - счетчик, вход которого подключен к первой линии связи, триггер, выход которого соединен с первым входом элемента ИЛИ, подключенного к третьей линии связи, и первый блок памяти, о т л и ч ающвес я тем, что, с целью повышения информативности и быстродействия устройства, в Него введены четвертая линия связи, на передающей cfopOHe формирователь импульсов, второй и третий элементы И, вход формирователя импульсов соединен с первым выходом блока управления, первый выход с вторым входом первого элемента И, второй выход - с первым входом второго элемента И, выход которого подключен к четвертой линии связи, второй вход второго элемента И объединен с входом блока управления и подключен к выходу триггера, третий выход блока управления соединен с первым входом третьего элемента И, второй вход которого подключен к третье линии связи, выход соединен с вторым входом первого триггера, на приемной стороне введены регистры адреса, второй блок памяти и сумматор по модулю два, выход которого соединен с вторым входом элемента ИЛИ, первый вход сумматора по модулю два объединен с первыми входами первого и второго блоков памяти, вторые входы которых объединены и подключены к второй линии связи, третий вход второго блока памяти объединен с первым входом первого регистра адреса и входом триггера и подключен к четвертой линии

связи, третий вход первого блока памяти объединен с первым входом второго регистра адреса и подключен к первой линии связи, выход счетчика

соединен с объединенными вторыми яходами второго регистра адреса и сумматора по модулю два, выход первого регистра адреса соединен с четвертым входом первого ОлЬка памяти и вторым входом второго регистра адреса, выход которого соединен с четвертым входом второго блока памяти.

Источники информацииг принятые во внимание при экспертизе

. Авторское свидетельство СССР 499677, . кл. Н 04 В З/5О, 1973.

2.Акцептованная заявка Япония

50-24565, кл. С 06 F 11/00, опублик. 1975.

3.Авторское свидетельство СССР по заявке 2883078/18-24,

кл. G 08 С 19/28, 1978 (прототип).

н

i

t

м:

г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Устройство для задержки цифровой информации с уплотнением | 1987 |

|

SU1425632A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Стохастический преобразователь | 1984 |

|

SU1241239A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

Ч;

I

г

. е

л

1

/ Г/Х

/

L

.

.LTl-J

иг.г

Авторы

Даты

1981-12-07—Публикация

1980-03-21—Подача