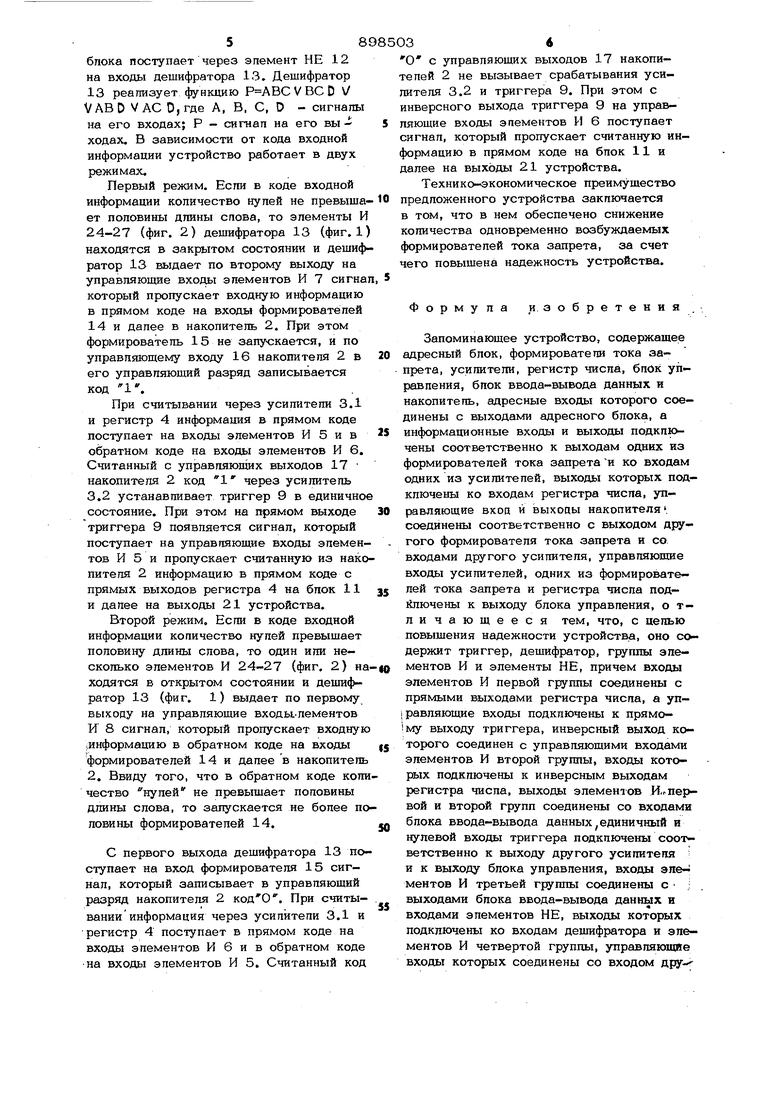

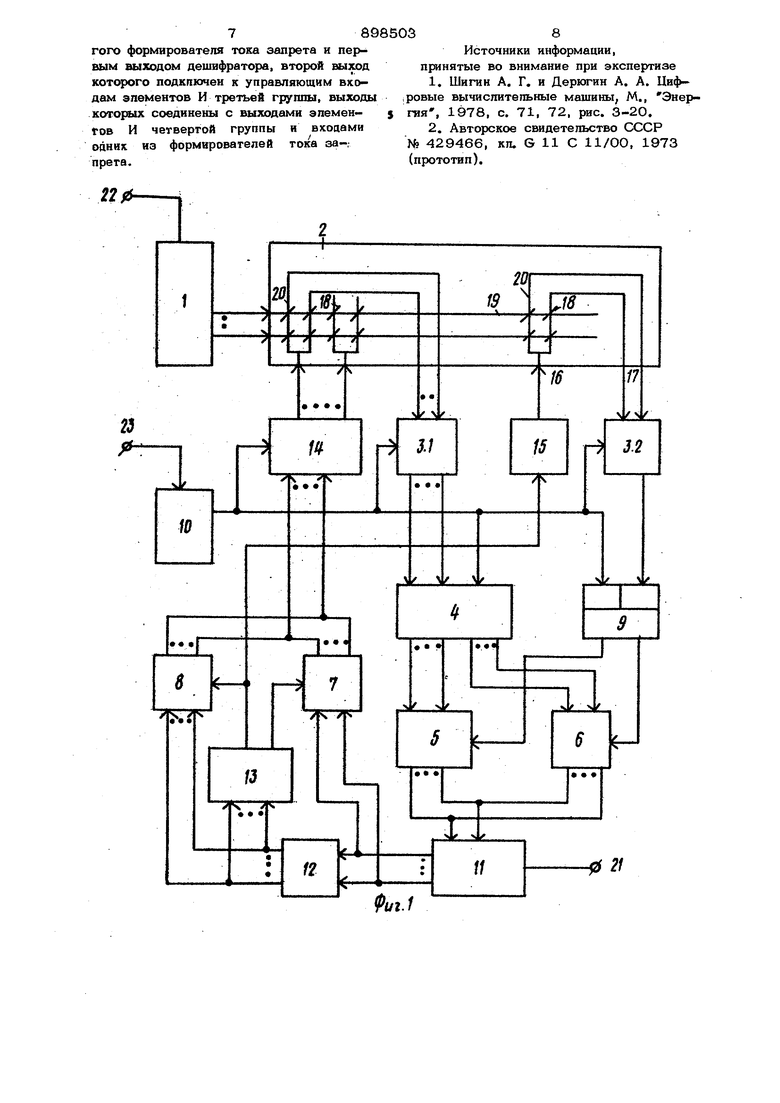

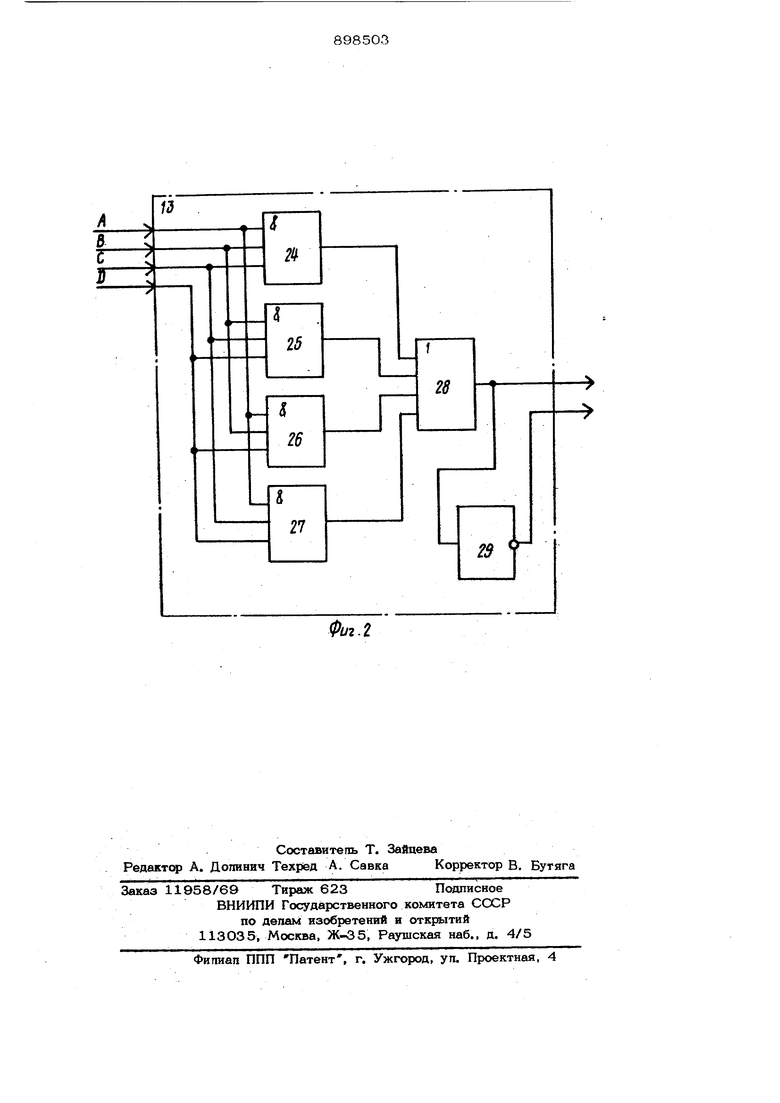

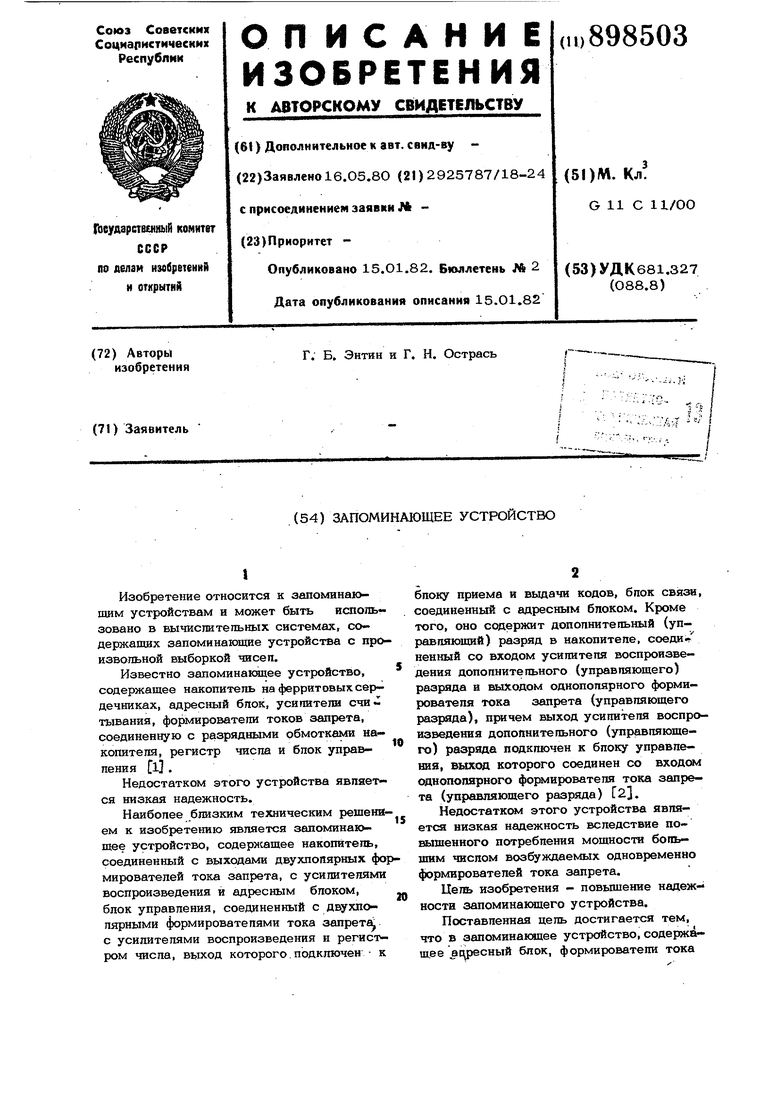

Изобретение относится к запомннающим устройствам и может быть испопьзовано в вычиспитепьных системах, содержащих запоминающие устройства с про извольной выборкой чисел. Известно запоминакяцее устройство, содержащее накопитель на феррит овых сердечниках, адресный блок, усиггатепи считывания, формирователи токов запрета, соединенную с разрядными обмотками накопителя, регистр числа и блок управления l . Недостатком этого устройства является низкая надежность. Наиболее близким техническим решением к изобретению является запоминахощее устройство, содерясащее накопитель, соединенный с выходами двухпопярных фо мирователей тока запрета, с усилителями воспроизведения и адресным блоком, блок управления, соединенный с двухполярными формирователями тока запрета с усилителями воспроизведения и регис-гром числа, выход которого.подключен к блоку приема и выдачи кодов, блок связи, соединенный с адресным блоком. Кроме того, оно содержит дополнительный (управляющий) разряд в накопителе, соеди ненный со входом усилителя воспроизведения дополнительного (управляющего) разряда и выходом однопопярного формирователя тока запрета (управляющего разряда), причем выход усилителя воспроизведения дополнительного (управляющего) разряда подключен к блоку управления, выход которого соединен со входсм однопопярного формирователя тока запрета (управляющего разр5ща) Г2. Недостатке этого устройства является низкая надежность вследствие повыщенного потребления мощности бопьщим числом возбуждаемых одновременно формирователей тока запрета. Цель изобретения - повьпиение надежности запоминакнцего устройства. Поставленная цель достигается тем, что в запоминакмдее устрюйство, содержа- щ.ее с ресный блок, формирователи тока запрета, усилители, регистр числа, блок управления, блок ввода-вывода данных и накопитель, адресные входы которого соединены с выходами адресного блока, а информационные входы и выходы подключены соответственно к выходам одних из формирователей тока запрета и ко входам одних из усилителей, выходы которых подключены ко входам регистра числа, управляющие вход и выходы накоп теля соединены соответственно с выходом другого формирователя тока запрета и со входами другого усилителя, управляющие входы усилителей, одних из формирователей тока запрета и регистра чис на подключены к выходу блока управлени введены триггер, дешифратор, группы эле ментов И. и элементы НЕ, причем входы элементов И первой группы соединены с прямыми выходами регистра числа, а управляющие входы подключены к прямому выходу триггера, инверсный выход ко торого соединен с управляющими входами элементов И второй группы, входы ко торых подключены к инверсным выходам регистра числа, выходы элементов И первой и второй групп соединены со входами блока ввод-вывода данных, единичный и нулевой входы триггера подключены соответственно к другого усипителя и к выходу блока управления, входы элементов И третьей группы соединены с выходами блока ввода-вывода данных и входами элек ентов НЕ, выходы которы подключены ко входам дешифратора и эле ментов И четвертой группы, управляющие входы которых соединены со входом другого формирователя тока запрета и первым выходом дешифратора, второй выход которого подключен к управляющим входам элементов И третьей группы, выходы которых соединены с выходами элементов И четвертой группы и входами одних из формирователей тока запрета. На фиг, 1 изображена функциональная схема предложенного устройства; на фиг. 2 - пример выполнения функциональной схемы дешифратора для запоминающего устройства на четыре разряда. Устройство (фиг. 1) содержит адресный блок 1, накопитель 2, усилители 3.1 и 3.2, регистр 4 числа, первую 5, вторую 6, третью 7 и четвертую 8 группы элементов И, триггер 9, блок 1О управления, блок 11 ввода-вывода данных, элементы НЕ 12, дешифратор 13 и формирователи 14 и 15 тока запрета, На фиг. 1 обозначены управляющие вход 16 и выходы 17, ферритовые сердечники 18 адресные 19 и разрядные 20 шины нако пителя, а также информационные входы (и выходы) 21, адресные 22 и управляющие 23 входы устройства. Входы элементов И 5 соединены с прямыми выходами регистра 4, а управляющие входы подключены к прямому выходу триггера 9. Инверсный выход триггера 9 соединен с управгшющими входам- ми элементов И 6, входы которых подключены к инверсным выходам регистра 4. Выходы элементов И 5 и 6 соединены со входами блока 11. Единичный и нулевой входы триггера 9 подключены соответственно к выходу усилителя 3.2 и к выходу блока 10. Входы элементов И 7 соединены с выходами блока 11 и входами элементов НЕ 12, выходы которых подключены ко входам дешифратора 13 и элементов И 8. Управляющие входы элементов И 8 соединены со входом формирователя 15 и первым выходом дешифратора 13, второй выход которого подключен к управляющим входам элементов И 7. Выходы элементов И 7 и 8 соединены со входами формирователей 14. Дешифратор 13 содержит (фиг. 2) элементы И 24-27, элемент ИЛИ 28 и элемент НЕ 29. Выходы элементов И 24-27 соединены соответственно со входами элемента ИЛИ 28, выход которого подключен ко входу элемента НЕ 29. Первый вход первого элемента И 24 соединен с первыми входами третьего 26 и четвертого 27 элементов И и является первым входом дешифратора 13. Второй вход элемента И 24 подключен к первому входу второго 25 и второму входу третьего 26 элементов И и является вторым входом дешифратора 13. Третий вход элемента И 24 соединен со вторыми входами второго 25 и четвертого 27 элементов И и является третьим входом дешифратора 13. Третьи входы второго i 25, третьего 26 и четвертого 27 элементов И являются четвертым входом дешифратора 13. Выходы элемента НЕ 29 и элемента ИЛИ 28 являются соответственно первым и вторым выходами дешифратора 13. На фиг. 2 обозначены сигналы А, В, Си D на входах дешифратора. Устройство работает следующим образом. В исходном состоянии регистр 4 и триггер 9 находятся в нулевом состоянии. При записи на входы блока 11 со входов устройства 21 поступает входная информация,, которая с выходов этого

блока поступает через элемент НЕ 12 на входы дешифратора 13. Дешифратор

13реаггазует функцию P ABCVBCD V VABD VAC О, где А, В, С, D - сигналы

на его входах; Р - сигнал на его вы ходах. В зависимости от кода входной информации устройство работает в двух режимах.

Первый режим. Если в коде входной информации количество нулей не превышает половины длины спова, то элементы И 24-27 (фиг. 2) дешифратора 13 (фиг. 1) находятся в закрытом состоянии и деши ьратор 13 выдает по второму выходу на управляющие входы элементов И 7 сигнал который пропускает входную информацию в прямом коде на входы формирователей

14и далее в накопитель 2. При этом формирователь 15 не запуч:кается, и по управляющему входу 16 накопитета 2 в его управляющий разряд записывается

код I.

При считывании через усилители 3.1 и регистр 4 информация в прямом коде поступает на входы элементов И 5 и в обратном коде на входы элементов И 6. Считанный с управляющих выходов 17 накопителя 2 код 1 через усилитель 3,2 устанавливает триггер 9 в единичное состояние. При этом на прямом выходе триггера 9 появляется сигнал, который поступает на управляющие входы элементов И 5 и пропускает считанную из накопителя 2 информацию в прямом коде с прямых выходов регистра 4 на блок 11 и далее на выходы 21 устройства.

Второй режим. ЕС пи в коде входной информации количество нулей превышает noHOBHiiy длины слова, то один или несколько элементов И 24-27 (фиг. 2) находятся в открытом состоянии и дешифратор 13 (фиг. 1) выдает по первому выходу на управляющие входы-лементов И 8 сигнал, который пропускает входную информацию в обратном коде на входы формирователей 14 и далее в накопитель 2. Ввиду того, что в обратном коде количество нулей не превышает половины длины слова, то запускается не более половины формирователей 14.

С первого выхода дешифратора 13 поступает на вход формирователя 15 сигнал, который записывает в управляющий разряд накопителя 2 кодО. При считыванииинформация через усилители 3.1 и регистр 4 поступает в прямом коде на входы элементов И 6 и в обратном коде на входы элементов И 5. Считанный код

О с управляющих выходов 17 накопителей 2 не вызывает срабатывания усилителя 3.2 и триггера 9. При этом с инверсного выхода триггера 9 на управляющие входы элементов И 6 поступает сигнал, который пропускает считанную иформацию в прямом коде на блок 11 и далее на выходы 21 устройства.

Технико-экономическое преимущество предложенного устройства заключается в том, что в нем обеспечено снижение количества одновременно возбуждаемых формирователей тока запрета, за счет чего повышена надежность устройства.

Формула и.зобретения

Запоминающее устройство, содержащее адресный блок, формирователи тока запрета, усилители, регистр числа, блок управления, блок ввода-вывода данных и накопитель, адресные входы которого соединены с выходами адресного блока, а информационные входы и выходы подключены соответственно к выходам одних из формирователей тока запрета и ко входам одних из усилителей, выходы которых подключены ко входам регистра числа, управляющие вход и выхоцы накопителя соединены соответственно с выходом другого формирователя тока запрета и со входами другого усилителя, управляющие входы усилителей, одних из формирователей тока запрета и регистра числа под- йлючены к выходу блока управления, отличающееся тем, что, с целью повышения надежности устройства, оно содержит триггер, дешифратор, группы элементов И и элементы НЕ, причем входы элементов И первой группы соединены с прямыми выходами регистра числа, а уп равляющие входы подключены к прямо му выходу триггера, инверсный выход которого соединен с управляющими входами элементов И второй группы, входы которых подключены к инверсным выходам регистра числа, выходы элементов И,первой и второй групп соединены со входами блока ввода-вывода данных,единичный и нулевой входы триггера подключены соответственно к выходу другого усилителя и к выходу блока управления, входы эле-i ментов И третьей группы соединены с i выходами блока ввода-вывода данных и входами элементов НЕ, выходы которых подключены ко входам дешифратора и элементов И четвертой группы, управляющие входы которых соединены со входом друтого формирователя тока запрета и первым выходом дешифратора, второй выход которого подкпючеи к управляющим входам элементов И третьей группы, выходы которых соединены с выходами элеменгов И чегвергой группы и входами одних из формирователей тока за-, прега.

Источники информации, принятые во внимание при экспертизе

1.Шигин А. Г. и Дерюгин А. А. Циф.ровые вычислительные машины, М., Энергия, 1978, с. 71, 72, рис. 3-20.

2.Авторское свидетельство СССР N9 429466, кл. G 11 С 11/00, 1973 (прототип).

Фиг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1981 |

|

SU985830A1 |

| Запоминающее устройство | 1980 |

|

SU940235A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Магнитное оперативное запоминающее устройство | 1983 |

|

SU1129654A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Многоканальное оперативное запоминающее устройство | 1987 |

|

SU1432606A1 |

| Резервированное многоканальное запоминающее устройство | 1980 |

|

SU942142A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149317A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

Авторы

Даты

1982-01-15—Публикация

1980-05-16—Подача