(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU900437A2 |

| Следящий аналого-цифровой преобразова-ТЕль | 1979 |

|

SU828401A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU907794A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU900438A2 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU805489A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1003331A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU892702A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU924852A1 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1184090A1 |

I

Предлагаемое устройство относится к аналого-1Щфровым преобразователям (АЩ1)и может быть использовано в связи, вычислительной и измерительной технике а также в автоматизированных системах управления технологическими процессами и системах автоматизации научных исследований.

Известен поразрядный АЦП, содержаощй схему сравнения, цифро-аналоговый преобразователь, источник опорного сигнала, импульсов, триггер со схемой И и блок, реали-. зующий поразрядный метод (ВРЕ одержащий регистр и группу схем И. ;

Недостатками данного А1Щ .является низкая вероятность правильного ответа, обусловленная тем, что общее число испытаний распределяется равномерно межру всеми перебираемыми образцовыми уровнями независимо от взаимиого расположения текущего образцррого уровня и входного |Сигнал ч низкое быстродействие, обусловленное частыми переключениями образцовых уровней.

Цель изобретения - повышение вероятности правильного ответа и уменьшение времени получения результата.

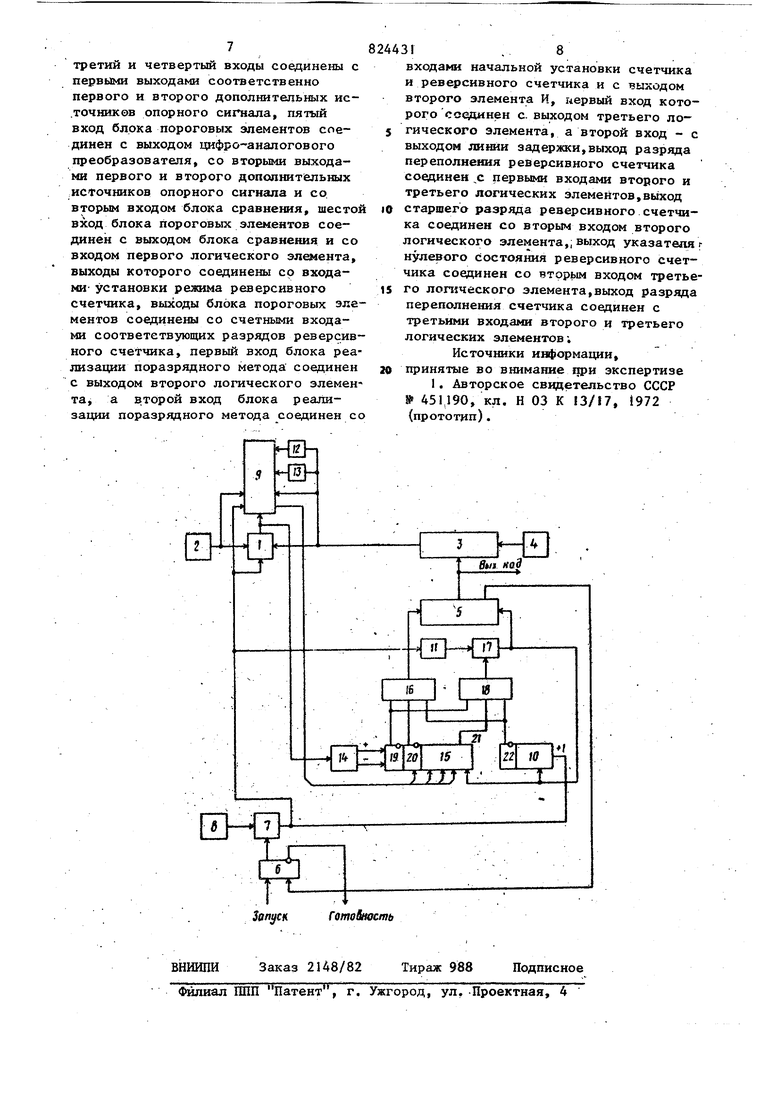

Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий блок сравнения, первый вход которого соединен с выходом источника входного сигнала, а второй выход соединен с выходом цифроаналогового преобразователя, аналого вый вход которого соединен с выходом источника опорного сигнала, а цифровые входы - с соответствухнцими информационными выходами блока реализации поразредного метода, выход Конец работы которого соединен с нулевы входом триггера, нулевой выход которого соединен с шиной Готовность а единичный вход триггера соединен с . шиной Запуск, единичный выход тригг гера соединен с первым входсм перйог элемента И, второй вход которого 3 соединен с выходом генератора импуль сов, выход первого элемента И соединен со входом опроса блока сравнения дополнительно введены блок пороговых элементов, два дополнительных источника опорного сигнала, счетчик, реверсивный счетчик,-три логических элемента, линия задержки, второй эле мент И, причем первый вход блока пороговых элементов соединен с выходом первого элемента И, со счетным входом счетчика, со входом опроса блока сравнения и со входом линии задержки второй вход - с выходом источника входного сигнала; третий и четверил входы с первыми выходами соответст венно первого и второго дополнительных источников опорного сигнала; пятый - с выходом цифро-аналогово го преобразователя, со вторыми выходами первого и второго дополнитель ных источников опорного сигнала и со вторым входом блока сравнения; шестой вход блока пороговых элементов соединен с выходом блока сравнения и со входом первого логического элемента, выходы которого соединены со входами установки режима деверсив ного счетчика, выходы блока пороговых элементов соединены со счетными входами соответствующих разрядов реверсивного счетчика, первый вход блока реализации поразрядного метода соединен с выходом второго логического элемента, а второй вход блока реализации поразрядного метода соединен со входами начальной установки счетчика и реверсивного счетчика и с выходом второго элемента И первый вход которого соединен с выходом третьего логического элемента, а второй вход - с выходом линии задержки, выход разряда переполнения реверсивного счетчика соединен с первыми входами второго и третьег логических элементов, выход старшег.о разряда реверсивного счетчика соединен со вторым входом второго логического элемента, выход указа-, теля нулевого состояния реверсивного счетчика соединен со вторым вх дом третьего логического элемента; выход .разряда переполнения счетчика соединеа-с третьими входами второго и третьего логического элементов. На чертеже представдена функциональная схема аналого-цифрового пре образователя. 14 Предлагаемый аналого-цифровой преобразователь (фиг.1)содержит схему 1 сравнения, первый вход которой соединен с выходом источника 2 входного сигнала, а второй вход - с выходом цифро-аналогового преобразователя (ЦАП 3, аналоговый вход которого соединен с выходом источника 4 опорного сигнала, а цифровые входы ЦАП соединены с соответствующими информационными выходами блока реализации поразрядного метода БРПМ) 5, выход Конец работы БРПМ 5 соединен с нулевым входом триггера 6, нулевой выход которого соединен с шиной Готовность, единичный вход триггера 6 соединен с шиной Запуск, а единичный выход триггера 6 соединен с первым входом первого элемента И 7, второй вход которого соединен с выходом генератора 8 импульсов, выход первого элемента И 7 соединен со входом опроса схемы 1 сравнения, с первым входом блока пороговых элементов (БПЭ)9, со счетным входом счетчика 10 и со входом линии И задержки; второй вход БПЭ 9 соединен с выходом источника 2 входного сигнала третий и четвертый входы БПЭ 9 соединены с первыми выходами соответственно первого.12 и второго 13 дополнительных источников опорного сигнала; пятый вход БПЭ..9 соединен с выходом ЦАП 3 и со вторыми выходами первого 12 и второго 13 дополнительных источников опорного сигнала; шестой вход БПЭ 9 соединен с выходом блока I сравнения и со входом первого логического элемента(ЛЭ) 14, выкор л которого соединены со входами установки режима реверсивного счетчика 15, выходы БПЭ 9 соединены со счетными входами соответствующих разрядов реверсивного счетчика 15; первый вход БРПМ 5 соединен с выходом второго ЛЭ 16, а второй вход БРПМ 5 соединен со входами на51альной установки счетчика 10 и реверсивного счетчика 15 и с выходом второго элемента И 17, первый вход которого соединен с выходом третьего ЛЭ 18, а второй вход - с выходом линии П задержки; выход разряда 19 переполнения реверсивного счетчика 15 соединен с первыми входами второго 16 и третьего 18 логических элементов; выход старшего разряда 20 реверсивного счетчика 15 соединенсо вторым входом второго ЛЭ 16; выход 21 ука ателя нулевого состояния реверсивного счетчика 15 соединен со вторым входом третьего ЛЭ 18; выход 22 разряда переполнения счетчика 10 соединен с третьими входами второго 16 и третьего 18 ЛЭ. . АЦП работает следующим образом.

В начале работы в счетчике 10 устнавливается код 0...0, в реверсивном счетчике 15 - код 010....(5, т. е. устанавливается 1 в старший разряд а все остальные раэряды, в том числе И..разряд переполнения, .сбрасываются ,j в БРПМ 5 устанавливается код 10...0. С приходом сигнала Запуск триггер 6 устанавливается в 1, и первь1Й импульс от генератора 8 импульсов проходит через элемент И 7 и опрашивает схему 11 сравнения и БПЭ 9. €игнал с блока 1 сравнения устанавливает режим работы реверсивного счетчика значение вход4ого сигнала меньше образцового , то устанавливается режим сложения а БПЭ 9 подает сигнал на счётный вход соответствующего разряда реверсивного счетчика 15. Чем больше разница текущего знач.ения сигнала и образцового уровня, снимаемого с ЦАП -ЗУ тем на более ст&рший разряд реверсивного счетчика 15 подается сигнал с БПЭ 9. Процесс изменения содержимого реверсивного счетчика 15 продолжается либо до переполнения счетчика 10, т. е. до истечения максимального времени, отведенного на испытания при одном образцовом уровне, либо до переполнения или обнуления реверсивного счетчика 15. При зтом появляется сигнал , t на выходе TpejTbero ЛЭ 18, гдеП - сигнал переполнения 19 реверсивного счетчика 15; О - признак нулевого содержимого

реверсивного счетчика 15; IQ- сигнал переполнения 22 счетчика 10,

Задержанный на линии II задержки сигнал от генератора 8 импульсов проходит через второй элемент И 17 на БРПН 5, в результате чего устанавливается проверочная единица в более младший разряд кодового эквивалента, и в зависимости от наличия сигнала на выходе второго ЛЭ 16 гасится или нет текущий разряд кодового эквивалента, т. е. реализуется очередной такт к лассического поразрядного метода. Кроме этого, сигнал с выхода

второго элемента И 17 устанавливает начальные состояния на реверсивном счетчике 15 (010.,..0) и счетчике 10 (о....о). И начинается новый

цикл определения следующего разряда кодового эквивалента. После определения значения последнего разряда кодового эквивалента РПМ 5 вьщает сигнал Конец работы, который га.сит триггер 6, тем самым форишруетсй сигнал Готовность.

Использование последовательного анализа при сравнении с каждым об)азцовым уровнем позволяет повысить

вероятность правильного ответа в зависимости от эида и величины помехи при сокращении времени получения результата.

20

Формула изобретения

Анало,го-цифровой преобразователь, содержащий блок сравнения, первый вход которого соединен с выходом источника входного сигнала, а второй вход соединен с выходом цифро-аналогового- преобразователя, аналоговый вход которого соединен с выходом источника опорного сигнала, а цифро0вые входы с соответствующими информационными выходами блока реализации поразрядного метода, выход Конец работы которого соединен с нулевым

входом триггера, нулевой выход коsторого соединен с шиной Готовность, единичный вход триггера соединен с шиной Запуск, а единичный выход триггера.соединен с-первым вхо- дом первого элемента И, второй

0 вход которого соединен с выходом генератора импульсов, выход первого элемента И соединен со входом опроса блока сравнения, отличающийся тем, что, с целью повы5шения вероятности правильного ответа и уменьшения времени гголучения результата, Б него введены блок пороговых элементов, два дополнительных источника опорного сигнала, счетчик,

0 реверсивный счетчик, три логических элемента, линия задержки, второй элемент И, причем первый вход блока пороговых элементов соединен с выходсш первого элемента И, со счетным вхо-

5 дом счетчнЕка, со входом опроса блока сравнения и со входом линии.задеря ки, второй вход соединен с выходом источника входного сигнала.

Авторы

Даты

1981-04-23—Публикация

1979-07-16—Подача