(54) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU900437A2 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1003331A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU824431A1 |

| Следящий аналого-цифровой преобразова-ТЕль | 1979 |

|

SU828401A1 |

| Следящий аналого-цифровой преобразователь | 1979 |

|

SU799129A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU907795A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU924852A1 |

| Следящий аналого-цифровой преобразователь | 1978 |

|

SU780184A1 |

| Устройство для измерения времени установления выходного напряжения цифро-аналогового преобразователя | 1976 |

|

SU603121A1 |

I

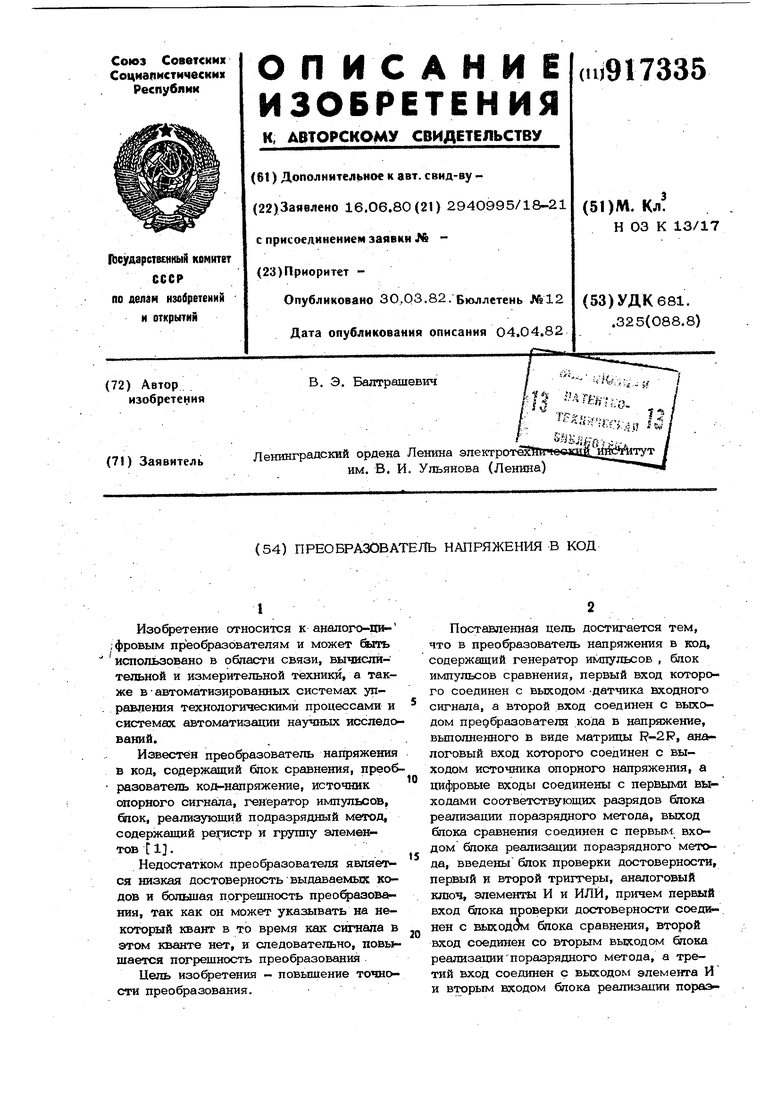

Изобретение относится к аналого-ци;фровым преобразователям и может бкггь испол1зЗовано в области связи, вычислительной и измерительной тёхникИ| a также в автоматизированных системах управления технологическими процессами и системах автоматизации научных исследований.

Известен преобразователь напряжения в код, содержащий блок сравнения, преобразователь код-напряжение, источник сшорного сигнала, генератор импульсов, бпок, реализующий подразрядный метод, содержащий реестр и группу элемвн тов 1.

Недостатком преобразователя являет оя низкая достоверность выдаваемых кодов и большая пргрещность преофазования, так как он может указывать на некоторый квант в то время как в этом кванте нет, и следовательно, повышается погрешность преобразования .

Цель изобретения - повышение точности преобразования.

Поставленная цель достигается тем, что в преобразователь напряжения в код, содержащий генератор импульсов , блок импульсов сравнения, первый вход которого соединен с выходом -датчика входного сигнала, a второй вход соединен с выходом предбразователн кода в напряжение, вьшолнеиного в виде матрицы R-2R, аналоговый вход которого соединен с выходом источника опорного напряжения, a

10 цифровые входы соединены с первыми В1 ходами соответствующих разрядов блока реализации поразрядного метода, выход блока сравнения соединен с первым входом блока реализации поразрядного мето15да, введены блок проверки достоверности, первый и второй триггеры, аналоговый ключ, элементы И и ИЛИ, причем первый вход блока цроверки достоверности соединен с выходс5м блока сравнения, второй

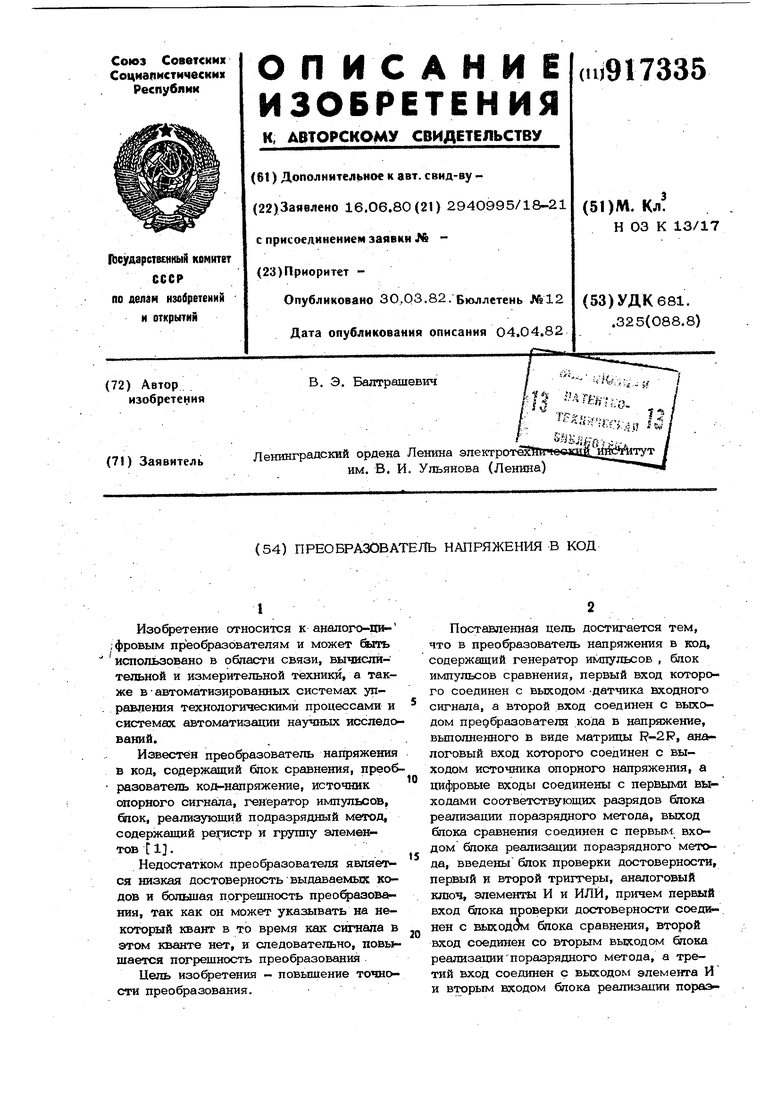

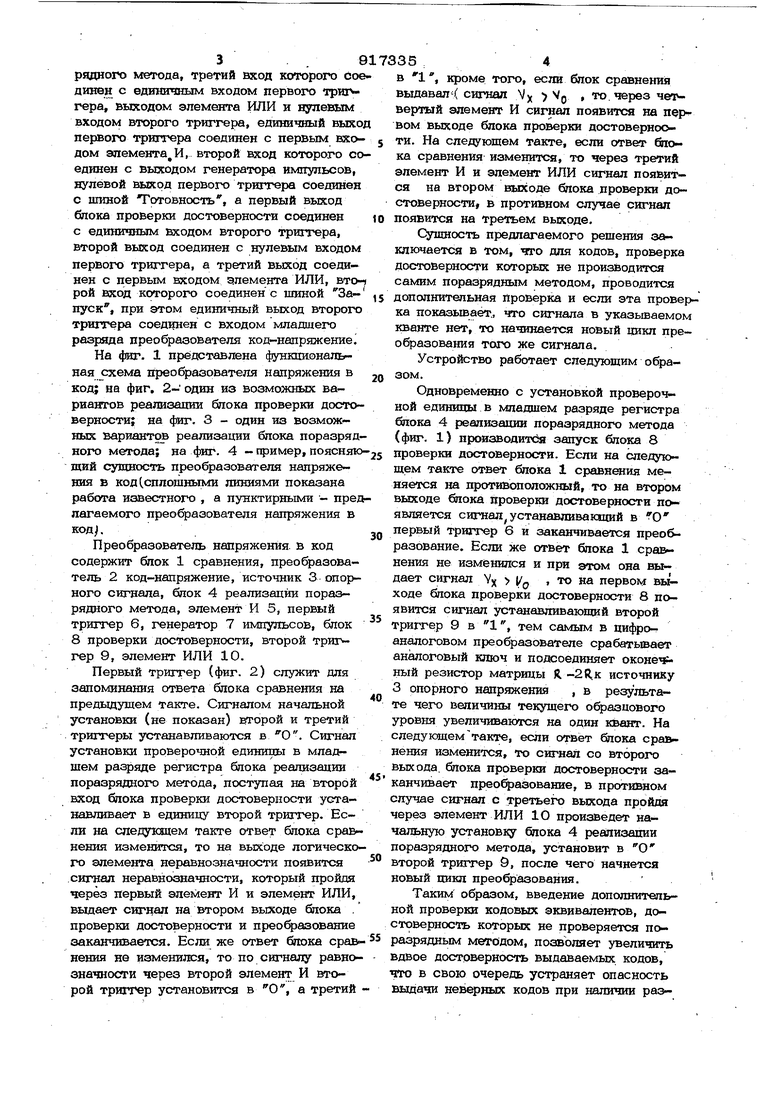

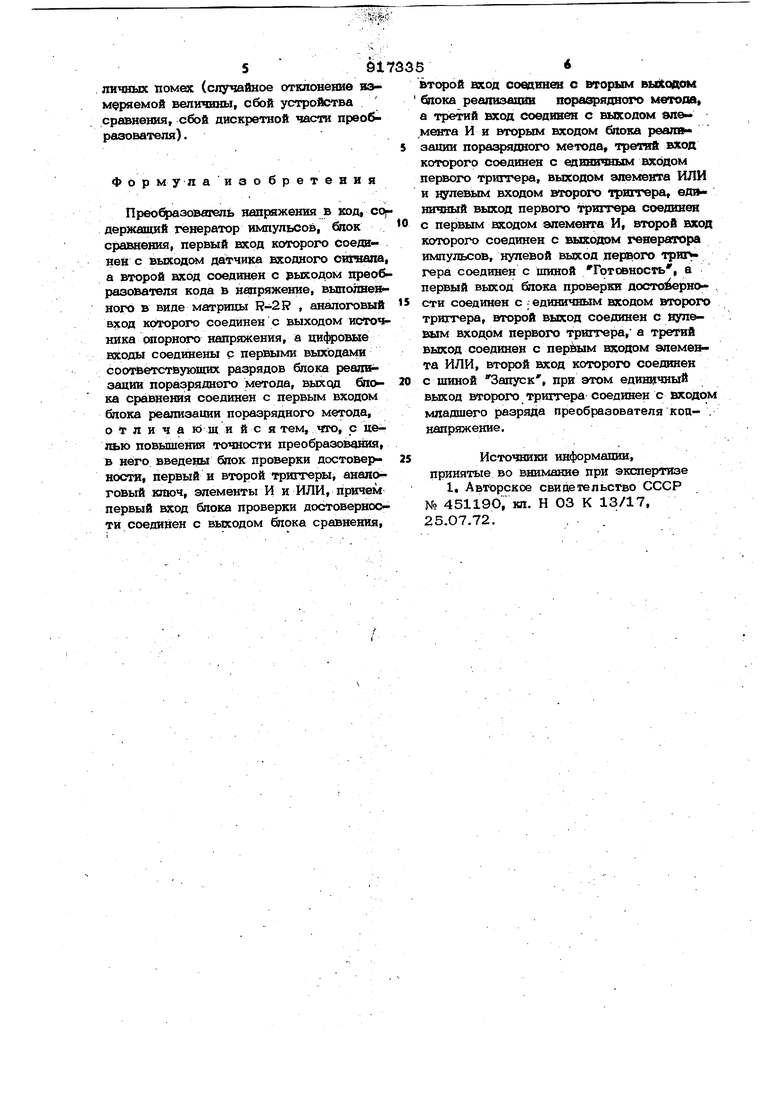

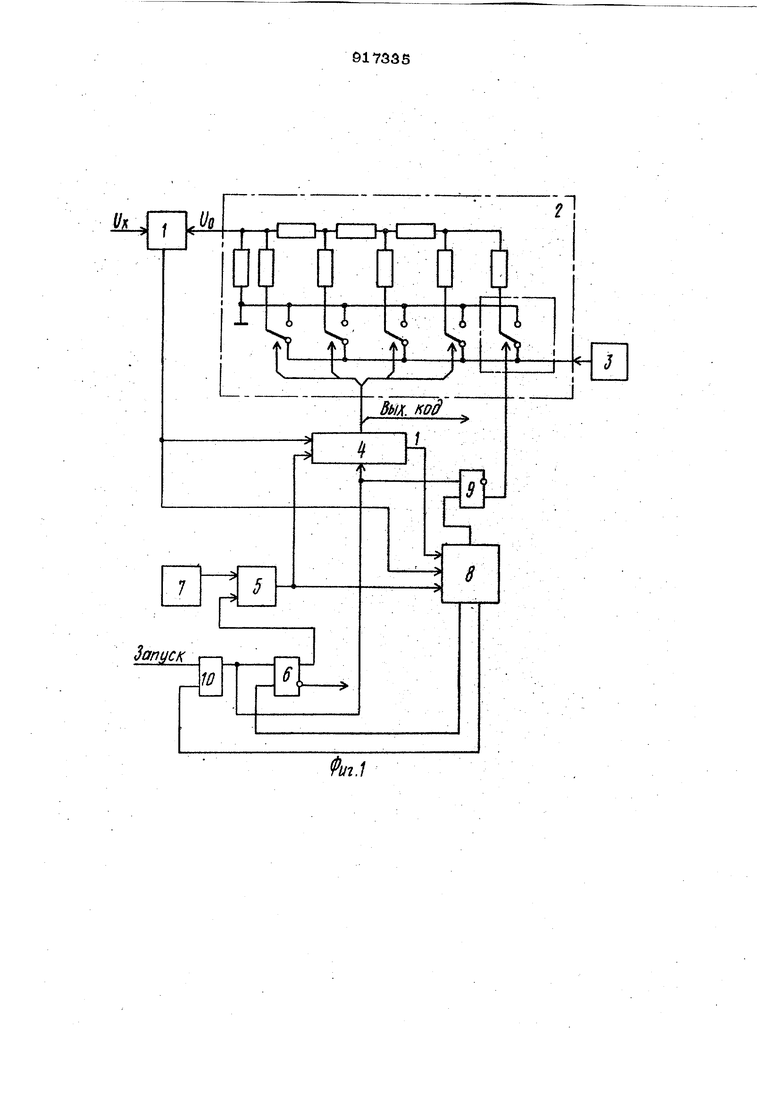

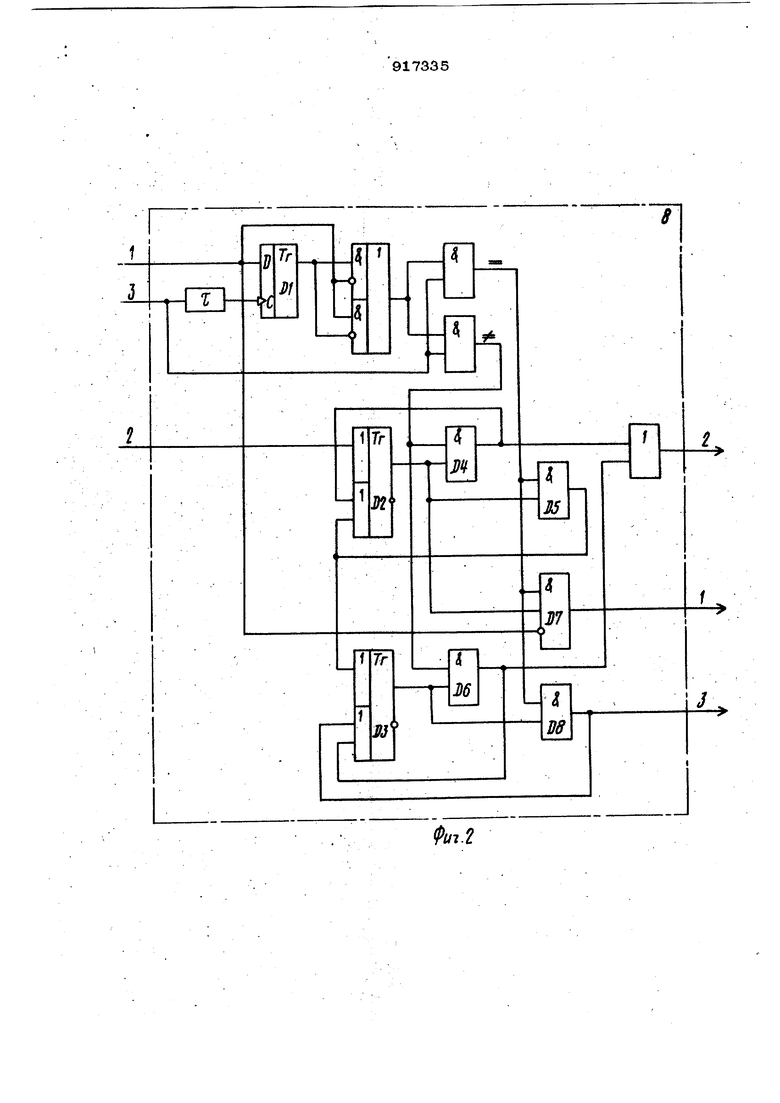

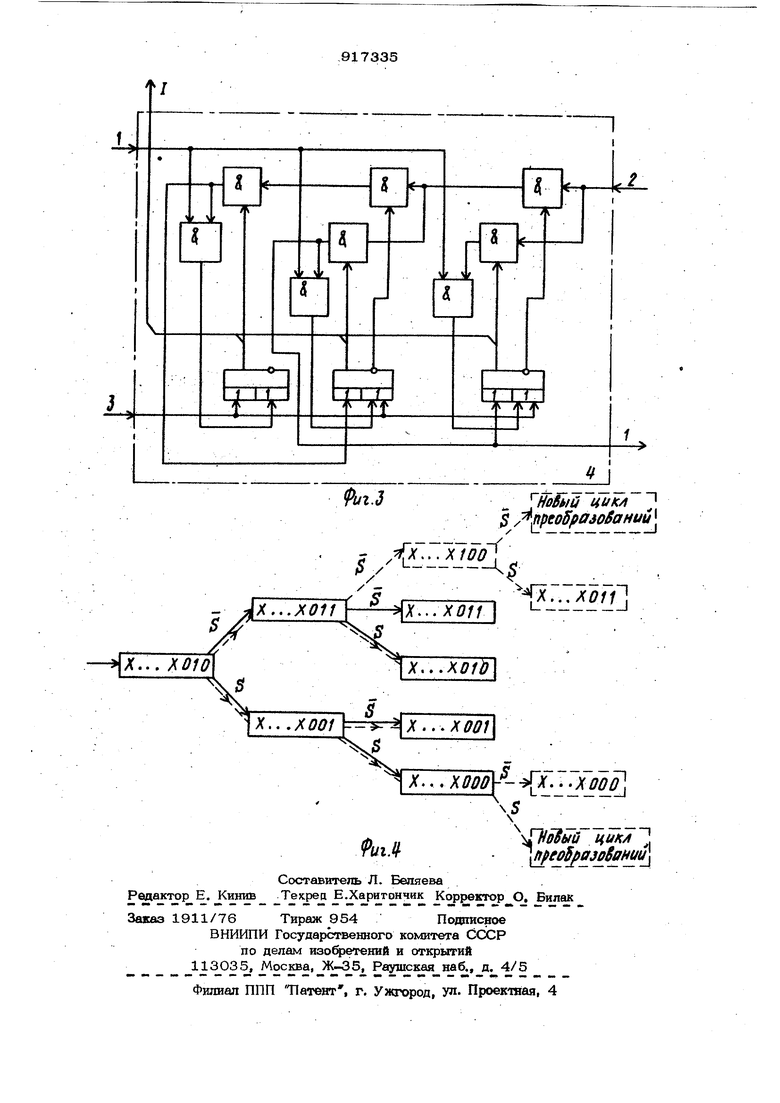

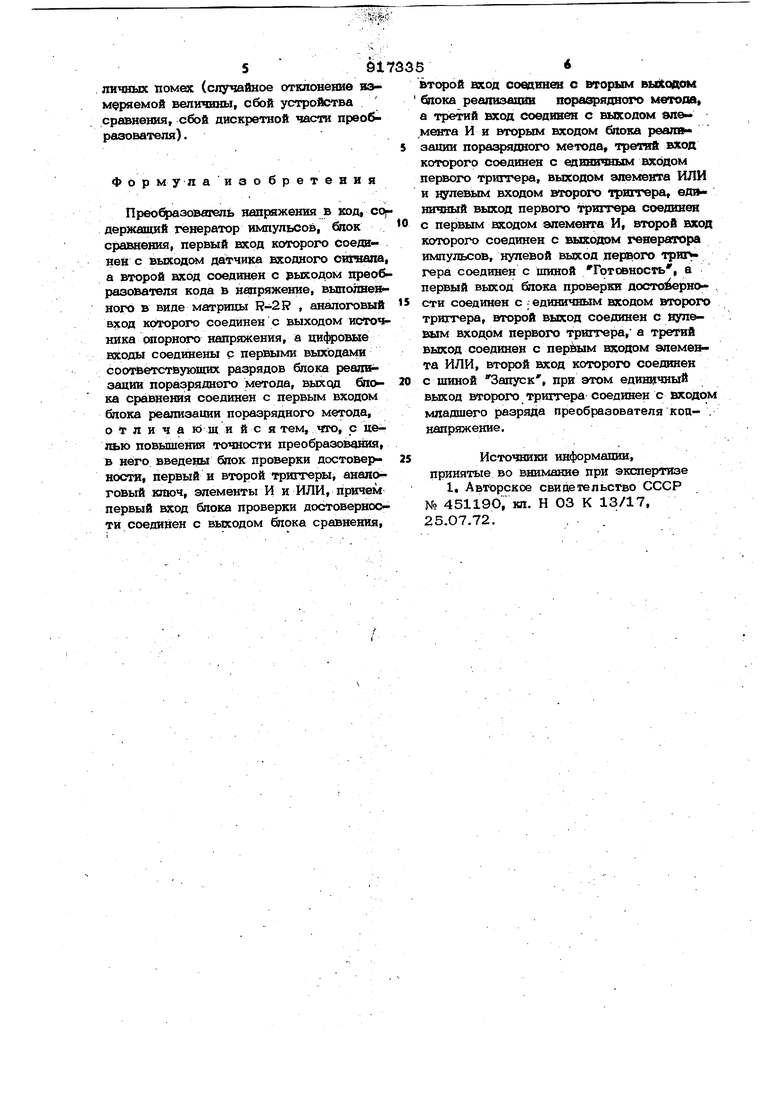

20 вход соединен со вторым выходом блока реализациипоразрядного метода, a третий вход соединен с выходом элемента И и вторым входом блока реализации пора рвдного метода, третий вход которого сое динен с единичным входом первого триггера, выходом элемента ИЛИ н нулевым входом второго триггера, единичный выхо первого триггера соединен с первым входом элементами, второй вход которого со единен с выходом генератора импульсов, нулевой выход первого трштера соединен с шиной Тотовностъ, а первый выход блока проверки достоверности соединен с единичным входом второго триггера, второй выход соединен с нулевым входом первого триггера, а третий выход соединен с первым входом элемента ИЛИ, второй вход которого соединен с шиной Запуск, при этом единичный выход второго триггера соед11нен с входом младшего разряда преобразователя код-напряжение На фиг. 1 представлена функциональная хема преобразователя напряжения в код; на фиг. 2- один из возможных вариантов реализации блока проверки достоверности; на фиг. 3 - один из возможных вариантов реализации блока поразрядного метода; на фиг. 4 - г зимер, поясняю щий супдаость преобразователя напряжения в код сплошными линиями показана работа известного , а пунктирньпуга - пред лагаемого преобразователя напряжения в код. Преобразователь напряжения в код содержит блок 1 сравнения, преобразователь 2 код-напряжение, источник 3 опорного сигнала, блок 4 реализации поразрядного метода, элемент И 5, первый триггер 6, генератор 7 импульсов, блок 8 проверки достоверности, второй триггер 9, элемент ИЛИ 10. Первый триггер (фиг. 2) служит для запоминания ответа блока сравнения на предьщушем такте. Сигналом начальной установки (не показан) второй и третий трштеры устанавливаются в О. Сигнал установки проверочной едини;аь1 в младщем разряде регистра блока реализации поразрядного метода, поступая на второй вход блока проверки достоверности устанавливает в единицу второй триггер. Если на спедукшем такте ответ блока сра& нения изменится, то на выходе логическо го элемента неравнозначности появится сигнал неравнозначности, который пройдя через первый элемент И и элемент ИЛИ, выдает сигнал на втором выходе блока . проверки достоверности и преофазование заканчивается. Если же ответ блока срав нения не изменился, то по сигналу равнознаяности через второй элемент И второй триггер установится в О, а третий в 1, кроме того, если блок сравнения выдавал-( сигнал Vx VQ , то. через чет вертый элемент И сигнал появится на пер вом выходе блока проверки достоверности. На следующем такте, если ответ бяока сравнения изменится, то через третий элемент И и элемент ИЛИ сигнал появится на втором выходе блока проверки достоверности, в противном случае сигнал появится на третьем выходе. Оутцность предлагаемого решения заключается в том, чгго для кодов, проверка достоверности которых не производится самим поразрядным методом, проводится дополнительная проверка и если эта проверка показьюает., что сигнала в указьшаемом кванте нет, то начинается новый цикл преобразования того же сигнала. Устройство работает следующим образом. Одновременно с установкой проверочной единшда в младшем разряде регистра блока 4 реализашш поразрядного метода (фиг. 1) производится запуск блока 8 проверки достоверности. Если на следуюшем такте ответ блока 1 сравнения меняется на противоположный, то на втором выходе блока Проверки достоверности появляется сигналдстанавяивакщий в О первый триггер 6 и заканчивается преобразование. Если же ответ блока 1 сравнения не изменился и при этом она BI дает сигнал V 1/ , то на первом выходе eiioKa проверки достоверности 8 появится сигнал устанавливающий второй триггер 9 в 1, тем самым в цифро аналоговом преобразователе срабатывает аналоговый ключ и подсоединяет оконеч ный резистор матрицы R. -2Як источнику 3 опорного напряжения , в результате чего величины текущего образцового уровня увеличиваются на один квант. На следующемтакте, если ответ блока сравнения изменится, то сигнал со второго выхода, блока проверки достоверности заканчивает преофаЗование, в противном случае сигнал с третьетх выхода пройдя через элемент ИЛИ 1О произведет начальную установку блока 4 реализации поразрядного метода, установит в О второй триггер 9, после чего начнется новый цикл преобразования. Таким образом, введение дополнительной проверки кодовых эквивалентов, достоверность которых не проверяется поразрядным методом, позволяет увеличить вдвое дострверность выдаваемых кодов, что в свою очередь устраняет опасность выдачи неверных кодов при наличии различных помех (случайное отклонение измеряемой величины, сбой устройства сравнения, сбой дискретной части преобразователя).

Формулаизобретевия

Преофазовагель напряжения в код, сор держащий генератор импульсов, биок сравнения, первый в(ход которого соединен с выходом датчика вводного свшапа, а второй вход соединен с рыходом преобразователя кода в напряжение, выполненного в виде матрицы R-2R , аналоговый вход которого соединен с выходом источника опорного напряжения, а цифровые входы соединены с первыми выходами соответствующих разрядов блока реалв заиии поразряднозто метопа, выход €пока сравнения соединен с первым входом блока реализации поразрядного метода, о т л и ч а ю щ и и с я тем, что, с целью повышения точности преобразования, в него введены блок проверки достове1 ности« первый и второй триггеры аналоговый ключ, элементы И и ИЛИ, причем первый вход блока проверки достоверности соединен с выходом блока сравнения.

второй вход соединен с вторым выводом блока реализации поразрядного метохш, а третий вход соединен с выходом дле,мента И и вторым входом блока рвал зашга пораг кщного метода, третий вход которого соединен с единичным входом первого триппера, выходом элемента ИЛИ и нулевым входом второго триггера ничный выход первотч) (триггера соединен с первым входом элемента И, второй вход которого соединен с выходом генератора импульсов, нулевой выход первого тригу гера соединен с шиной Грговность, а первый выход блока проверки досто рног сти соединен с .единичным входом второго триггера, второй выход соединен с нулевым входом первого триггера, а третий выход соединен с nepibjM входом элемента ИЛИ, второй вход которого соединен с шиной Запуск, при атом единичный выход второго триггера соединен с входом младшего разряда преобразователя коанапряжение.

Источники информации, принятые во внимание при экспертизе I, Авторское свицегепьство СССР № 45119О, кл. Н 03 К 13/17, 25.07.72.

&j

(Т p )1 jt-lФи1.2

Авторы

Даты

1982-03-30—Публикация

1980-06-16—Подача