(54) УСТРОЙСТВО ДЛЯ СДВИГА ДАННЫХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство для выполнения арифметических и логических операций над словами | 1978 |

|

SU767757A1 |

| Устройство для сдвига информации | 1984 |

|

SU1167658A1 |

| Устройство для выполнения арифметических и логических операций | 1977 |

|

SU674017A2 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Устройство для уплотнения информации | 1984 |

|

SU1211716A1 |

| Устройство для сдвига операндов | 1987 |

|

SU1481741A1 |

| Устройство для сдвига операндов | 1988 |

|

SU1633391A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

I

Изобретение относится к цифровой вычислительной технике и может быть использовано для организацщ запоминающих устройств.

Известно устройство сдвига данных на один или несколько разрядов за один цикл, состоящее из сдвиговой матрицы, блока управления величиной сдвига и направлением сдвига. Величина сдвига задается двоичным кодом 1 .

Недостаток устройства - невозможность получения арифметического сдвига значений данных.

Наиболее близким к предлагаемому является устройство для сдвига данных, содержащее Матрицу логических коммутаторов, каждый из которых выполнен на элементе 2И-2И-2ИЛИ, при чем логические коммутаторы сгруппированы в матрице по tog п ступеням (п - разрядность сдвигающих данных; х - ближайшее целое большее или равное числу х), выход i-ro

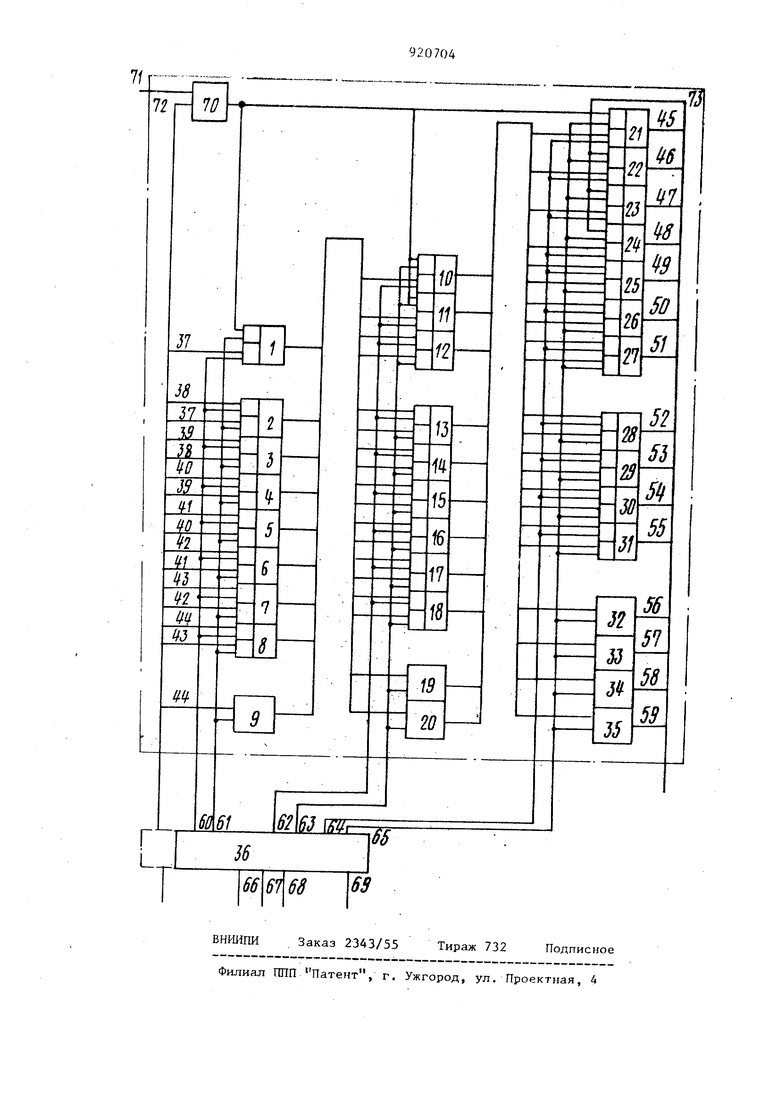

логического коммутатора j-й ступени (i 1,...,n; ,..., соединен с информационными входами 1-го и (i+2j)-ro логических коммутаторов (j+)-й ступени, первые информационные входы логических коммутаторов первой ступени соединены с соответствугацими входами разрядов данных устройства, вторые информационные входа логических коммутаторов с первого по (2 )-й k-й ступени ( ,..., .) соединены между собой и с выходом знакового разряда устройства, вторые информационные входы логических коммутаторов первой ступени соединены со входами разрядов данных устройства со сдвигом на один разряд вправо, выходы логических коммутаторов последней ступени соединены с выходами разрядов устройства 12, Это устройство осуществляет арифметические сдвиги вправо, однако не |МОжет осуществлять арифметические сдвиги влево и логические сдвиги вправо и влево. Целью изобретения является расши рение функциональных возможностей устройства. Для достижения поставленной цели в устройство для сдвига данных.содержащее матрицу логических коммута торов, каждый из которых пред,ставляет собой элемент 2И 2И-2И1Ш, при чем логические коммутаторы сгруппированы в матрице по . ступеня ми (п - разрядность сдвигар.мых данных; X ближайшее целое, большее lirm. равное числу х) , выход i-ro лог ческого коммутатора j-й ступени (,,..,n; j 1,...,., соединен с информационными входами i-ro и ()ro логических коммутаторов (+1)-й ступени, первые информационные входы.логических ком мутаторов первой ступени соединень соответствующими входами разрядов данных устройств, вторые информационные входы логических коммутаторов с первого по 2 -и к-й ступени ( Jtog2 п ) соединень между собой и с выходом знакового разряда устройства, BTOpfaie информационнь е входы логических коммутаторов первой ступени соединены со входами разрядов данных устройства со сдвигом на один разряд вправо, выходы логических коммутаторов последней ступени соединены с выходами разрядов данных устройства, введены блок преобразования прямого кода в дополнительный, элемент И, а каждая k-я ступень матрицы логических коммутаторов содержит дополнительно () логических .коммутаторов, информационные входы т-го логического коммутатора 1-й ступени ( ..., ; ,..., Ibg2.n С соединены с -выходами т-го и (т-2 )го логических коммутаторов ( сту пени, информационный вход (п+1)-го логического коммутатора первой сту пени соединен со входом п-го разряда данных устройства, выходы логических -коммутаторов с (п+1)го по (( -1)-й1 toQin -и ступе1Ш соединены с выходами разрядов данных устройства, информационные входы блока преобразования прямого кода в дополнительный соединены со входами разрядов кода сдвига устро ства, управляющий вход соединен со входом направления сдвига устройства, прямой и инверс й1й выходы k-ro разряда блока преобразования прямого кода в дополн1-1тельный соединены с управляющими входами логических коммутаторов k-й ступени, входы элемента И соединешз со входом знака данных устройства и входом вида сдвига устройства, а выход - соединен с входом знака данных устройства, На чертелсе представлена функциональная схема устройства для случая . Устройство содержит логические коммутаторы 1-35, каждый из которых представляет собой элемент 2И2 И-2 И ЛИ, И.ПИ (вырожден №1Й случай) элемент 2И, сгруппированные в матрицу, содержащую 3 ступени. Зстррйство содержит также блок 36 преобразования прямогй кода в дополнительный. Входная информация (разряды кодов данных), в виде восьмиразрядного числа поступают со входов на информационнь е входы логических коммутаторов 1-8 соответственно j а также со сдвигом на один разряд вправо - на информацио и- ые входы логических коммутаторов 2-9 соответственно. Выходы логических коммутаторов 1-9 соединень соответственно с информао,ионными входами логических коммутаторов iO-lS, а таюке со сдвигом на два разряда вправо с информационными входа ш логических коммутаторов 12-20 соответственно. Выходы логических коммутаторов 10-20 соединегпз соответственно с информационными входами логических коммутаторов 2 --31j а также со сдвигом на четыре разряда вправо - с информационными входами логических коммутаторов 25-35 соответственно. Выходы логических коммутаторов 21-35 соединены соответственно с выходами 45-59 устройства Управляющие входы логических коммутаторов 1-9 соединень с вьсходами 60 и 61 блока 35, управляюидае входы логических коммутаторов 10-20 соединены с выходами 62 и 63 блока 355 управляющие входы логических коммутаторов 21-35 соединены с выходами 64 и 65 блока 35, информационные входы 66, 67 и 68 которого соединены с входами разрядов трех разрядного кода сдвига устройства, а управлянюлй вход 69 - со входом управления сдвига устройства Вторые информационные входы коммутаторов , 1, 10, 11, 20, 21, 22 и 23 соединены с выходом элемента И .70, один вход торого соединен со входом 71 вида сдвига, а другой вход - со входом 72 знакового разряда кода данных. Выход элемента И 70 соединен также с выходом 73 знакового разряда устройства. Устройство производит сдви ги арифметические, логические влево и вправо за один цикл на произвольн число разрядов, которое определяется двоичнььм кодом величины сдвига на входах 66-68, сигналом управления направления сдвига на входе 69, сигналом управления арифметическим сдви гом на входе 71. Входы 71 и 69 обесп чивают выборку необходимой операции согласно таблице. Пример 1. Выполнить логический сдвиг влево на 3 разряда дан;ных 01110010. На входы 66-68 подается код 011, на входы 71 и 69,, согласно таблице, подается кодовое зна чение 00, входные данные OlliOOlO подаются на входы 37-44.. Так как нео ходимо выполнить сдвиг влево, то кодовое значение величины сдвига выдается из блока 36 без перевода в допо нительный код путем подачи на вход 6 значения О. На первой ступени матрицы (на коммутаторах 1-9) сдвига не происходит, так как на выходе 60 находится значение , а на выходе 61 значение 0 На выходе первой ступени информация 011100100. На второй ступени матрицы (на коммутаторах 10-20)сдвига не происходит, так как на выходе 62 находится значение 1, а на выходе 63 - значение О. На выходе второй ступени - информация 01110010000. На третьей ступени матрицы (на коммутаторах 21-35) происходит сдвиг вправо на четыреразряда, так как на выходе 64 находится О, а на выходе 65 1. На выходе третьей ступени - информация 00 1 1 0 1 И 00 I 0000. Поскольку производится сдвиг влево, то сдвинутая информагшя снимается с выходов 52-59. Таким образом на выходе есть следующая информация 10010000, т.е. относительно исходной информации, по-° лученная информация сдвинз.лась на 3 разряда влево. Пример 2. Выполнить арифметический сдвиг вправо на 5 разря - дов данных iOlOOOiO. На входы 66-68 подается код 101, на входы 71 и 69; согласно таблице, подается кодовое значение 11. Входные данные 10100010 подаются на входы 37-44. Поскольку необходимо выполнить сдвиг вправо, от необходимо кед величины сдвига преобразовать в дополнительный код. Это делается в блоке 36 путем подачи на вход 69 значения 1. Следовательно, на сдвиговую матрицу воздействует код величины сдвига 01. На первой ступени сдвига не происходит, поскольку на выходе 60 находится 1, а на выходе 61 - О. На выходе первой ступени - информация 101000100. На второй ступени матрицы сдвига не происходит, так как на выходе 62 находится 1, а па выходе 63 - О. На выходе второй ступени - информация 10100010000. На третьей ступени матрицы информация сдвинута на четыре разряда вправо, так как на выходе 64 находится значение О, а на выходе 65 - 1. На выходе третьей ступени - информация 11111IOI00010000, а так как производится сдвиг вправо, то сдвинутая информация снимается с выходов 73, 45-51. Таким образом на выходе есть следующая информация I11 М 101, т.е. относительно исходной информации, полученная информация сдвигается на 5 разрядов вправо с размножением знака на место вдвигаемых разрядов, BbmBHraeNbie разряды при этом Теряются. Применение данного устройства двига данных на один или несколько азрядов за один цикл позволяетрасирить функциональные возможности утем выполнения apиф eтичecкиx и огических сдвигов вправо и влево. Формула изобретения Устройство для сдвига данных, соержащее матрицу логических кoм fyтaоров, каждый из которых представяет собой элемент ; -2H-2HJD, причем логические коммутаторы сгруппи рованы в матрице по ступеням (п - разрядность сдвигаемых дан - ближайшее целое, большее или равное числу х), выход i-ro логи ческого коммутатора J-й ступе1Ш (,..,,п; j«1,..,, -1) соединен с информационным входами i-гЪ и (i+2j)ro логических коммутаторок (j+l)-ft ступени, первые информациейные входы логических коммутаторов первой ступени соединены с соответ йтвунлцими входами разрядов дашшт устройства, вторые информационные входы логических коммутаторов с пер вого по (2 )-и k-й CTynei-ш (k-l,... ) соединены между собой и с выходом знакового разряда устройства, вторые информационшш входы логических коммутаторов первой сту пени соединены со входами разрядов данных устройства со сдвигом на один разряд вправо, выходы логических коммутаторов последней ступени соеди нены с выходами разрядов данных уст ройст.ва, о т л и ч а ю ц е е с я тем, что, с целью расширения функциональных возможностей устройств.а за счет выполнения арифметических сдвигов влево и вправо, в устройство введены блок преобразования прямого кода в дополнительный, элемент И, а каждая к-я ступень матрицы ло гических коммутаторов содержит дополнительно () логических коммутаторов, информационш51е m-ro логического комм /татора .-й ступени (,...,п+2-1; ,,,., ) соединены с выходами т-го и (т-2 Млогических коммутаторов (-1)-й ступени, информациоиньй вход ()-гс) логического коммутатора первой ступени соединен со входом пто разряда данных устройства, выходы логических коммутаторов с (n+.t)-ro по ()-й togtnC-й ступени содинены с выходами разрядов данрых устройства,- информацион - ые входы блока преобразования прямого кода в дополнительный соединены со входами разрядов кода сдвига устройства, управляющий вход соединен со вхояом направления сдвига устройства, прямой и инверсный выходы к-го разряда блока преобразования прямого кода в дополнительный соединен с управляющими входами логических коммутаторов к-й ступени, входа элемента И соединены со входом знака данных устройства и входом вида сдвига устройства, а выход соединен с входом знака данных устройства.

Источники информации, принятые во внимание при экспертизе

2,Авторское свидетельство СССР № 622079, кл. G 06 F 17/38, 1977.

Авторы

Даты

1982-04-15—Публикация

1979-01-19—Подача