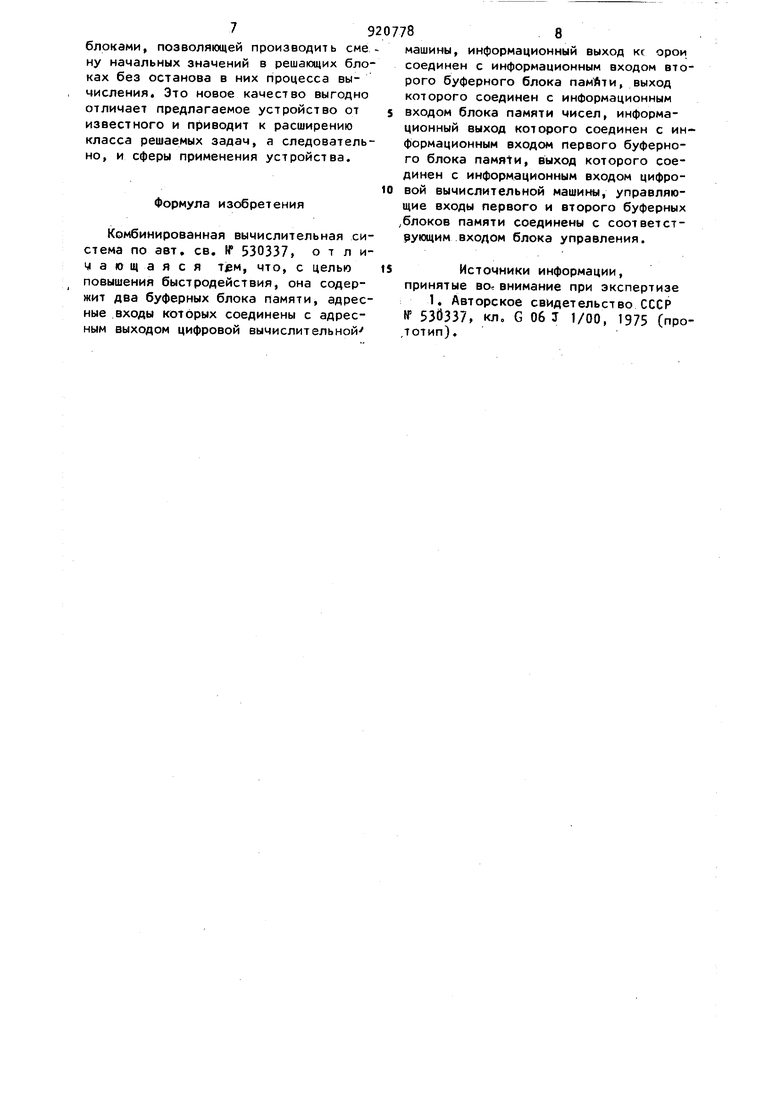

Изобретение относится к вычислительной технике и может быть испол зовано для моделирования сложных ди намических процессов управления движением объектов в реальном масштабе времени и решения различных научнотехнических задач (математической Физики, оптимального управления и т. Д.) По основному авт. ев, № 530337 из вестна комбинированная вычислительная система, содержащая решающие бло ки, блоки памяти чисел, кодов управления, кодов настройки, коммутатор, блок управления, цифровую вычислительную машину (ЦВМ) с соответствую ющими взаимосвязями til. Недостатком известного устройства является относительно низкое быстродействие, заключающееся в том, что цифровая вычислительная машина непосредственно подключается к блоку памяти чисел. Это приводит к тому, что комбинированную вычислительную систему нельзя использовать для решения некоторого класса задач, связанного с непрерывным управлением быстродействующими процессами или движением объектов, так как на время смены информации необходимо останавливать ход вычислений в решающих блоках, потому что одни и те. же ячейки блока памяти чисел используются в качестве регистров сдвига в режиме решения и в качестве регистров для приема { выдачи) параллельными кодами информационных слов в режиме обмена. Цель изобретения заключается в повышении быстродействия комбинированной вычислительной системы. Поставленная цель достигается тем, что комбинированная вычислительная система содержит два буферны: блока памяти, адресные входы которых соединены с адресным выходом цифровой вычислительной машины, информационный выход которой подключен к информационному входу второго буферного блока памяти, выход которого соединен с ин формационным входом блока памяти чисел, информационный выход которого соединен с информационным входом пер вого буферного блока памяти, выход которйго соединен с информационным входом ЦВМ. управляющие входы первог и второго буферных блоков памяти соединены с соответствующим выходом блока управления. Введение буферных блоков памяти в устройство позволяет повысить быст родействие, во-первых, за счет совмещения передачи данных из цифровой вычислительной машины во второй буферный блок памяти и передачи данных из решающих блоков в первый буферный блок памяти с процессом вычисления решающих блоков, во-вторых, за счет организации более быстрой передачи данных из второго буферного блока па мяти в блок памяти чисел параллельно по словам.и параллельно или последовательно по разрядам в процессе обме на информацией цифровой вычислительной машины с решающими блоками. На чертеже представлена структурная схема комбинированной вычислител ной системы. Система содержит цифровую вычислительную машину 1, соединенную ад ресным выходом 2 и информационными выходом 3 и входом 4 с блоками памяти чисел 5, памяти кодов настройки 6 памяти кодов управления 7 и с блоком коммутации 8, соединенным выходами и входами с информационными входом и выходом каждого решающего блока 9-i У соединенного другими информационными выходом и входом с блоком памяти чисел 5 и настроечными входами с выходом блока памяти кодов настройки 6, блок управления 10, подключенный дву сторонними связями к блокам памяти чисел 5 и памяти кодов управления 7 и управляющими выходами к решающим блокам 9-1 9 п и цифровой вычислительной машине 1, первый буферный блок памяти 11, информационный вход которого соединен с блоком памяти чисел 5, а выход - с информационным входом 4 цифровой вычислительной машины 1, второй буферный блок памяти 12, подключенный информационным выходом к блоку памяти чисел 5 и входом к выходу 3 цифровой вычислительной машины 1, соединенной адресным выходом 2 с первым.и вторым буферным блоками .памяти, управляющие выходы 13 блока управления 8, кроме того, подключены ко всем блокам памяти 5, 6, 7, 11 и 12 и блоку коммутации 8. Комбинированная вычислительная система в зависимости от класса решаемых задач работает в следующих основных режимах: последовательном, параллельном и одиночном. Последовательный режим работы характеризуется последовательной во времени работой цифровой вычислительной машины 1 и решающих блоков . Этот режим работы вычислительной системы встречается при решении задач оптимального управления и математической физики, в которых решающие блоки используются в качестве структурной подпрограммы цифровой вычислительной машины для быстрого решения систем алгебраических (дифференциальных ) ураэнений. Для этого режима работы наиболее быстродействующей является организация передачи числовых данных из циф- ровой вычислительной машины 1 (и наоборот) непосредственно в блок памяти чисел 5, так как результаты, полученные процессором цифровой вычислительной машины и являющиеся начальными зна.чениями. для решакйцих блоков, отсылаются в блок памяти чисел 5, который благодаря своему подключению к адресным и информационным шинам цифровой вычислительной машины составляет некоторую часть ее оперативной памяти. Параллельный режим работы комбинированной вычислительной системы выполняется при одновременной работе цифровой вычислительной машины и решающих блоков, например, при моделировании сложных динамических систем. Одиночный режим работы системы заключается в выполнении операций вычи. слений только решающими блоками , а цифровая вычислительная машина 1 осуществляет вывод управляющих и информационных слов в решающие блоки по сигналам прерывания, сформированным блоком управления 10. Этот режим работы встречается при программном управлении движением объектов по заранее известной траектории (программе) . Для последних двух режимов работы наиболее быстродействующей является организация передачи данных между цифровой вычислительной машиной и решающими блоками через первый 11 и второй 12 буферные блоки памяти. За счет совмещения передачи чисел из цифровой вычислительной машины во второй буферный блок памяти 12 и из решающих блоков в первый буферный блок памяти 11 с процессом вычисления решающих блоков время ввода числовых данных в решающие блоки определяется временем передачи чисел из второго буферного блока памяти 12 в блок памяти чисел 5. Это время при передаче данных параллельно по словам и параллельно по оазрядам, практически равно времени выполнения одного такта, осуществляющего передачу чисел из второго буферного блока памяти 12 в блок памяти чисел 5, То е. в этом случае возможно осущест влять смену начальных значений в решающих блоках без останова в них про цесса решения. Рассмотрим некоторые принципы организации совместной работы цифровой вычислительной машины и решающих бло ков, характерные для трех режимов работы вычислительной системы. Перед началом работы цифровая вычислительная машина выполняет с помо щью команды Передача ввод числовой информации, кодов коммутации, кодов настройки и кодов управления соответ ственно в блок памяти чисел 5, блок коммутации 8, в блоки памяти кодов настройки 6 и памяти кодов управления 7. Каждому типу передаваемой информациу соответствуют коды признака информации, которые передаются в фик сированные ячейки блока памяти 7 В COOT велстВИИ с этими кодами признаков блок управления 10 на выходе 13 формирует сигналы разрешения на ввод информации в соответствующие блоки памяти 5, 6, 7, 11и12и блок коммутации 8, а выбор ячейки в блоках п памяти выполняется с помощью адресны выходов 2 цифровой вычислительной ма шины. Ввод кодов коммутации, кодов настройки и некоторых кодов управления, задающих время решения блоков , производится обычно один раз на все время решения задачи. Затем в процессе выполнения программы цифровой вычислительной машиной происходи только смена начальных условий решаю щих блоков в ячейках блока памяти чисел 5. После ввода исходной информации блок памяти кодов настройки 6 осуществляет настройку каждого решающего блока на выполнение определенной операции (суммирования, интегрирования и т. д.), блок коммутации 8 выполняет соединение выходов и входов решающих блоков в соответствии с кодами коммутации, задающими адреса входов рзшающих блоков, и адресами на адресном выходе 2 цифровой вычислительной машины, определяющими адреса выходов решающих блоков о По управляющему слову с кодом признака пуска, переданным цифровой вычислительной машиной в фиксированную ячейку блока памяти кодов управления 7, производится пуск блоков на решение задачи. При этом цифровая вычислительная машина переключается на выполнение другой программы или находится в режиме ожидания (останов) процессе работы решающих блоков выполняется одновременный сдвиг в данных ячейках блока памяти чисел 5 тактовыми импульсами блока управления 10 (каждая ячейка соединена с соответствующим решающим блоком и используется в качестве регистра сдвига). После останова работы решающих блоков блоком управления 10 вырабатывается сигнал, который прерывает работу цифровой вычислительной машины над выполнением текущей программы или осуществляет пуск ее на продолжение выполнения старой программы, и результаты решения блоков считываются цифровой вычислительной машиной из блока памяти чисел 5 или первого буферного блока памяти 11 в зависимости от режима работы комбинированной вычислительной системы, который также задается цифровой вычислительной машиной, передачей кода в Фиксированную ячейку блока памяти . кодов управления 7. В соответствии с этим кодом блок управления 10 разрешает выдачу чисел по одним и тем же адресам или из ячеек буферного блока или блока памяти чисел 5. Кроме того, цифровая вычислительная машина может произвести считывание информации о. состоянии решающих блоков из фиксированных ячеек памяти блока памяти кодов управления 7 Использование первого и второго буферных блоков памяти повышает быстродействие комбинированной вычислительной системы при решении круга задач за счет организации более быстрой передачи данных между цифровой вычислительной машиной и решающими

блоками, позволяющей производить сме ну начальных значений в решающих блоках без останова в них процесса вычисления. Это новое качество выгодно отличает предлагаемое устройство от известного и приводит к расширению класса решаемых задач, а следовательно, и сферы применения устройства.

Формула изобретения

Комбинированная вычислительная система по авт, св. № 530337, о т л имающаяся , что, с целью повышения быстродействия, она содержит два буферных блока памяти, адресные входы которых соединены с адресным выходом цифровой вычислительной

машины, информационный выход кс орои соединен с информационным входом второго буферного блока памТйти, выход которого соединен с информационным

входом блока памяти чисел, информационный выход которого соединен с информационным входом первого буферного блока памяти, выход которого соединен с информационным входом цифровой вычислительной машины, управляющие входы первого и второго буферных блоков памяти соединены с соответструющим входом блока управления.

Источники информации,

принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 530337, кл. G Об J 1/00, 1975 (про,тотип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная система | 1975 |

|

SU530337A1 |

| Устройство сопряжения | 1974 |

|

SU519704A1 |

| Цифровая интегрирующая структура | 1974 |

|

SU674052A1 |

| Устройство для связи интегрирующей машины с электронной вычислительной машиной | 1974 |

|

SU691890A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Комбинированная вычислительная система | 1977 |

|

SU670942A1 |

| Вычислительная система для решения дифференциальных уравнений | 1978 |

|

SU771674A1 |

| ПРИСТАВКА К ЦИФРОВЫМ ВЫЧИСЛИТЕЛЬНЫМ МАШИНАМ | 1968 |

|

SU212628A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| Программируемое запоминающее устройство | 1977 |

|

SU736170A1 |

Авторы

Даты

1982-04-15—Публикация

1975-12-08—Подача