(54). ЦИФРОВОЙ АДАПТИВНЫЙ СИНХРОНИЗАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| РАДИОНАВИГАЦИОННАЯ СИСТЕМА (БАГИС-А) | 1995 |

|

RU2097780C1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство поэлементного фазирования | 1980 |

|

SU928665A1 |

| Демодулятор фазоманипулированных сигналов | 1987 |

|

SU1443200A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

Изобретение относится к вычислич тельной технике и может быть исполь-зовано для синхронизации фазокодированной информации, считанной с магнит ного. носителя, а также для формирования синхросерии сигналов для ее записи.

Известны устройства для синхронизации, содержащие управляемый генератор я фазовый дискриминатор l и 2 .

Недостатком этих устройств является то, что они являются устройства.ми с непосредственным воздействием на управляемый генератор, что приводит к снижению стабильности генератора и требует подстройки и регулировки.

Наиболее близкш к изобретению является цифровой адаптивный синхронизатор, содержащий блок выделения информационных фазовых переходов, фазовЕяй дискриминатор, корректирующий счетчик, блок уп)авления кррректирующим счетчиком, счетчик периода бита, дешифратор и дискретный управляемый генератор З .

Недостатке данного устройства ях1ляется то, что он-не является универсальным з широком диапазоне час-.

тот, его низкое оыстродействиё и то, что его нельзя использовать в качестве синхронизатора записи.

Цель изобретения - повышение надежности и быстродействия устройства синхронизации, а также раоиирениеобласти применения.

Для достижения этой цели цифровой адаптивный синхронизатор, содержащий

10 блок выделения информационных фазовых переходов, фазовый дискриминатор, корректирующий счетчик, блок управления корректирующим счетчиком/ счетчик периода бита, дааифратор,

15 причем первый.выход блока выделения информационных фазовых перехЬдов соединен с первым входом фазового дискриминатора, первым входом блока управления корректирующим счетчиком

20 и входом установки счетчика периода бита, второй выход блока выделения информационных фазовых переходов соединен с вторым входом блока .управления корректирующим счетчиком, тре25тий и четвертый входы которого соединены с первым и вторым выходами фазового дискриминатора соответственно, первый и второй выходы блока управления корректирующим счетчиком

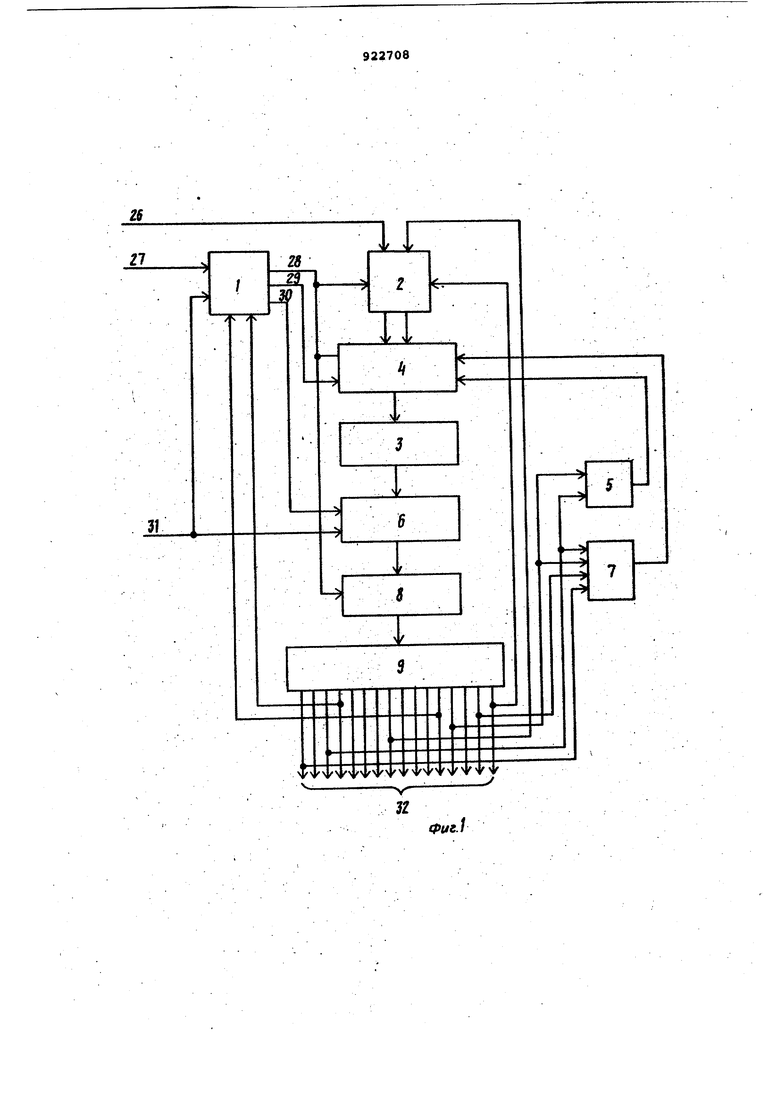

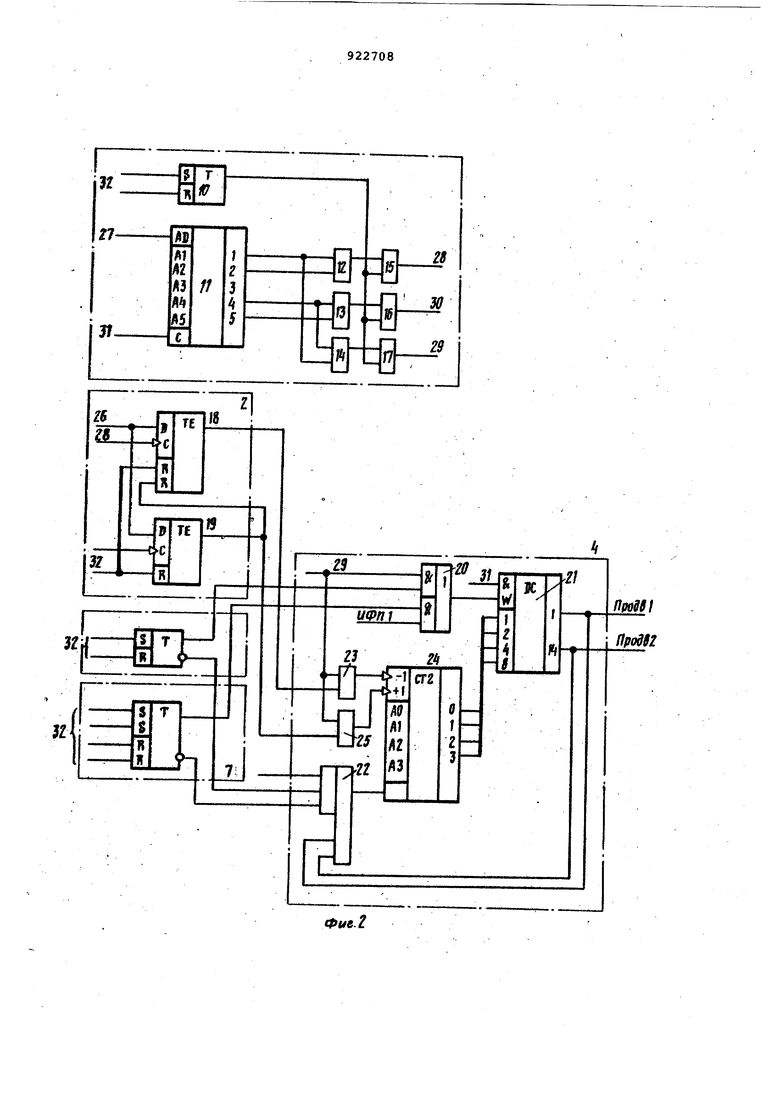

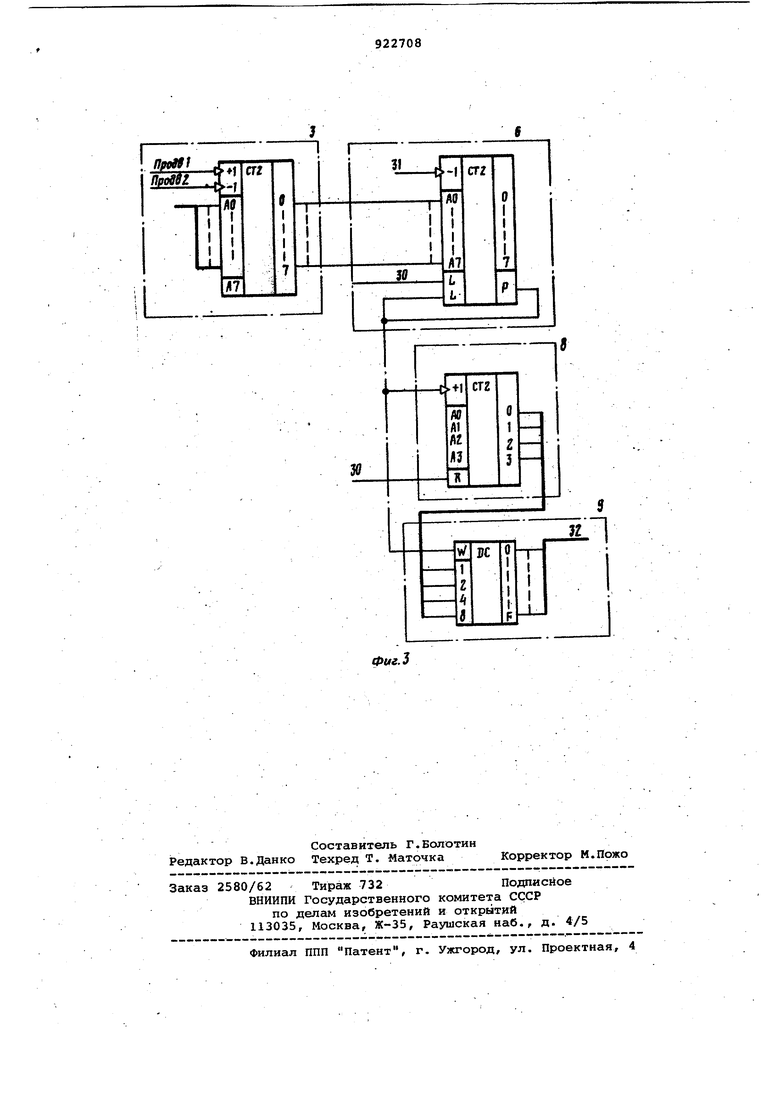

30 соединены с суммирующим и вычитгшщим входами корректирующего счетчика/ выходы разрядов счетчика периода бита соединены с входами дешифратора выходы которого с первого по шестнад цатый соединены с выходами цифрового адаптивного синхронизатора, второй, TpetHft и четвертый вхрды фазового дискриминатора соединены срответственно с входом режима работы цифрового адаптивного синхронизатора, восьмым и шестнадцатым выходами дешифратора, содержит делитель частоты, триггер грубой подстройки и трих гер точной подстройки/ причем управляющие входы делителя частоты соединены с выходами разрядов корректирую щего счетчика,, вход управления записью делителя частоты соединен с третьим выходом блока выделения информационных фазовых переходов, выхо делителя частоты соединен с счетным входом счетчика периода бита, единичный вход триггера грубой подстрой ки соединен с третьим выходом дешифратора, тринадцазий выход которого соединен с нулев.ым входсм триггера грубой подстройки, первый и второй единичные входы триггера точной подстройки соединены с.первым и тринадцатым выходами детаифратора соответственно, первый и второй нулевые входы триггера точной подстройки сое динены с третьим и пятнадцатым выхоДё1ми дешифратора соответственно, пятый и шестой входы блока управления корректирующим счетчиком соединены с прямыми выходами триггеров грубой и точной подстройки соответственно, инверсные выходы котррых соединены с седьмым и восьмым входами блока. управления корректирующим счетчиком соответственно, информационный вход цифрового адаптивного синхронизато- ра соединен с информационным входом блока выделения информационных фазовых переходов, первый и второй управляющие входы которого соединены с двенадцат(:О4 и четвертым выходами дешифратора соответственно, тактовый вход цифрового адаптивного синхронизатора соединен с тактовым входом блока выделения информационных фазовых переходов и счетным входом делителя частоты; при этом блок вы деления информационных, фазовых переходов содержит триггер, регистр, три элемента неравнозначности, три элемента И, причем выход триггера соедикен с.первыми входами первого, вто рого и.третьего элементов И, вторые входы которвхк соединены с выходами соответствующих элементов неравнозначности, первый и второй выходы ре гистра соединены с первым и вторым первого элемента неравнознач ности соответственно, третий и четвертый выходы регистра соединены с первым и вторым входами второго элемента неравнозначности соответствен но, первый и второй входы третьего элемента неравнозначности соединены . соответственно с первым и третьим выходами регистра, выходы первого, второго и третьего элементов И. соединены соответственно с первым, ВТО-. рым и третьим выходами блока, первый ц второй управляющие входы блока соединены соответственно с единичным и нулевым входами триггера, информационный вход блока соединен с информационным входом регистра, вход управления сдвигом которого соединен с тактовым входом блока; кроме того блок управления корректирующим счетчиком содержит счетчик, дешиФратоо два элемента И-ИЛИ и два элемента И, выходы которых соединены с вычитающим и суммирующим входами счетчика соответственно, выходы разрядов которого соединены с информационными входами дешифратора, выходам которого соединены с первым и вторым выходами блока, первые элеменхрв И соединены с вторым входом блока, третий и четвертый входы которого соединены с вторыми входами первого и второго элементов И соответственно, входы первой группы первого элемента ИИЛИ соединены с вторым и пятым входами блока, входы второй группы - с первым.и шестым входами блока, входы первой группы второго элемента И-ИЛИ соединены с первым, седьмым и восьмым входами блока, входы втАрРй группы - с выходами дешифратора, выход первого элемента И-ИЛИ соединен с управляющим входом дешифратора , выход второго элемента И-ИЛИ соединен с установочным входом счетчика. На фиг.1 приведена структурная схема цифрового адаптивного синхронизатора; фиг.2 и 3: - функциональная, схема цифрового адаптивного синхронизатора. Цифровой адаптивный синхронизатор содержит блок 1 вьвделения информационных фазовых переходов. Фазовый дискриминатор 2, корректирующий счетчик 3, блок 4. управления корректирующим счетчиком, триггер 5 грубой подстройки. Делитель б частоты, триггер 7 точной подстройки, счетчик ,8 периода бита и дв1гафратор 9. Блок 1 вьщеления информационных фазовых переходов 1 содержит триггер 10, регистр 11, элементы 12-14 неравнозначности, элементы И 15-17 Г Фазовый дискриминатор 2 содержит триггеры 18 и 19. Блрк 4 управления корректирующим счетчиком содержит элемент И-ИЛИ 20, дешиф ратор 21, элемент И-ИЛИ 22, элемент Н 23, счетчик 24, элемент И 25. Цифровой адгштивный синхронизатор имеет два режима работы., Он может работать . в режиме считывания фазокодированной информации, и в режиме записи ,ее на магнитный носитель. При наличии на входе 26 режима ра боты разрешающего сигнала (режим счи тывания фазокодированной информации) цифровой адаптив::ый синхронизатор ра ботает следующим образом. Входной фазокодированный сигнал Ьоступает с информационного входа 27 IB блок 1 выделения информационных фа зовых переходов 1 на информационный эход/регистра 11, где преобразуется в три последовательности сигналов ИФП1, ЙФП2 и ИФПЗ, соответствующих информационным фазовым переходам, получаемым на выходах 28-30. Блокировка фазирующих переходов входного сигнала осуществляется триг гером 10, который стробирует ыход блока выделения информационных фазовых переходов. Для отсчета периода бит по первому сигналу ИФП1 счетчик 8 периода бита сбрасывается, а по сигналу ИФПЗ в делитель б частоты загружается кон станта. При отсчете промежутка между битами содержимое делителя 6 частоты изменяется сигнала ми с тактового входа 31.. Сигнал переноса делителя 6 частоты изменяет содержимое счетчика 8 периода бита с частотой, в шестнадцать раз превышающую текущую частоту следования информационных фазовых переходов. Положения счетчика 8 периода бита декодируются дешифратором 9 и образуют на выходах 32 синхросерии ИЗ шестнадцати сигналов ССО-СС15 с периодом, равным интервалу между битами. CHrHajrtJ на выходных линиях дешифратора 9 поступают на выход цифрового адаптивного синхронизатора и используются в качестве синхросигналов управляющих работой схем записи и считывания в устройствах управления накопителями на магнитном носителе. Эти синхросигналы разбивают период следования информационных фазовых переходов на три зоны: мертвую зону, где коррекция расхождения фазы не производится, зону точной подстройки и зону грубой подстройки, что определяется состоянием триггера 7 точной подстройки и триггера 5 Грубой подстройки. При рассогласовании периода входного сигнала относительно периода следования, синхросигнала ССО {начальное положение счетчика 8 периода бита) изменяется содержимое корректи рующего счетчика 3, а затем делителя 6 частоты. Причем направление про движения корректируюиего счетчика 3 определяется- сигналами с выхода фазового дискриминатора 2. Для того, чтобы отфильтровать случайную составляющую фазовых флуктуации входного сигнала, между фазовым дискриминатором 2 и корректирующим счетчиком 3 включен реверсивный счетчик 24 с коэффициентом счета 2 (входящий в состав блока 4). Коррекция содержимого корректирующего счетчика 3 на 1 (в случае попадания информационных фазовых переходов в зону точной подстройки) или на 3 (в случае попадания информационных фазовых переходов в зону грубой подстройки) .осугаествляется при дешифрации положений 1 или 14 реверсивно о счетчика 24 блока 4 и стробируется сигналами с входа 31 и соответственно сигналом ИФП1 или ИФП2. При отсутствии на входе 26 разрешающего сигнала цифровой адапт 1вный синхронизатор работает в режиме записи. При этом блокируется работа блоков 1,2,4,5 и 7, и коррекция содер- жимого корректирующего счетчика 3 не производится. Частота следования синхросигналов ССО-СС15 в этом случае задается тактовыми ш тульсами с входа 31, исходя из скорости движения магнитного носителя и плотности записи. Применение в предлагаемом цифровом адаптивном синхронизаторе переменного коррекционного-эффекта позволяет существенно уменьшить время синхронизации, характеризующее быстродействие работы устройства. Соответственное изменение частоты сигналов внешнего тактового генератора дает воз можность использования цифрового адаптивного синхронизатора в устройствах управления накопителями на магнитном носителе с различными скоростями и плотностями записи. Отсутствие аналоговых элементов в цифровом адаптивном синхронизаторе позволяет повысить надежность. Формула изобретения 1. Цифровой адаптивный синхронизатор, содержащий блок выделения информационных фазовых переходов, фазовый дискриминатор, корректирующий счетчик, блок управления корректирующим счетчиком, счетчик периода бита, дешифратор, причем первый выход блока выделения информационных фазовых переходов соединен с первым входом фазового дискриминатора, первым входом блока управления корректирующим счетчиком и входом установки счетчика периода бита, второй выход блока выделения информационных фазовых переходов соединен с вторым входом блока управления корректирующим счетчиком, третий и четвертый входы которого соединены с первым и вторым выходами фазового дискриминатора соответственно, первый и второй выходы блока управления корректирующим счетчиком соединены с суммируюцим и вычитающим входами корректирующего счетчика, выходы разрядов счетчика периода бита соединены с входами дваифратора, выхрды которого с первого по шестнадцатый соединены с выходами цифрового адаптивного синхронизатора, второй, третий и четвертый входы фазового дискриминатора соединены соответственно с входом режима работы цифрового адаптивного синхронизатора, восьмым и шестнадцатым выходами дешифратора, отличающийся тем, что, с целью повышения быстродействия и надежности и расширения области применения, он содержит делитель частоты, триггер грубой подстроки и триггер точной подстройки, причем управляющие входы делителя частоты соединены с.выходами разрядов кор ректирующего счетчика, вход управления записью делителя частоты соедине с третьим выходом блока выделения информационных фазовых переходов, выхо делителя частоты соединен с счетные входом счетчика периода бита, единичный вход триггера грубой подстройки соединен С третьим выходом дешифратора, тринадцатый выход которого соединен с нулевым входом триггера Грубой подстройки, первый и второй единичные входы триггера точной подстройки соединены с первым и тринадцатым выходами дешифратора соответственно первый и второй нулевые вхо,ды триггера точной подстройки соеди нены с третьим и пятнадцатым выходами дешифратора соответственно, пятый и шестой входы блока управления корректирующим счетчиком соединены с прямыми выходами триггеров грубой И точной подстройки соответственно, инверсные выходы которых соединены с седьмым и восьмым входами блока управления корректирующим счетчиком соответственно, информационный вход цифрового адаптивного синхронизатора соединен с информационным входом блока выделения информационных фазовых переходов, первый и второй управляющи входы которого соединены с двенадцатым и четвертым выходами дешифратора соответственно, тактовый вход цифрового адаптивного синхронизатора соединен с тактовым входом блока выделения информационных фазовых переходов и счетным входом делителя ЧИСТОТЫ.

; Источники информации, принятые во внимание при экспертизе

кл. 329-104, опублик. 1975 (прототип

г

п

jrт

Фие.2

Авторы

Даты

1982-04-23—Публикация

1980-01-22—Подача