t

Изобретение относится к запоминаю щим устройствам.

Известно устройство, содержащее схему пуска-останова, счетчика адреса, имитаторы ввода начального адреса, количества адресов и кода числа, -схему формирования кода .адреса, схему сравнения адреса, контрольный регистр числа, схему формирования кода числа, схему сравнения чисел, счетчик циклонов, схему сравнения циклоп и схему управления кодом чисел 1 ..

Недостатками этого устройства являются сложность и невысокая достоверность контроля.

Наиболее близким к предлагаемому является устройство для контроля блоков оперативной памяти, содержащее первый счетчик, регистр числа и блок управления, подключенные к выходным шинам устройства, счетный триггер, формирователь, элемент И, основные коммутаторы.

полусумматор, дополнительные коммутаторы, второй и третий счетчики 2..

Недостатком этого устройства является низкая достоверность контроля, так как применяемые в нем тесты типа Дождь и Адресный код не обеспечивают полной проверки блока оперативной памяти, в частности динамических качеств усилителей

10 считывания..

Цель изобретения - повышение достоверности контроля.

Поставленная цель достигается тем, что в устройство для контроля

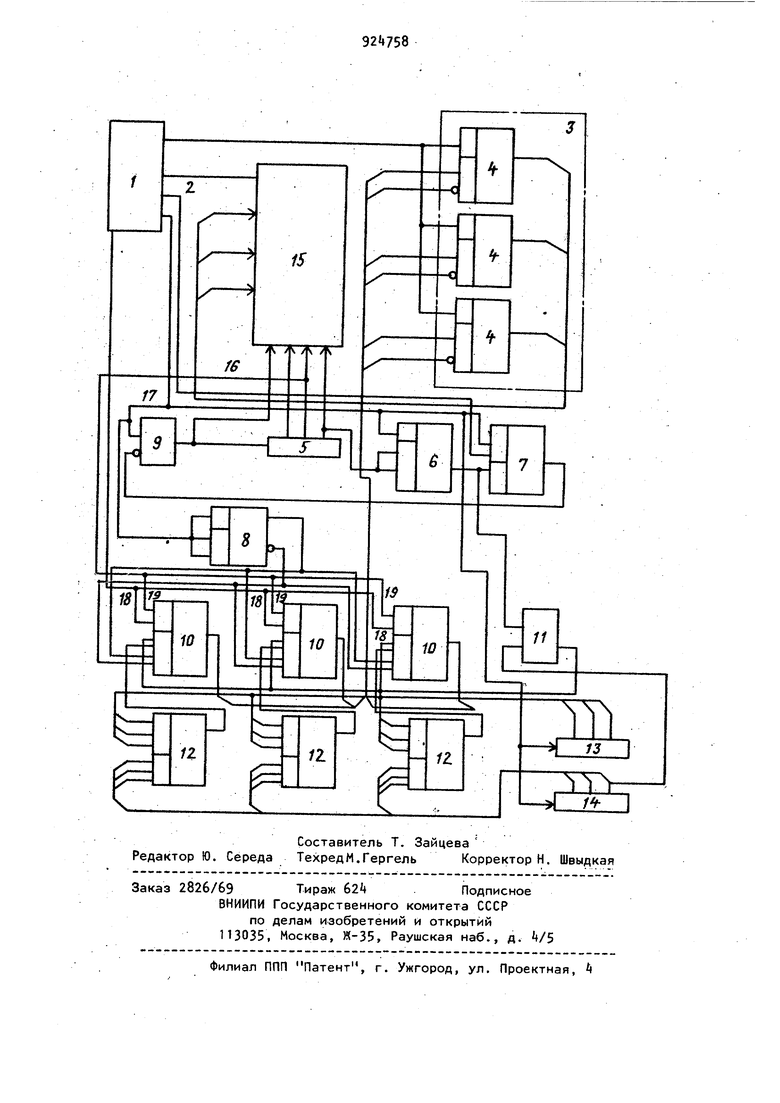

15 оперативной памяти, содержащее блок управления, регистр числа, элемент И, первый счетный триггер, формирователь импульсов, основные и до2Q полнительные коммутаторы, полусумматор и счетчики, причем выходы первого счетчика и регистра числа , выход элемента И и первый выход блока управления являются выходами устройства , второй выход блока управления соединен с первым входом элемента И, первыми входами первого счетного триггера и формирователя им, ульсов и входами второго и третьего счетчиков, выход элемента И подключен к входу первого счетчика, один из выходов которого соединен с вторым и третьим входами первого счетного триггера, выход которого подключен к первому входу полусумматора и второму входу формирователя импульсовi выход которого соединен с вторым входом элемента И, второй вход полусумматора подк .лючен к одному из выходов третьего счетчика, а выход - к первым информационным входам основных коммутаторов, выходы которых соединены соответственно с одними из входов регистра числа, другие входы которого подключены к третьему выходу блока управления,четвертый выход ко торого соединен с первыми управляющими входами основных коммутаторов вторые информационные входы которых подключены соответственно к выходам дополнительных коммутаторов, уп равляющие и информационные входы ко торых соединены соответственно с вы ходами второго и третьего счетчиков содержит второй счетный триггер, первый , второй и третий входы кото рого подключены к первому входу элемента И, пряной и инверсный выходы второго счетного триггера соединены соответственно с информацион ными входами основных коммутаторов, вторые управляющие входы которых .подключены к другому выходу первого счетчика, третий вход формирователя импульеов соединен с одним из выходов блока управления, .1 :- На чертеже изображена функционал ная схема предлагаемого устройства. Устройство содержит блок 1управ ления с первым выходом 2, регистр 3 числа, выполненный на триггерах , первый счетчик 5 , имеющий разрядность п . , где А - количество адресов, и предназначенный для формирования кода адреса, счетный триггер 6, формирователь 7 импульсов, второй счетный триггер 8, элемент И 9, основные коммутаторы 10, полусумматор 11, дополнительные коммутаторы 12, второй 13 и третий It счетчики. На чертеже показан контролируемый блок 15 оперативной памяти. На чертеже обозначен ( )ный выход 16 первого счетчика ,соединенный со вторыми управляющими входами основных коммутаторов. vHa чертеже обозначены также первый вход 17 элемента И, первые 18 и вторые 19 управляющие входы основных коммутаторов. Третий счетчик 1 имеет разрядность (п +1 ). Устройство работает следующим образом. Импульсы на управляющих входах 18 и 19 основных коммутаторов 10 обуславливает выбор одного из трех применяемых в устройстве контрольных тестов : Дождь. Адресный код или Шахматный код.Рассмотрим работу устройства в режиме формирования теста Шахматный код. После запуска устройства блок 1 управления выдает управляющие импульсы, под воздействием которых коммутаторы 10 подключают выходы счетного триггера 8 ко входам регистра 3- Блок 1 вырабатывает тактовую последовательность импульсов, причем управляющий сигнал на третьем входе формирователя 7 обеспечивает прохождение этой последовательности импульсов через элемент И 9 на вход счетчика 5. Во время первого такта обращения первого подцикла происходит запись кода О в первый адрес блока 15. Затем на выходе счетного триггера 8 появляется код 1, который записывается во второй адрес блока 15. Далее в третий адрес блока 15 записывается код О. Так продолжается до 2V адреса. Таким образом, первая строка первого канала блока 15 заполнена перемежающимися единицами и нулями. После заполнения 2 адресов на выходе 1б счетчика 5 устанавливается уровень логической 1, разрешая тем самым Д прохождение в следуюичие 2 - тактов обращения импульса с инверсного выхода счетного триггера 8 на входы регистра 3. Итак в течение первого подцикла каждый канал блока 15 заполнен Шахматным кодом. Во время второго подцикла в блок 15 записыва-, ется инверсный Шахматный код. Применение этого .кода обеспечивает- более полную проверку динамических качеств усилителей считывания блока 15 оперативной памяти. Технике-экономическое преимущерт во предлагаемого устройства заключа ется ь более высокой, по сравнению с известным , достоверности контрол блоков оператив.ной памяти за счет применения теста Шахматный код на ряду с тестами Дождь и Адресный код. Формула изобретения Устройство для контроля блоков оперативной памяти, содержащее блок управления, регистр числа, элемент И, первый счетный триггер , формирователь импульсовi основные и дополнительные коммутаторы, полусум матор и счетчики, причем выходы пер вого счетчика и регистра числа, выход элемента И и первый выход блока управления являются выходами устройства, второй выход блока управления соединен с первым входом элем та И, первыми входами первого счётного триггера и формирователя им;Пулъсов, и входами второго и третьего счетчиков, выход элемента И под ключен к входу первого счетчика, один из выходов которого соединен с вторым и третьим входами первого счетного триггера, выход которого Подключен к первому входу полусумма тора и второму входу формирователя импульсов, выход которого соединен с вторым входом элемента И, вто рой вход полусумматора подключен к одному из выходов третьего счетчика, а выход - к первым информационным входам основных коммутаторов,&ыходы которых соединены соответственно с одними из входов регистра числа, другие входы которого подключены к третьему выходу блока управления, четвертый выход которого соединен с первыми управляющими входами основных коммутаторов, вторые информационные входы которых подключены соответственно к выходам дополнительных коммутаторов, управляющие и информационные входы которых соединены соответственно с выходами второго и третьего счетчиков, о т л и ч а ю щ е е с я т;ем, что, с целью повышения достоверности контроля , оно содержит второй счетный триггер, первый , второй и третий входы которого подключены к- первому входу элемента И, прямой и инверсный выходы второго счетного триггера соединены соответственно с информационными входами основных коммутаторов, вторые управляющие входы которых подключены к другому выходу первого счетчика, третий вход формирователя импульсов соеди- нен с одним из -выходов блока управления. Источники информации , принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 07398, кл. G 11 С 29/00, 1972. 2.Авторское свидетелБСТво СССР № , кл. U 11 с 29/00, 1975 (прототип

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1022225A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Устройство для контроля оперативной памяти | 1980 |

|

SU955208A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1024990A1 |

| Устройство для контроля оперативной памяти | 1975 |

|

SU547837A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Генератор сигналов | 1985 |

|

SU1335968A1 |

| Устройство для контроля памяти | 1981 |

|

SU1001180A1 |

Авторы

Даты

1982-04-30—Публикация

1980-10-02—Подача