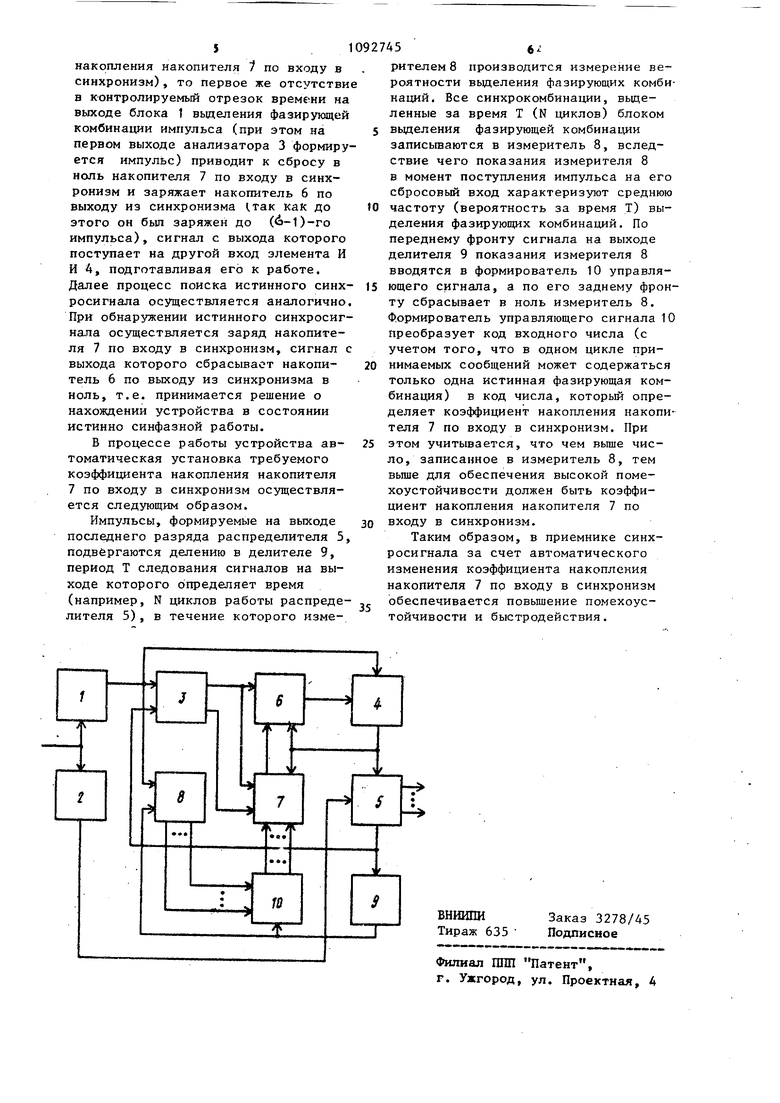

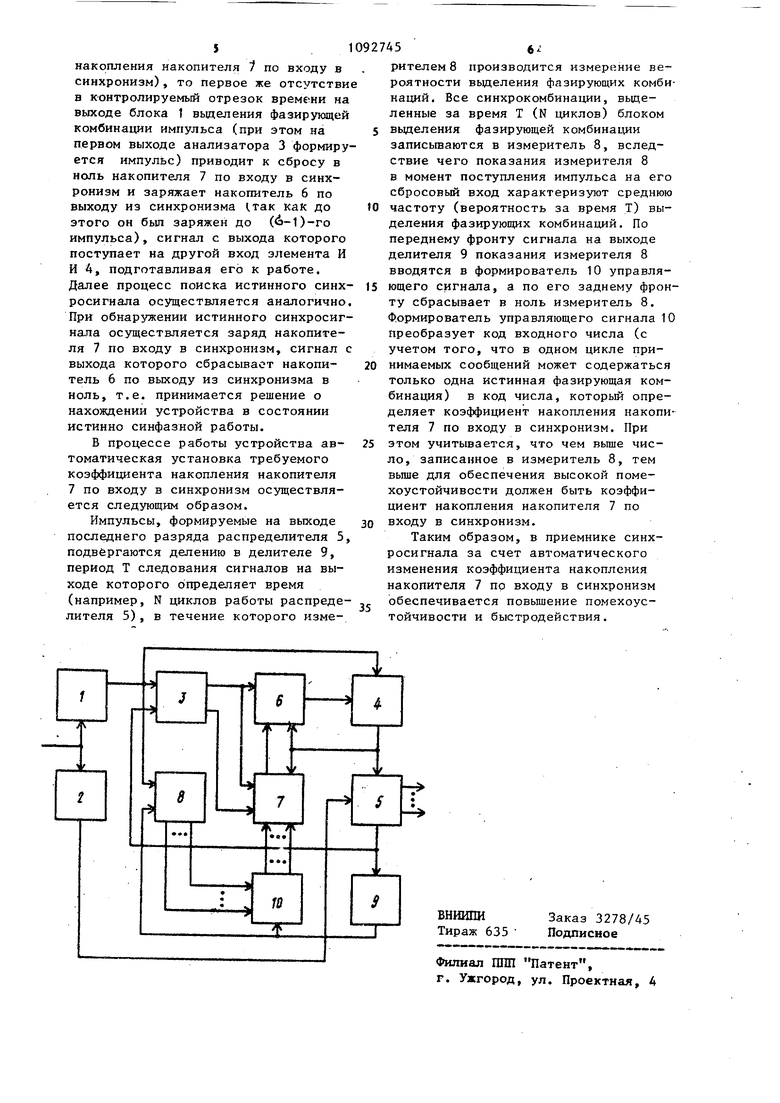

Изобретение относится к электросвязи и может быть использовано для фазирования синхронных систем передачи дискретных сигналов. Известен приемник синхросигнала, содержащий последовательно соединен ные блок регистрации, блок вьиелени фазирующей комбинации, блок защиты, блок установки распределителя импул сов и распределитель импульсов, а также блок вьщеления тактовых импул сов, выход которой подключен к объединенным входам блока регистрации и распределителя импульсов . Недостатками известного приемника синхросигнала являются низкие помехоустойчивость и быстродействие Наиболее близким к изобретению п техническому решению является прием ник синхросигнала, содержащий после довательно соединенные блок вьщеления фазирлощей комбинации, анализатор совпадения, накопитель по выход из синхронизма, элемент И и распределитель импульсов, а также накопитель по входу в синхронизм и блок вьщеления тактовых импульсов, выход которого подключен к тактовому вход распределителя импульсов, второй вход элемента И соединен с выходом блока вьщеления фазирующей комбинации, а выход элемента И подключен к установочному входу накопителя по выходу из синхронизма и первому сбр совому входу накопителя по входу в синхронизм, информационный вход которого соединен со вторым выходом анализатора совпадения, а выход накопителя по входу в синхронизм подключен к сбросовому входу накопителя ПО выходу из синхронизма, выход распределителя импульсов подключен к тактовому входу анализатора совпа дения, а объединенные входы блока вьщеления фазирующей комбинации и блока выделения тактовых,импульсов, а также дополнительные выходы распределителя импульсов являются соответственно входом и выходами приемника синхросигнала С 2 Л. Недостатками известного приемника синхросигнала являются низкие помехоустойчивость и быстродействие Цель изобретения - повьшение помехоустойчивости и быстродействия. Указанная цель достигается тем, что в приемник синхросигнала, содер жащий последовательно соединенные блок вьщеления фазиру ощей комбинации, анализатор совпадения, накопи-тель по выходу из синхронизма, элемент И и распределитель импульсов, а также накопитель по входу в синхронизм и блок вьщеления тактовых импульсов, выход которого подключен к тактовому входу распределителя импульсов, другой вход элемента И соединен с выходом блока вьщеления фазирующей комбинации, а выход элемента И подключен к установочному входу накопителя по выходу из синхронизма и к первому сбросовому входу накопителя по входу в синхронизм, информационный вход которого соединен с другим выходом анализатора совпадения, а выход накопителя по входу в синхронизм подключен к сбросовому входу накопителя по выходу из синхронизма, один из выходов распределителя импульсов подключён к тактовому входу анализатора совпадений, а объединенные входы блока выделения фазирующей комбинации и блоки вьщеления тактовых импульсов, а также другие выходы распределителя импульсов являются соответственно входом и выходами приемника синхросигнала, введены последовательно соединенные измеритель вероятности формирования фазирующих комбинаций и формирователь управляющего сигнала, а также делитель частоты, при зтом вход делителя частоты соединен с выходом распределителя импульсов, а выход делителя частоты подключен к стробирующему входу формирователя управляющего сигнала и к сбросовому входу измерителя вероятности формирования фазирующих комбинаций, информационный вход которого соединен с выходом блока вьщеления фазирующей комбинации, а выходы формирователя управляющего сигнала подключены к соответствующим установочным входам накопителя по входу в синхронизм, второй сбросовый вход которого объединен с входом накопителя по выходу из синхронизма. На чертеже изображена структурная электрическая схема приемника синхросигнала. Приемник синхросигнала содержит блок 1 вьщеления фазирующей комбинации, блок 2 вьщеления тактовых импульсов, анализатор 3 совпадения, элемент И 4, распределитель 5 импульсов, накопитель 6 по выходу из синхронизма, накопитель 7 по входу в синхронизм, измеритель о вероятности формирования фазирующих комбинаций, делитель 9 частоты и формиро ватель 10 управляющего сигнала. Приемник синхросигнала работает следующим образом. Цифровой групповой сигнал поступает на объединенные входы блока 1 вьщеления фазирующей комбинации и блока 2 вьщеления тактовых.импульсо Блок 2 вьщеления тактовых импуль сов формирует тактовые импульсы, си фазные и синхронные принимаемым эле ментам сообщения, которые обеспечивают непрерывную работу распределителя 5. Каждая комбинация принимаемых элементов сообщения, аналогичная фазирующей, вьщеляется блоком 1 вьщеления фазирующей комбинации-. Выходной сигнал последнего фиксируется (записывается символ 1) в измерителе 8, а также поступает на информационньм вход анализатора 3, на тактовый вход которого поступают импульсы с выхода последнего разряда распределителя 5 (их период след вания равен длительности цикла принимаемых элементов сообщения). Если приемник синхросигнала находится в состоянии синхронизма, то сигналы н входах анализатора 3 совпадают во времени, вследствие чего на другом выходе анализатора 3 формируются импульсы, заряжающие накопитель 7 по.входу в синхронизм, коэффициент пересчета (емкость счетчика) которого определяется кодом числа на вы ходе формирователя 10 управляющего сигнала. При заряде накопителя 7 по входу в синхронизм на его выходе формируется импульс, сбрасывающий накопитель 6 по выходу из синхронизма в ноль, т.е. приемник синхросигнала принимает решение о нахождении в состоянии истинно синфазной работы (это состояние сохраняется до тех пор, пока каждому цик лу работы непрерывно работающегора пределителя 5 соответствует .формиро вание импульса на втором выходе ана лизатора 3, т.е. вьщелёние фазирующей комбинации блоком 1 вьщеления фазирующей комбинации в требуемый момент времени). Ложные -фазирующие комбинации, фо мируемые в групповом сигнале вследствие случайного сочетания единиц и нулей информации и вьщеляемые бло ком 1 вьщеления фазирующей комбинации, записываются в измеритель 8, однако вследствие случайного расположение внутри циклов принимаемых сообщений, они не совпадают, естественно, во времени с сигналом на выходе последнего такта распределителя 5 и не участвуют в процессе накопления . При кратковременных пропаданиях истинного синхросигнала (фазирующей комбинации), возникающих, например, под действием помех в каналы связи либо при сбоях синхронизации в системах более высокого порядка, сигнал с выхода последнего разряда распределителя 5 проходит на первый выход анализатора 3, сбрасывая в ноль накопитель 7 по входу в синхронизм и записывая единицу в накопитель 6 по выходу из синхронизма, т.е. приемник синхросигнала переходит в режим поддержания синхронизма. Однако если накопитель 6 по выходу из синхронизма .не успевает зарядиться (для этого на его вход должно поступить . импульсов) до повторного заряда накопителя 7 по входу в синхронизм, то сигнал с выхода накопителя 7 по входу в синхронизм сбра1сывает накопитель 6 по выходу из синхронизма в ноль, т.е. устройство вновь возвращается в состояние истинно синфазной работы, т.е. сбоя синхронизации не происходит. При отсутствии же истинной фазирующей комбинации в 6-J цикле происходит заряд накопителя 6 по выходу из синхронизации, единичный уровень напряжения с выхода которого подготавливает к работе элемент И 4 по первому входу. В этом случае первый же импульс, сформированньй на выходе блока 1 вьщеления фазирующей комбинации, проходит через элемент И 4, устанавливая распределитель 5 в новое исходное состояние работы (изменяет временную фазу цикла его работы) , сбрасывая в ноль накопитель 7 по входу в синхронизм и устанавливая накопитель 6 по выходу из синхронизма в состояние, соответствующее поступлению на его вход (6-1)-го импульса. Если ложная синхрокомбинация сформируется на одних и тех же позициях в цикле меньше, чем К раз подряд (где К - установленный коэф11)ицие1тт накопления накопителя 1 по входу в синхронизм), то первое же отсутстви в контролируемый отрезок времени на выходе блока 1 вьиеления фазирующей комбинации импульса (при этом на первом выходе анализатора 3 формиру ется импульс) приводит к сбросу в ноль накопителя 7 по входу в синхронизм и заряжает накопитель 6 по выходу из синхронизма (.так как до этого он был заряжен до (6-1)-го импульса), сигнал с выхода которого поступает на другой вход элемента И И 4, подготавливая его к работе. Далее процесс поиска истинного синх росигнала осуществляется аналогично При обнаружении истинного синхросиг нала осуществляется заряд накопителя 7 по входу в синхронизм, сигнал выхода которого сбрасывает накопитель 6 по выходу из синхронизма в ноль, т.е. принимается решение о нахождении устройства в состоянии истинно синфазной работы. В процессе работы устройства автоматическая установка требуемого коэффициента накопления накопителя 7 по входу в синхронизм осуществляется следующим образом. Импульсы, формируемые на выходе последнего разряда распределителя 5 подвергаются делению в делителе 9, период Т следования сигналов на выходе которого определяет время , v- чг -х(например, N циклов работы распреде лителя 5), в течение которого измерителем 8 производится измерение вероятности вьщеления фазирующих комбинаций. Все синхрокомбинации, вьщеленные за время Т (N циклов) блоком выделения фазирующей комбинаьщи записьшаются в измеритель 8, вследствие чего показания измерителя 8 в момент поступления импульса на его сбросовый вход характеризуют среднюю частоту (вероятность за время Т) выделения фазирующих комбинаций. По переднему фронту сигнала на выходе делителя 9 показания измерителя 8 вводятся в формирователь 10 управляющего сигнала, а по его заднему фронту сбрасывает в ноль измеритель 8. Формирователь управляющего сигнала 10 преобразует код входного числа (с учетом того, что в одном цикле принимаемых сообщений может содержаться только одна истинная фазирующая комбинация) в код числа, который определяет коэффициент накопления накопителя 7 по входу в синхронизм. При этом учитывается, что чем вьше число, записанное в измеритель 8, тем вьше для обеспечения высокой помехоустойчивости должен быть коэффициент накопления накопителя 7 по входу в синхронизм. Таким образом, в приемнике синхросигнала за счет автоматического изменения коэффициента накопления накопителя 7 по входу в синхронизм обеспечивается повышение помехоустойчивости и быстродействия.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Устройство синхронизации | 1980 |

|

SU982205A1 |

| Устройство синхронизации | 1983 |

|

SU1095435A1 |

| Устройство для синхронизации по циклам | 1988 |

|

SU1690209A1 |

| Система для асинхронного сопряжения импульсных потоков | 1986 |

|

SU1420670A1 |

| ПРИЕМНИК СИНХРОСИГНАЛА | 2002 |

|

RU2242093C2 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

ПРИЕМНИК СИНХРОСИГНАЛА, содержащий последовательно соединенные блок выделения фазирующей комбинации, анализатор совпадения, накопитель по выходу из синхронизма, элемент И и распределитель импульсов, а также накопитель по входу в синхронизм и блок вьщеления тактовых импульсов, выход которого подключен к тактовому входу распределителя импульсов, другой вход элемента И соединен с выходом блока выделения фазирующей комбинации, а выход элемента И подключен к установочному входу накопителя по выходу из синхронизма и к первому сбросовому входу накопителя по входу в синхронизм, информационный вход которого соединен с другим выходом анализатора совпадения, а выход накопителя по входу в синхронизм подключен к сбросовому входу накопителя по выходу из синхронизмй, один из выходов распределителя импульсов подключен к тактовому входу анализатора совпадений, а объединенные входы блока выделения фазирующей комбинации и блока выделения тактовых импульсов, а также другие выходы распределителя импульсов являются соответственно входом и выходами приемника синхросигнала, отличающийся тем, что, с целью повьшения помехоустойчивости и быстродействия, введены последовательно соединенные .измеритель вероятности формирования фазирующих комбинаций и формирователь управляющего (Л сигнала, а также делитель частоты, е при этом вход делителя частоты соединен с выходом распределителя импульсов, а выход делителя частоты подключен к стробирующему входу формирователя управляющего сигнала и к сбросовому входу измерителя вероятности формирования фазирующих комбинаций, информационный вход которого соединен с выходом блока вы деления фазирующей комбинации, а СП выходы формирователя управляющего сигнала подключены к соответствуюпц м установочным входам накопителя по входу в синхронизм, второй сбросовый вход которого объединен с входом на копителя по выходу из синхронизма.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Мартынов Е.М | |||

| Синхронизация в системах передачи дискретных сообщений | |||

| М-., Связь, 1972, с | |||

| Заслонка для русской печи | 1919 |

|

SU145A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Левин Л.С., Ипоткин М.А | |||

| Основы построения цифровых систем передачи | |||

| М., Связь, 1975, с | |||

| Способ получения бензидиновых оснований | 1921 |

|

SU116A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-05-15—Публикация

1981-12-25—Подача