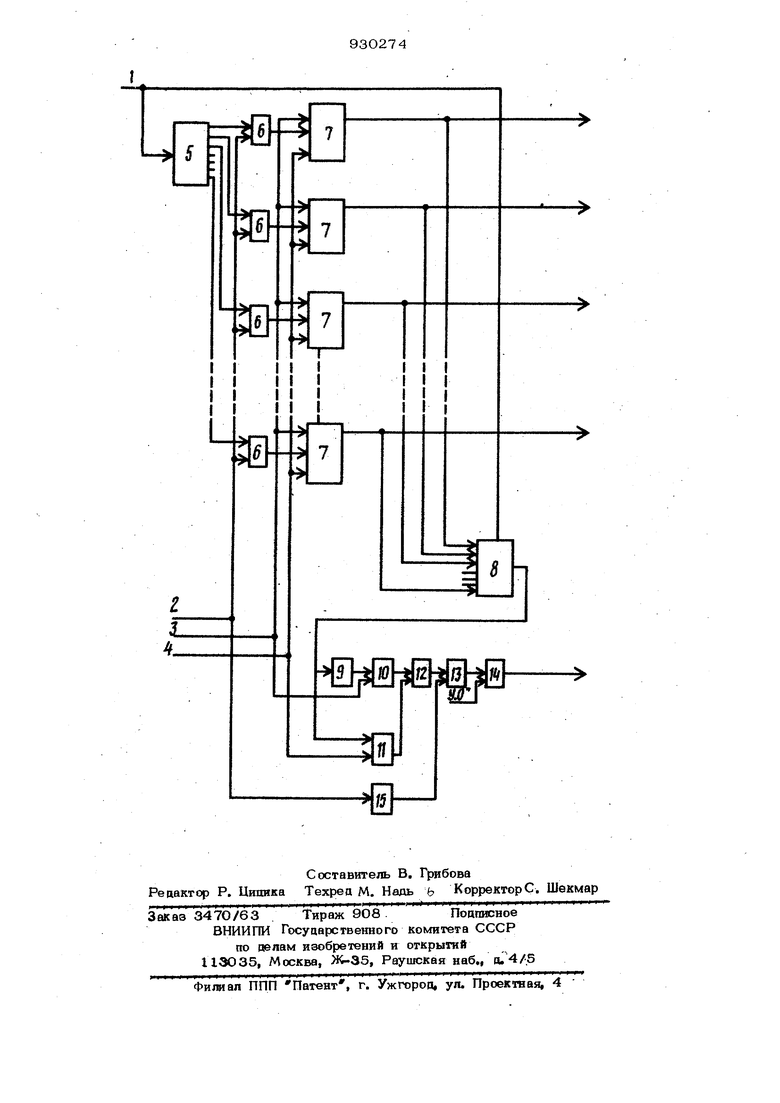

Изобретение относится к автоматике и может быть использовано в системах управления различным технологическим оборудованием. Известно устройство управления с последовательной обработкой входных сиг налов, содержащее коммутатор вхошых сигналов, логический блок, обеспечивающей последовательную обработку входны сигналов и формирование выходных упра& ляюших сигналов, а также программируемую память, адресный регистр, указывающий адрес входа иливькода, дешифрато и выходной регистр для хранения выходных управляюцих сигналов и выдачи их на исполнитгльные механизмы. Выходные управляющие сигналы, сфо М1;рованные в логическом , посту пают на триггеры выходного регистра, Выбор требуемого триггера осуществляется деишфратором по адресу, указанному в адресном регистре 1. Недостатком устройства явлжтся отсутствие контроля правильности записн выходных управляющих сигналов,в трипГеры выходного регистра. Наиболее близким техническим решением к предлагаемому изобретению явл9 ется устройство которое сооеркшт адреоную шину, шину синхроннаацин, . пись 1, шину Запись О , пбшнфратор, группу элементов И, группу Т-К триггаров выходного регистра и коммутатор. Адресная шина устройства соесшнена с входом дешифратора и с адресным вхопом коммутатора. Выходы оешвфратора соеда нены с первыми входами логвческнх схем И, вторые входы которых соединЕены с йог ной свнхроннзацяи. Выход каждого ал. мента И соеовв с свнхрсвиавруювшм входом соответствующего триггера BI« ходаого репистра. Швны Запись I и Запись О устройства соетнены cooi. ветственно с. входами Т и К тртггеров, выходы которых соединены с исполнитель ными механизмами i с соот&етстцуювшмя йн юрмаононвымн входами коммутатора. Выход коммутатора является контрольным выходом устройства. При поступлении коаа адреса по адресной шине на вход дешифратора последний подготавливаег соответствующий элемент И к прохождению через него импу льса синхрсниэации на выбранный триггер выходного регистра. Одновременно с кодом адреса подается сигнал по одной из шин Запись 1 или Запись О , в зависимости от того, в какое состояние должен быть установлен выбранный триггер. Затем поступает импульс синхронизации. и переводит данный триггер в требуемое состояние. Аналогично происходит переклточение остальных триггеров выходного регистра. Контроль правильности установки каждого триггера осуществляется с помощью коммутатора, т.к. его выходной сигнал в каждый данный момент вре- мени соответствует состоянию триггера, код адреса которого установлен на адресной шине 2 . Нецостагок известного состоит в том, что его схема предлагает программную реализацию контроля правильности jrcTaновки триггеров в заданное состояние. Действительно, чтобы определить соответ ствует ли новое состояние триггера заданному, необходимо запомнить, какой из сигналов (Запись О или Запись 1) был подан на его вход, затем после уста новки триггера опросить чере.з коммутатор его выход и сравнить состояние выхо да с подававшимся входным сигналом. Та кая организация контроля требует,. по крайней мере, выполнения двух дополнительных команд - считьюание состояния триггера и сравнение. Все это приводит к удлинению программы управления и, следовательно, к снижению бьютродействйя устройства и к увеличению обьема па мяти программ, Цель изобретения - повышение быстродействия, и упрощение устройства путем уменьшения обьема памяти программ в системе управления, составной частью ко торой является данное устройство, путем аппаратной реализации контроля правильности установки триггеров выходного регистра. Поставленная цель достигается тем, что в устройство, содержащее дешифрато выходы которого через соответствующие элементы И и триггеры соединены с соо ветствующими информационными входами коммутатора и с выходами устройства, адресный вход коммутатора и вход дешифратора Ъодключены к адресной шине, вторые Ьходы элементов И подключены к шине синхронизации, вторые входы триггеров - к шине Запись 1, а третьи входы триггеров - к шине Запись О , ввеве ны последовательно соединенные элемент НЕ, первый дополнительный элемент И, элемент ИЛИ, второй дополнительный элемент И и триггер,третий дополнительный элемент И и элймент задержки, вьгход которого подключен к второму входу второго дополнительного элемента И, а вход - к шине синхронизации, выход коммутатора соединен с входом элемента НЕ и через третий дополнительный элемент И с вторым входом элемента ИЛИ, вторые входы первого и третьего дополни- , тельных элементов И подключены соответстственно к шинам Запись 1 и Запись О На чертеже показана схема предлагаемого устройства. Устройство управления содержит адресную шину I, шину 2 синхронизации, игану 3 Запись 1, шину 4 Запись О , де- дешифратор 5, группу элементов И 6,, группу триггеров 7 выходного регистра, коммутатор 8, элемент НЕ 9, первый дополнитель«ый элемент И 1О, второй дополнительный элемент И 11, элемент ИЛИ 12, третий дополнительный элемент И 13, триггер 14 ошибки и элемент 15 задержки. Адресная цщна 1 связана с входом дешифратора 5 и с адресным входом коммутатора 8. Выходы дешифратора 5 соединены с первыми входами элементов И 6 группы, вторые входы соединены с шиной 2 синхронизации, а выходы - с синхронизирующими входами f-K триггеров 7 выходного регистра. Шина Запись I соединена с Т -входами триггеров 7, а также с вторым входом первого дополнительного э;юмента И 10. Шина Запись О соединена с К-входами триггеров 7, а также с вторым входом второго дополнительного элемента И 11. Выходы трипгеров 7 соединены с исполнительными механизмами (не показаны) и с соответствующими информационными входами ком мутатора 8. Выход коммутатора 8 соединен с первым входом второго дополнительного элемента И 11 через элемент НЕ 9 с первым входом первого дополнительного элемента И 10. Выходы дополнительных элементов И 10 и 11 соединены с аламентом ИЛИ 12, выход которого соединен с первым входом третьего дополнительного Э1юмента И 13. Второй вход третьего дополнительного элемента И 13 соединен с шиной 2 синхронизации через элемент задержки 15, a выхоц - с вхо- аом Установка 1 триггера ошибки 14, агорой вхоа которого используется для усгановки его в исходное состо5шие. ycTjpoftcTBO работает слецующим образом. При поступлении кода адреса по адресной ишне I на вход дешифратора 5 последний подготавливает соответствующий элемент И 6 к прохождению через него импульса синхронизации. Одновременно с к00ом адреса подается сипгал либо по шине 3 Запись I, либо по иине 4 Запись О , в зависимости от того, в какое состояние должен быть установпэн выбранный триггер 7 выходного регистра Поступающий затем импульс по шине 2 синхронизации переводит триггер 7 в требуемое состояние. Так как адресный код . одновременно поступает и на коммутатор 8, то на его выходе появляется сигнал, соответствующий состоянию переключаемо го триггера 7. Этот сигнал совместно с сигналами на щинах Запись 1 и Запись О анализируется дополнительными элементами, введенными в устройство. При неправильной установке выбранного триггера 7 на выходе элемента ИЛИ 12 устанавливается единичный уровень, поэтому задержанный сигнал синхрстгазацни с шины 2 через третий дополнительный элемент И 13 устанавливает в единичное состо5шие триггер 14 ошибки. Условиями формирования единичного уровня сипнала на выходе третьего дополнительного элемента 13 5тляются единичный сигнал на шине 3 Запись I и нулевой сигнал на коммутатора 8, что приводит к срабатыванию первого дополнительного элемента И 10; единичный сигнал на шине 4 Запись О, и единичный сигнал на выходе коммутатора 8, что приводит к срабатыванию второго дополнительного элемента И 11, Из приведенного описания схемы и работы предлагаемого устройства видно, что при каждом переключении любого триггера 7 выходного регистра можно проконтролировать правильность его установки в требуемое состо5шие по выходному сягявпу триггера ошибки 14, При этом не требуются дополнительные затраты времени. Таким образом, предлагаемое техниче- ское решение позволяет аппаратными срец 63 6 твами осуществлять контроль правильнооустановки триггере выходного региста. Переход от программной реализадии онтроля к аппаратной приводит к уменьению числа: команд в программе управения, что, в свою очередь, обеспечивает меньшение требуемого объема памяти рограмм и повышение быстродействия стройства. Формула изобрет е н и я Устройство программного управления исполнительными механизмами, содержащее дешифратор, выходы-Которого через соответствующие элементы И и триггеры соединены с соответствующими информационными входами коммутатора и с В№ходами устройства, адресный вход комму Тагора и вход дешифратфа подключены к адресной шин вторые входы элементе И подключены к шине синхронизацни вгорые входы григгоров - к шине Запись I, а третьи входы триггеров - к щине Запись О, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, в него введены последовательно соединенные элемент НЕ, первый дополнительный элемент И, элемент ИЛИ, второй дополнительный элемент И и Tfsirrep, а также третий дополнительный элемент И и элемент задержки, выход которого подключен к второму вхог ау второго дополнительного элемента И, а вход - к шине синхронизации, выход коммутатора соединен с входом элемента НЕ и через третий дополнительный еле- МЙ1Т И с вторым входом элемента ИЛИ, вторые входы первого и третьего допел нительных элементов И подключены соответственно к шинам Запись I и О. Источники информации, принятые во внимание при экспертизе 1. Вешкобритании Ni 2О04О88, кл.5 05 В 15/02, опублик. 1977. 2.Патент Япогаш W 53-38394, кл, 5 О5 В 23/О2, опублик, 1978 (протопюК

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления исполнительными механизмами | 1980 |

|

SU1023285A2 |

| Многоканальный резервированный коммутатор | 1989 |

|

SU1737723A1 |

| Устройство для сопряжения ЭВМ с внешним абонентом | 1988 |

|

SU1594553A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| Устройство для отладки микропроцессорных систем | 1986 |

|

SU1462326A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для регенерации динамической памяти | 1980 |

|

SU943845A1 |

Авторы

Даты

1982-05-23—Публикация

1980-02-27—Подача