(5) УСТРОЙСТВО МИКРОПРОЦЕССОРНОЙ связи

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1980 |

|

SU955077A1 |

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 2012 |

|

RU2486581C1 |

| Устройство для ввода-вывода информации из накопителей на магнитных дисках | 1982 |

|

SU1019431A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| Устройство для сопряжения между ЭВМ, оперативной памятью и внешним запоминающим устройством | 1988 |

|

SU1531103A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

I

Изобретение относитея к вычислительной технике, в частности к средствам микропроцессорного управления, и может найти применение в системах управления сбора и обработки информации и измерительных системах.

Известно устройство, содержащее коммутаторы, триггеры, формирователи и регистр П }

Недостаток данного устройства большой объем оборудования.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее регистр состояний, первый коммутатор, двунаправленный коммутатор, три триггера, три формирователя сигнала, семь элементов И и элемент задержки ГЗ.

Недостаток известного устройстванизкая эффективность и надежность при организации обмена.

Цель изобретения - повышение коэффициента использования оборудования и его надежности.

Поставленная цель достигается тем

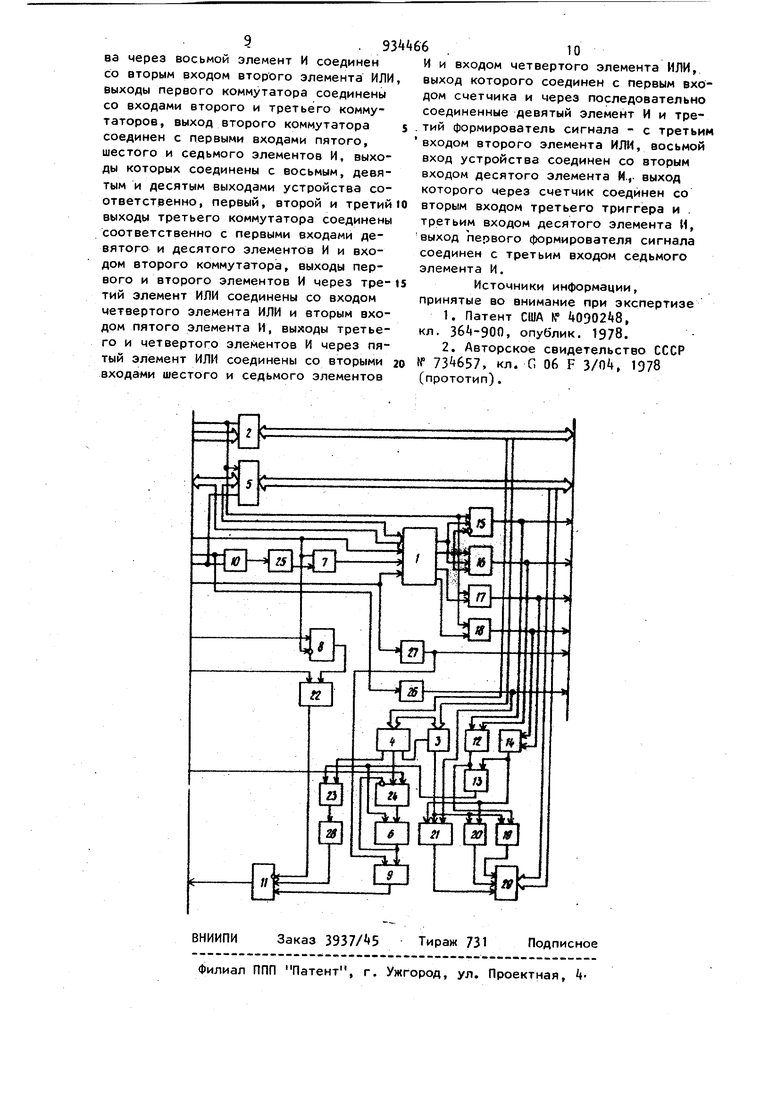

что в устройство микропроцессорной связи, содержащее первый коммутатор, группа входов которого соединена с первой группой входов устройства, группа выходов которого соединена с выходами первого коммутатора, двунаправленный коммутатор, соединенный двусторонними связями с шиной данных микропроцессора и общей шиной, регистр состояний, группа входов которого соединена со второй группой входов устройства, три триггера, три формирователя сигнала, семь элементов И и элемент задержки, выход которого соединен с первым входом первого триггера, выходы первого и второго формирователей сигнала соединены соответственно с первым и вторым вь1ходами устройства, выходы первого, второго, третьего и четвертого элементов И соединены соответственно с третьим, чет вертым, пятым и шестым выходами устройства, введены два кбммутатора. счетчик, пять элементов ИЛИ и три эл мента И, причем, первый вход устройства соединен со входом первого коммутатора и первыми входами двунаправ ленного коммутатора и первого, второ го, третьего и четвертого элементов И, второй вход устройства соединен со вторым входом первого триггера и первыми входами второго триггера и регистра состояний, первый выход которого соединен со вторыми входами первого и второго элементов И, третьи входы которых соединены со вторым выходом регистра состояний, третий и четвертый выходы которого соединены со вторыми входами соответственно третьего и четвертого элементов И,.третий вход устройсТЬа соединен со входом первого формирователя сигнала и первым входом первого элемента ИЛИ, выход которого соединен со входом элемента задержки, четвертый вход устройства соединен со вторыми входами двунаправленного коммутатора и первого элемента ИЛИ, пятый вход устройства соединен со вторым входом регистра состояний и через второй формирователь сигнала - с пер вым входом третьего триггера, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с седьмым выходом устройства, шестой вход которого соединен со вторым входом второго триггера, выхо которого соединен со входом восьмого элемента И, седьмой вход устройства через восьмой элемент И соединен со вторым входом второго элемента ИЛИ, выходы первого коммутатора соединены со входами второго и третьего коммутаторов, выход второго коммутатора соединен с первыми входами пятого, шестого и седьмого элементов И, выходы которых соединены с восьмым, девятым и десятым выходами устройства соответственно, первый, второй и третий выходы третьего коммутатора соединены соответственно с первыми входами девятого и десятого элементов И и входом второго коммутатора, выходы первого и второго элементов И через третий элемент ИЛИ соединены со входом четвертого элемента ИЛИ и вторым входом пятого элемента И, выходы третьего и четвертого элементов И через пятый элемент ИЛИ соединены со вторыми входами шестого и седьмого элементов И и входом четвер того элемента ИЛИ, выход которого соединен с первым входом счетчика и через последовательно соединенные девятый элемент И и третий формирователь сигнала - с третьим входом второго элемента ИЛИ, восьмой вход устройства соединен со вторым входом десятого элемента И, выход которого через счетчик соединен со вторым входом третьего триггера и третьим входом десятого элемента И, выход первого формирователя сигнала соединен с третьим входом седьмого элемента И. На чертеже приведена блок-схема устройства. Устройство содержит регистр 1 состояний, .коммутаторы 2-Ц, двунаправленный коммутатор 5, счетчик 6, триггеры . элементы ИЛИ 10-14, элементы И , элемент 25 задержки, формирователи 26-28 сигнала и внешнее устройство 29. Коммутатор 2 предусмотрен для разделения и сопряжения внутренней шины магистрали микропроцессора с внешней магисталью, а также для формирования уровней и фронтов адресных сигналов. Кроме того, коммутатор используют для отключения устройства от общей магистрали в случае передачи ее другому ведущему модулю в режиме работы многопроцессорной системы. Двунаправленный коммутатор 5 используют для сопряжения шин данных микропроцессора с общей магистралью. Регистр 1 предусмотрен для фиксации байта слова состояния микропроцессора. Внешнее устройство 29 обмена данными представляет собой ячейки памяти (.ОЗУ, ПЗУ, ППЗУ и т. д.; или порты считывания или записи информации из внешних устройств ввода-вывода и обозначает функциональное объединение памяти и портов. Предлагаемое устройство работает следующим образом. В первом машинном такте микропроцессор выставляет на коммутаторе 2 .адрес очередной команды. На регистре 1 микропроцессор выставляет код слова состояния. Это слово является байтом состояния микропроцессора, который определяет тип машинного цикла, к выполнению которого микропроцессор приступает в данный момент. Типь машинных циклов процессора могут быть: запись или считывание из памяти, обращение к стековой памяти, запись или считывание внешних устройств ввода-вывода разрешение прерывания и разрешение останова. Биты состояния микропроцес сора с выхода регистра 1 поступают на входы элементов И 15-18, в которых формируются магистральные команды чтения или записи. Имеется четыре типа магистральных команд: запись ин формации в устройство ввода-вывода, запись информации в устройство памяти, считывание информации из устройс ва ввода-вывода, считывание информации из устройства памяти, при помощи которых устройство посредством магистрали обращается к другим модулям системы. Взаимодействие микропроцессора с одной стороны и общей магистрали интерактивное. При обращении к внешнему устройству 29 микропроцессор в лю бом случае ожидает ответную реакцию этого устройства: готовность. Сигнал общей готовности формируется следующим образом. После возникновения одной из команд обращения активизируется один из входов ИЛИ 12 и И, элемент 12 функционально группирует команды записи, а элемент 14 - команды чтения. Обе группы объединяются далее на входах элемента ИЛИ 13 и с его выхода поступают на элемент И 23. На дру гой его вход с коммутатора 4 поступа ет разрешающий сигнал для адресных групп быстродействующих внешних устройств. Сформированный таким образом сигнал с элемента И 23 поступает через формирователь 28 на элемент ИЛИ 1 и с его выхода на выход устройства. Одновременно сигнал чтения поступае на элемент ИЛИ 10 и далее через элемент 25 на триггер 7. Одновременно происходит формирова ние команды для чтения информации с внешнего устройства обмена данными. Для этой цели с- вь1хода элемента ИЛИ И команда чтения поступает на вход эле мента И 19, а с выхода коммутатора 3 поступает разрешающий сигнал. Если в коммутаторе t внешние адреса определ ются по его быстродействию, то в ком мутаторе 3 происходит формирование сигнала разрешения для определенного адреса, или массива адресов подмножеств групп быстродействия. При совпадении этих сигналов на выходе элемента И 19 появляется команда чтения и на выходе внешнего устройства 29 выставляются выбранные данные, которые поступают на коммутатор 5Формирование сигнала задержанной готовности происходит в случае, если коммутатор 4 после дешифрации поступающего на его вход адреса определяет, что этот адрес входит в группу медленно действующих устройств. В этом случае активизируется выход коммутатора , сигнал с которого поступает на вход элемента И 2. Через открытый элемент И 2k импульсы проходят на счетчик 6, который начинает отсчет. После отсчета того числа имггульсов, на которое счетчик 6 запрограммирован, на его выходе возникает сигнал готовности, который поступает на вход запрета элемента И 24 и на вход триггера 9. В результате запрета элемента И 24 прекращается подача импульсов на вход счетчика 6, который останавливается в этом фиксированном положении. Для синхронизации с внешними синхроимпульсами на другой вход триггера 9 подаются магистральные синхроимпульсы. Сигнал задержанной готовности поступает на элемент ИЛИ 11 и далее на вход готовности микропроцессора. формирование готовности от команды записи происходит следующим образом. Команды записи функционально объединяются в элементе ИЛИ 14 и через элемент ИЛИ 13 поступают на вход элемента И 23 и на вход элемента И 24. В зависимости от того, какой из выходов коммутатора 4 активизируется, подобным образом, как при считывании, формируется сигнал опережающей или .задержанной готовности. Основные команды записи во внешнее устройство 29 обмена данными в конъюнкции с разрешающим сигналом коммутатора 3 формируются в элементе И 20. Через элемент И 21 дополнительная команда записи в конъюнкции с сигналом коммутатора 3 поступает на вход внешнего устройства 29. Сигнал чтения проходит через элемент ИЛИ 10, элемент 25 и поступает на вход триггера 7, который переключается и сбрасывает регистр 1 в исходное состояние, следовательно, кончается основная команда записи. В результате дейсгвия элемента 25 между задними фронтами основной команды записи и дополнительной команды записи образуется сдвиг по времени Т . Это необходимо

для устранения эффекта переходного процесса, который вызывается в шинах данных задним фронтом основной команды записи в случае совпадения с задним фронтом дополнительной команды записи. Эти переходные процессы могут быть фиксированы в ячейке памяти или регистра вывода внешнего устройства обмена данными и вызвать запись искаженной информации. Специфическим режимом задержанной готовности является работа микропроцессора в шаговом режиме.

Для перехода на шаговой режим на вход устройства поступает активный сигнал, который снимает запрет с элемента И 22. На другой его вход поступает сигнал, с выхода триггера 8, который активизируется передним фронтом синхроимпульса в начале каждого машинного цикла. Активный сигнал с выхода триггера 8 через открытый элемент И 22 поступает на вход запрета элемента ИЛИ П, в результате чего последний закрывается и блокирует поступление сигналов готовности внешнего устройства. Переход процессора к выполнению следующего машинного цикла осуществляется при подаче сигнала разрешения на триггер В. По переднему фронту этого сигнала три1- гер 8 устанавливается в положение, при котором на его выходе устанавливается сигнал, закрывающий элемент И 22, Вследствие этого снимается запрет с элемента ИЛИ 11 и сигналы готовности с других входов этого элемента проходят на седьмой выход устройства. Возврат триггера 8 в положение блокировки следующего шага происходит по переднему фронту синхроимпульса последующего машинного цикла, на котором микропроцессор переходит в состояние ожидания.

Для выхода из шагового режима необходимо снять активный сигнал со . входа устройства и тем самым подать запрет на вход элемента И 22.

Таким образом, предлагаемое устройство позволяет повысить эффективность обмена микропроцессора с магистралью при больших скоростях его работы и надежность за счет компенсации задержки распространения сигналов.

Формула изобретения

Устройство микропроцессорной связи, содержащее первый коммутатор, группа входов которого соединена с

Первой группой входов устройства, группа выходов которого соединена с выходами первого коммутатора, двунаправленный коммутатор, соединенный двусторонними связями с шиной данных микропроцессора и общей шиной, регистр состояний, группа входов которого соединена со второй группой входов устройства, три триггера, три формирователя сигнала, семь элементов И и элемент задержки, выход которого соединен с первым входом первого триггера, выходы первого и второго формирователей сигнала соединены соответственно с первым и вторым выходами устройства, первого, второго, третьего и четвертого элементов И соединены соответственно с третьим, четвертым, пятым и шестым выходами устройства, отличающееся тем, что, с целью повышения коэффициента использования оборудования и его надежности, в него введены два коммутатора, счетчик, пять элементов ИЛИ и три элемента И, причем первый вход устройства соединен со входом первого коммутатора и первыми входами двунаправленного коммутатора и первого, второго, третьего и четвертого элементов И, второй вход устройства соединен со вторым входом первого триггера и первыми входами второго триггера и регистра состояний, первый выход которого соединен со вторыми входами первого и второго элементов И, третьи входы которых соединены со вторым выходом регистра состояний, третий и четвертый выходы которого соединены со вторыми входами соответственно Третьего и четвертого элементов И, третий вход устройства соединен со входом первого формирователя сигнала и первым входом первого элемента ИЛИ, выход которого соединен со входом элемента задержки, четвертый вход устройства соединен со вторыми входами двунаправленного коммутатора и первого элемента ИЛИ, пятый вход устройства соединен со вторым входом регистра состояний и через второй формирователь сигнала - с первым входом третьего триггера, выход которого соединен с первым входом второго элемента ИЛИ, выход последнего соединен с седьмым выходом устройства, шестой вход которого соединен со вторым входом второго-триггера, выход последнего соединен со входом восьмого элемента И, седьмой вход устройства через восьмой элемент И соединен со вторым входом второго элемента ИЛИ выходы первого коммутатора соединены со входами второго и третьего коммутаторов, выход второго коммутатора соединен с первыми входами пятого, шестого и седьмого элементов И, выходы которых соединены с восьмым, девятым и десятым выходами устройства соответственно, первый, второй и третий выходы третьего коммутатора соединены соответственно с первыми входами девятого и десятого элементов И и входом второго коммутатора, выходы первого и второго элементов И через третий элемент ИЛИ соединены со входом четвертого элемента ИЛИ и вторым входом пятого элемента И, выходы третьего и четвертого элементов И через пятый элемент ИЛИ соединены со вторыми входами шестого и седьмого элементов 93 6 И и входом четвертого элемента ИЛИ, выход которого соединен с первым входом счетчика и через последовательно соединенные девятый элемент И и третий формирователь сигнала - с третьим входом второго элемента ИЛИ, восьмой вход устройства соединен со вторым входом десятого элемента И.,- выход которого через счетчик соединен со вторым входом третьего триггера и . третьим входом десятого элемента И, выход первого формирователя сигнала соединен с третьим входом седьмого элемента И. Источники информации, принятые во внимание при экспертизе 1.Патент США К A0902i 8, кл. 36i«-90fl, опублик. 1978. 2.Авторское свидетельство СССР № , кл. С Об F 3/04, 1978 (прототип).

Авторы

Даты

1982-06-07—Публикация

1981-03-04—Подача