1

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных устройств.

Известны вычислительные устройства для воспроизведения обратных функций til и t 2.

Недостатками известных устройств являются низкая скорость вычислений и значительные аппаратурные затраты.

Наиболее по технической сущности к предлагаемому устройству является устройство, содержащее три цифровых интегратора, один из которых (третий) является следящим, причем первые входы первого и второго интеграторов соединены со входом устройства, выходы первого и второго интеграторов соединены соответственно с первым и вторым входами третьего интегратора, выход которого соединен со вторыми входами первого и второго интеграторов С31.

При вычислении функции у - для

Л

значений х, приближающихся к нулю, погрешность вычислений в указанном устройстве резко возрастает.

Целью изобретения является повышение точности вычислений для значений X, близких к нулю.

С этой целью в устройство для вычисления обратной функции, содержаtoщее первый, второй и третий интеграторы, причем вход устройства соединен с первыми входами первого и второго интеграторов, а выход третьего интегратора подключен ко второму

15 входу второго интегратора, введены четвертый интегратор, первый, второй и третий сумматоры, регистр сдвига, Р гистр коррекции и коммутатор, при этом первый и второй входы первого

20 сумматора соединены с выходами со- . ответственно первого и второго интегратора, а выход первого сумматора присоединен к первомувходу третьего.

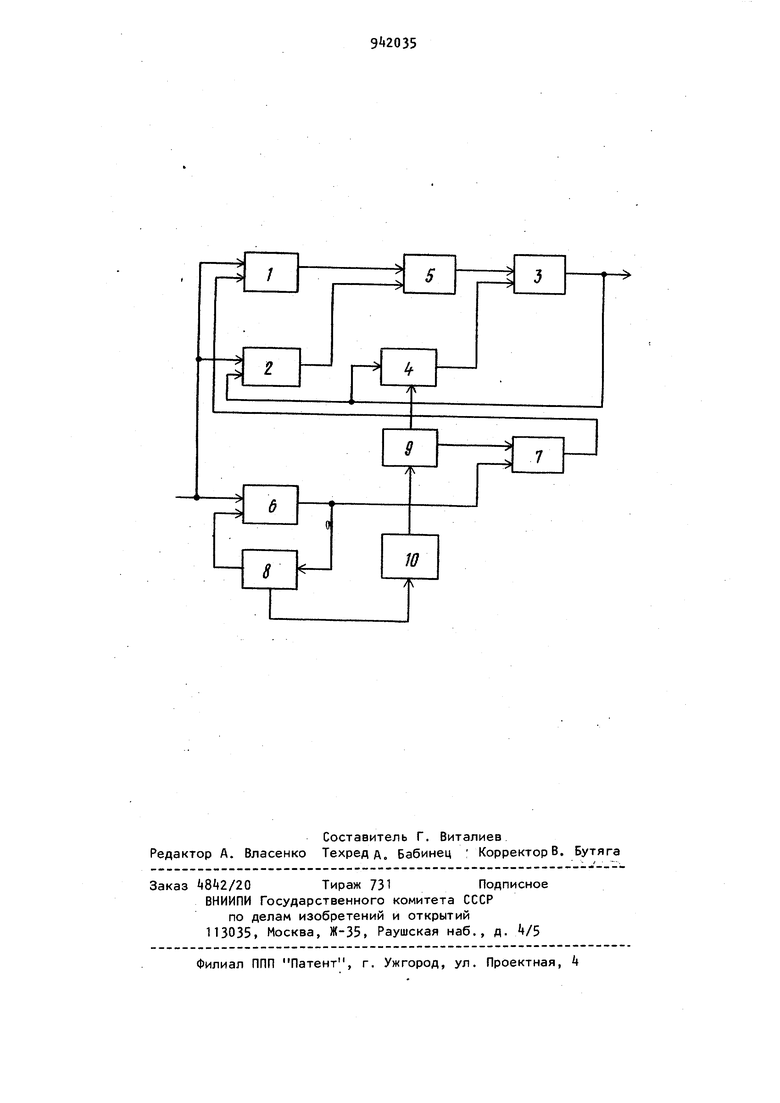

интегратора, выход которого соединен с первым входом четвертого интегратора, а выход четвертого интегратора подключен ко второму входу третьего интегратора, первый и второй входы второго сумматора соединены соответственно со входом устройства и первым выходом регистра сдвига, а выход второго сумматора подключен ко входу регистра сдвига и первому вХоду третьего сумматора, вход коммутатора соединен со вторым выходом регистра сдвига, а выход - со входом регистра коррекции, параллельный и последовательный выходы которого по ключены соответственно ко второму входу четвертого интегратора и второму входу третьего сумматора, выход которого соединен со вторым входом первого интегратора, причём, выход третьего интегратора является выходом устройства. За счет введения новых блоков и связей в предлагаемом устройстве значительно повышается устойчивость и точность вычислений для значений X, приближающихся к нулю. На чертеже приведена функциональ ная схема устройства. Устройство содержит первый, второй, третий и четвертый интеграторы 1 - Ц (интегратор 3 - следящий), первый, второй и третий сумматоры 5 - 7, регистр 8 сдвига, регистр 9 коррекции и коммутатор 10. Первые входы интеграторов 1 и 2 соединены со входом устройства, а выходы со входами сумматора 5, выход которого соединен с первым входом интег ратора 3, выход интегратора 3 соеди нен с выходом устройства, вторым входом интегратора 2 и первым входом интегратора 4. Первый вход сумматора 6 соединен со входом устройства, второй вход - с первым выходо регистра 8, а выход - с первым входом сумматора 7 и входом регистр 8.Второй выход регистра 8 соединен со йходом коммутатора 10, выход которого соединен со входом регистра 9,первый выход которого соединен со вторым входом интегратора k, а второй выход - со вторым входом сум матора 7. Выход сумматора 7 соедине со вторым входом интегратора 1. Работа устройства заключается в следующем. Перед началом вычислений на входы начальных значений подынтегральных функций интеграторов 1,2 и и в регистр 8 заносятся соответственно величины ff-oi o Хс

УО Хр. Вычисление функции у

начинается в устройстве с момента подачи- на вход устройства приращений dj. Приращения d поступают на первы входы интеграторов 1 и 2 и сумматора 6.-Проходя через сумматор 6 и накапливаясь в регистре 8, приращения d образуют текущее .значение переменной X, которое поступает на вход коммутатора 10. В этом коммутаторе в зависимости от значений х производится формирование корректирующего множителя od, значение которого записывается в регистр 9. Значение of,вырабатывается близким или равным х, но кратное 2, так, чтобы х pil X 0,12б, то с Например, если 0,125 2. Из регистра 9 значе ние cL параллельным кодом передается на второй вход интегратора-, а последовательным кодом - на вход сумматора 7, где из него вычитается значение х, поступающее из сумматора 6. Образованная в сумматоре 7 разность of.- X поступает на второй вход интегратора 1. С вы.ходов интегратора 1 и 2 на входы сумматора 5 поступает приращение dx, умноженное соответственно на величины ot-- х и у. Полученная сумма ( x).dx с выхода сумматора 5 поступает на первый вход следящего интегратора 3. С выхода следящего интегратора снимается приращение dy,поступающее на второй вход интегратора 2 и на первый вход интегратора Л. С выхода интегратора приращение dy, умноженное на величину оС , поступает на второй вход следящего интегратора 3. Предлагаемое устройство реализует дифференциальное уравне ние dy j-I(c6- x)dx - ydx .(1) при заданных начальных условиях, решением которого является функция у -5 . Дифференциальному уравнению (1) соответствует разностное уравнение .„,... й,,,.н.ь;,,, по которому ведутся вычисления в устройстве. Разностная схема (2) должна быть устойчивой, т.е. иметь решение, сводящееся к решению дифференциального уравнения (1) при h-50. Устойчивость схемы (2) опреде ляется следующим образом. Представи (2) в виде V н (2 i -1 ) i, V d d. I d4/ В евклидовом пространстве имеем , «Ч1И12-1 -ДМ--|:;.|.( Если и Н- о, то из (3) получаем г С, где С-ехр( ш b - аг , -} N J- , , b. Таким образом, из ограниченности оператора R, следует устойчивость и сходимость 12). За счет выбора параметра oL достигается ограниченность оператора R, для всех хеСа.Ь в то время как в известном устройстве ot 1 и ограниченность оператора имеет место не для всех значений Xjj а, Ъ.Методическая погреш ность равна f hoC Г,1 МIL V 2lL3J ;i J Следовательно, введение параметра незначительно увеличивает объем обо рудования , но позволяет вести вычис ления на всем интервале изменения переменной при заданной точности, так как вычислительная схема станов ся устойчивой и методическая погреш ность €-N) , Предлагаемое устройство предназн чено для использования в навигацион ных вычислителях, системах цифрово;го управления станками, в работах, микрокалькуляторах и другой радиоэлектронной аппаратуре. , Формула изобретения Устройство для вычисле ия обрат-. ной функции, содержащее первый, второй и третий интеграторы, причем вход устройства соединен с первыми входами первого и второго интеграторов, а выход третьего интегратора подключен ко второму вхОду второго интегратора, о тли ча-ющее с я тем, что, с целью повышения точности вычислений, оно содержит, четвертый интегратор, первый, второй и третий сумматоры, регистр сдвига, регистр коррекции и коммутатор, при этом первый и второй входы первого сумматора соединены с выходами соответственно первого и второго интегратора , а выход первого сумматора присоединен к первому входу третьего интегратора, выход которого соединен с первым входом четвертого интегратора, а выход четвертого интегратора подключен ко второму входу третьего интегратора, первый и второй входы второго сумматрра соединены соответственно со входом устройства и первым выходом регистра сдвига, а выход второго сумматора подключен ко входу регистра сдвига и первому входу третьего сумматора, вход коммутатора соединен со вторым выходом регистра сдвига, а выход со входом регистра коррекции, параллельный и последовательный выходы которого подключены соответственно ко второму входу четвертого интегратора и второму входу третьего сумматора, выход которого соединен со вторым входом первого интегратора, причем выход третьего интегратора является выходом устройства. Источники информации, принятые во внимание при экспертизе 1.Патент США № Зб+вОЗЗ, кл. G Об , 1971. 2.Авторское свидетельство СССР № , кл. G Об F 7/38, 1977. 3.Неслуховский К.С. Цифровые дифференциальные анализаторы. М., Машиностроение, 1968, с. 55, рис. 31.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления обратной функции | 1982 |

|

SU1137478A1 |

| Устройство для вычисления функции у= х | 1976 |

|

SU593210A1 |

| Устройство для цифрового дифференцирования | 1975 |

|

SU608145A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ВЕКТОРОВ И ДУГ НА ЭКРАНЕ ЭЛЕКТРОННО-ЛУЧЕВОЙ ТРУБКИ | 1990 |

|

RU2050021C1 |

| Стробоскопический цифровой измеритель с автоматической коррекцией нелинейности преобразователя | 1984 |

|

SU1218333A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР ПОСЛЕДОВАТЕЛЬНОГО ТИПА | 1970 |

|

SU281025A1 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Число-импульсное устройство для вычисления обратного тригонометрического тангенса | 1983 |

|

SU1092498A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

Авторы

Даты

1982-07-07—Публикация

1980-12-19—Подача