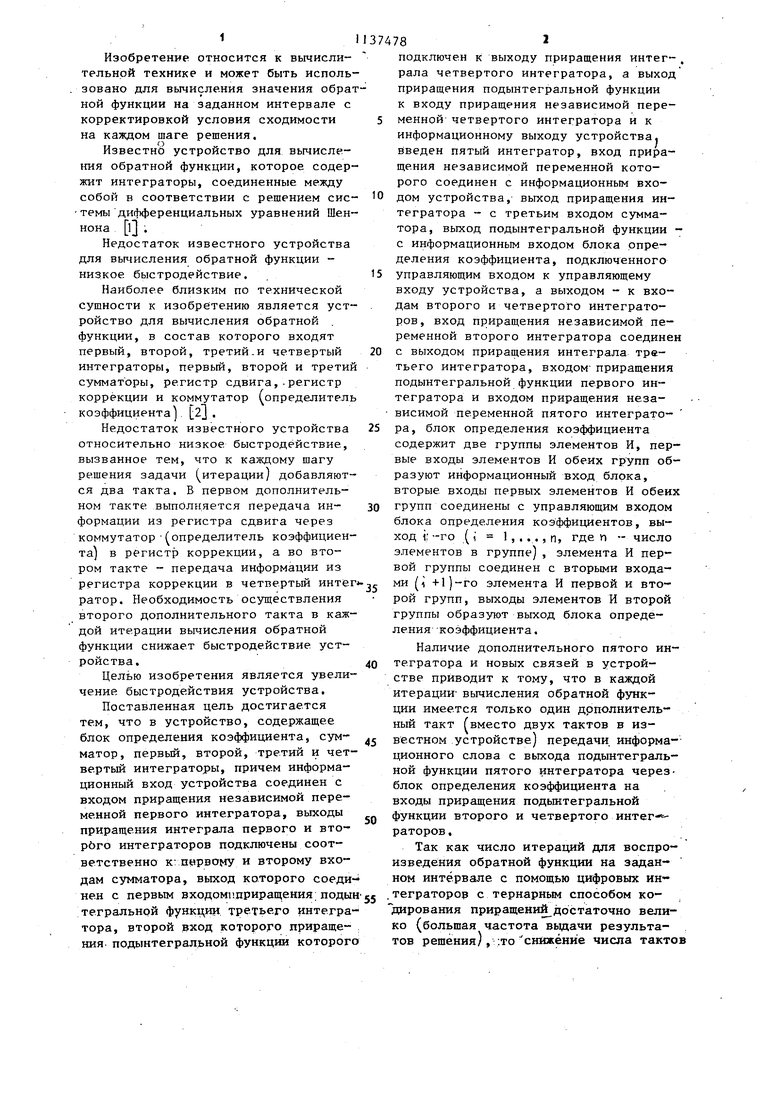

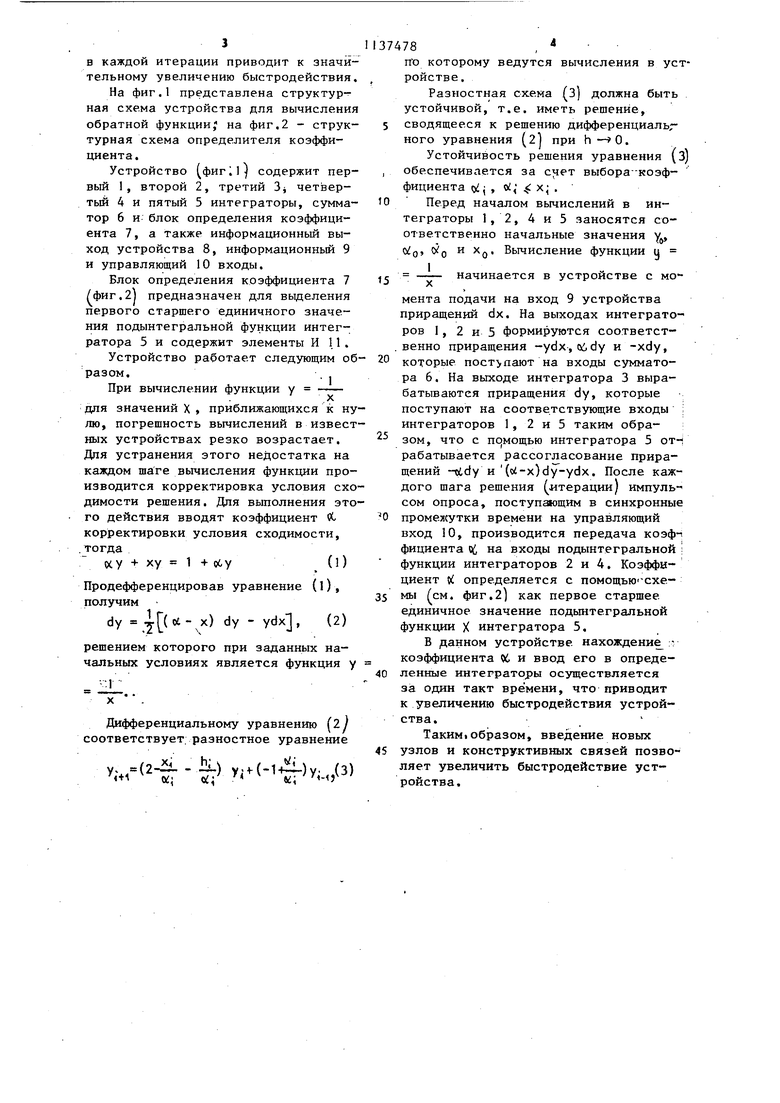

Изобретение относится к вычислительной технике и может быть исполь зовано для вычисления значения обра ной функции на заданном интервале с корректировкой условия сходимости на каждом шаге решения. Известно устройство для вычисления обратной функции, которое содер жит интеграторы, соединенные между собой в соответствии с решением сис темы дифференциальных уравнений Шен нона Q . Недостаток известного устройства для вычисления обратной функции низкое быстродействие. Наиболее близким по технической сущности к изобретению является уст ройство для вычисления обратной функции, в состав которого входят первый, второй, третий.и четвертый интеграторы, первый, второй и третий сумматоры, регистр сдвига,- регистр коррекции и коммутатор (определител коэффициента 2 , Недостаток известного устройства относительно низкое, быстродействие, вызванное тем, что к каждому шагу решения задачи (итерации) добавляются два такта. Б первом дополнительном такте выполняется передача информации из регистра сдвига через коммутатор -(определитель коэффициента) в регистр коррекции, а во втором такте - передача информации из регистра коррекции в четвертый инте ратор. Необходимость осуществления второго дополнительного такта в каж дой итерации вычисления обратной функции снижает быстродействие устройства. Целью изобретения является увели чение быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее блок определения коэффициента, сумматор, первый, второй, третий и чет вертьш интеграторы, причем информационный вход устройства соединен с входом приращения независимой переменной первого интегратора, выходы приращения интеграла первого и вторбго интеграторов подключены соответственно к: пврвому и второму входам сумматора, выход которого соеди нен с первым входомпприращения; поды тегральнрй функции третьего интегра тора, второй вход которого приращения подынтегральной функции которог 782 подключен к выходу приращения интег- . рала четвертого интегратора, а выход приращения подынтегральной функции к входу приращения независимой переменной четвертого интегратора и к информационному выходу устройства, введен пятый интегратор, вход приращения независимой переменной которого соединен с информационным входом устройства, выход приращения интегратора - с третьим входом сумматора, выход подынтегральной функции - с информационным входом блока определения коэффициента, подключенного управляющим входом к управляющему входу устройства, а выходом - к входам второго и четвертого интеграторов , вход приращения независимой переменной второго интегратора соединен с выходом приращения интеграла третьего интегратора, входом приращения подынтегральной функции первого интегратора и входом приращения независимой переменной пятого интеграто- ра, блок определения коэффициента содержит две группы элементов И, первые входы элементов И обеих групп образуют информационный вход блока, вторые входы первых элементов И обеих групп соединены с управляющим входом блока определения коэффициентов, выход i; -го (; 1,...,п, где и - число элементов в группе), элемента И первой группы соединен с вторыми входами (i +1)-го элемента И первой и второй групп, выходы элементов И второй группы образуют выход блока определения коэффициента. Наличие дополнительного пятого ин- тегратора и новых связей в устройстве приводит к тому, что в каждой итерации- вычисления обратной функции имеется только один дополнительный такт fвместо двух тактов в известном устройстве) передачи, информационного слова с выхода подынтегральной функции пятого интегратора черезблок определения коэффициента на входы приращения подьштегральной функции второго и четвертого интег-« раторов. Так как число итераций для воспроизве.де:ния обратной функции на заданном интервале с помощью цкфровых интеграторор с тернарным способом кодирования приращений достаточно велико (большая частота вьщачи результатов решения), .то снижение числа тактов в каждой итерации приводит к значительному увеличению быстродействия. На фиг . 1 представлена структурная схема устройства для вычисления обратной функции; на фиг.2 - структурная схема определителя коэффициента. Устройство ( содержит первый 1, второй 2, третий 3j четвертый 4 и пятый 5 интеграторы, сумматор 6 и блок определения коэффициента 7, а также информационный выход устройства 8, информационный 9 и управляющий 10 входы. Блок определения коэффициента 7 /фиг.21 предназначен для вьщеления первого старшего единичного значения подынтегральной функции интегратора 5 и содержит элементы И 11. Устройство работает следующим об разом. При вычислении функции у ДЛЯ значений X приближающихся к ну лю, погрешность вычислений в извест ных устройствах резко возрастает. Дпя устранения этого недостатка на каждом шаге вычисления функции производится корректировка условия схо димости решения. Для выполнения это го действия вводят коэффициент Л корректировки условия сходимости, .тогда (ХУ + ху 1+обу . Продефференцировав уравнение (l), получим dy .(ci- х) dy - ydx, (2) решением которого при заданных начальных условиях является функция у --. 5Г- . Дифференциальному уравнению (2 соответствует разностное уравнение ) У;И-.)у,„(з) i78, которому ведутся вычисления в устройстве. Разностная схема (З) должна быть устойчивой, т.е. иметь решение, сводящееся к решению дифференциальг ного уравнения (2 при . Устойчивость решения уравнения (з) обеспечивается за счет выбора-коэффициента (jij , 4 х- . Перед началом вычислений в интеграторы 1,2, 4 и 5 заносятся соответственно начальные значения у, , и XQ. Вычисление функции у начинается в устройстве с момента подачи на вход 9 устройства приращений dx. На выходах интеграторов I, 2 и 5 формируются соответст- венно приращения -ydx-, uidy и -xdy. которые поступают на входы сумматоpa 6. На выходе интегратора 3 вырабатываются приращения dy, которые поступают на соответствующие входы ; интеграторов 1, 2 и 5 таким образом, что с помощью интегратора 5 отн рабатывается рассогласование приращений -cidy и ()dy-ydx. После каждого шага решения (итерации) импульсом опроса, поступающим в синхронные промежутки времени на управляющий вход 10, производится передача коэф-i фициента на входы подынтегральной функции интеграторов 2 и 4, Коэффициент определяется с помощью|схе.- мы (см. фиг.2 как первое старшее единичное значение подьштегральной функции X интегратора 5. В данном устройстве нахождение :коэффициента 96 и ввод его в определенные интеграторы осуществляется за один такт времени, что приводит к увеличению быстродействия устройства. Таким«образом, введение новых узлов и конструктивных связей позволяет увеличить быстродействие устройства.

0иг.2

6 2,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1182515A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Устройство для вычисления цепных дробей | 1981 |

|

SU1008748A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ОБРАТНОЙ ФУНКЦИИ, содержащее блок определения коэффициента, сумматор, первый второй, третийи четвертый интеграторы, причем информационный вход устройства соединен с входом приращения независимой переменной Первого интегратора, выходы приращения интеграла первого и второго интег раторов подключены соответственно к первому и второму входам сумматора, выход которого-соединен с первым входом приращения подынтегральной функции третьего интегратора, второй вход приращения подынтегральной функции.которого подключен к выходу приращения интеграла четвертого интегратора, а выход приращения подынтегральной функции - к входу приращения независимой переменной четвертого интегратора и к информационному выходу устройства, о т - личаюшееся тем, что, с целью увеличения быстродействия, в него введен пятый интегратор, вход приращения независимой переменной которого соединен с информационным входом устройства, выход приращения интеграла - с третьим входом сумматора, а выход подынтегральной функции - с информационным входом блока определения коэффициента, подключенного управляющим входом к управляющему входу устройства, а выходом - к входам второго и четвертого интеграторов, вход приращения независимой пере.менной второго ин- . тегратора соединен с выходом приращения интеграла третьего интегратора, входом приращения подынтегральной функции первого интегратора и входом приращения-независимой переменной пятого интегратора, блок определения коэффициента содержит две группы элементов И, первые -входы СО элементов И обеих групп образуют информационный вход блока, вторые входы первых элементов И обеих групп соединены с управляющим входом блока определения коэффициента, выход -го оо элемента И первой груцпыЛ 1,... Л где ц - число элементов в группе) соединен с вторыми входами ( +1)-го элемента И первой и второй групп, выходы элементов И второй группы образуют выход блока определения коэффициента .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Майоров Ф.В | |||

| Цифровые интегрирующие машины | |||

| М., Машгиз, 1962, с | |||

| Способ очищения сернокислого глинозема от железа | 1920 |

|

SU47A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления обратной функции | 1980 |

|

SU942035A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-30—Публикация

1982-09-02—Подача