Изобретение относится к вычислительной технике и предназначено для применения в устройствах управления цифровых вычислительных машин с микропрограммным управлением.

Известно устройство микропрограммного управления, содержащее запоминающее устройство, регистры, дешифраторы, блок распределения элементарных операций и блок местного управления. В таком устройстве для задания адресе следующей микрокоманды применяются естественный или принудительный способы адресации. Принудительный способ адресации (задание адреса следующей микрокоманды в текущей микрокоманде) является более гибким, хотя естественный способ адресации (расположение .микрокоманд в последовательных ячейках памяти) и формирование адреса следующей микрокоманды по увеличению содержимого счетчика адреса на 1 позволяет сократить разрядность микрокоманды и, тем самым , объемооборудование устройства управления в целом fl.

Недостатком известного устройства является большой объем оборудования.

Наиболее близким техническим решением к предложенно является устройство, содержащее запоминающий блок, регистр адреса, распределительный блок, блок местного упр авления, элег мент задержки, блокпереключения, содержащий элемент ИЛИ, шесть элементов И, причем выходы блока местного управления подключены к управ10ляющим входам регистра адреса, выход которого подключен к входу запоминающего блока, первая группа входов блока местного управления подключена к первой группе входов

15 устройства, выходы п разрядов запоминс1ющего блока подключены к первому входу распределительного блокаГ23.

Недостатком известного устройства является большая разрядность микро20команды, что приводит -к увеличению объема запоминаю1иего блока и всего устройства в целом.

Цель изобретения - упрощение устройства за счет сокрацения объема за- 25поминающего блока.

Поставленная цель достигается тем, что в устройство введены дешифратор управления, буферный регистр, элемент И, выход которого подключен

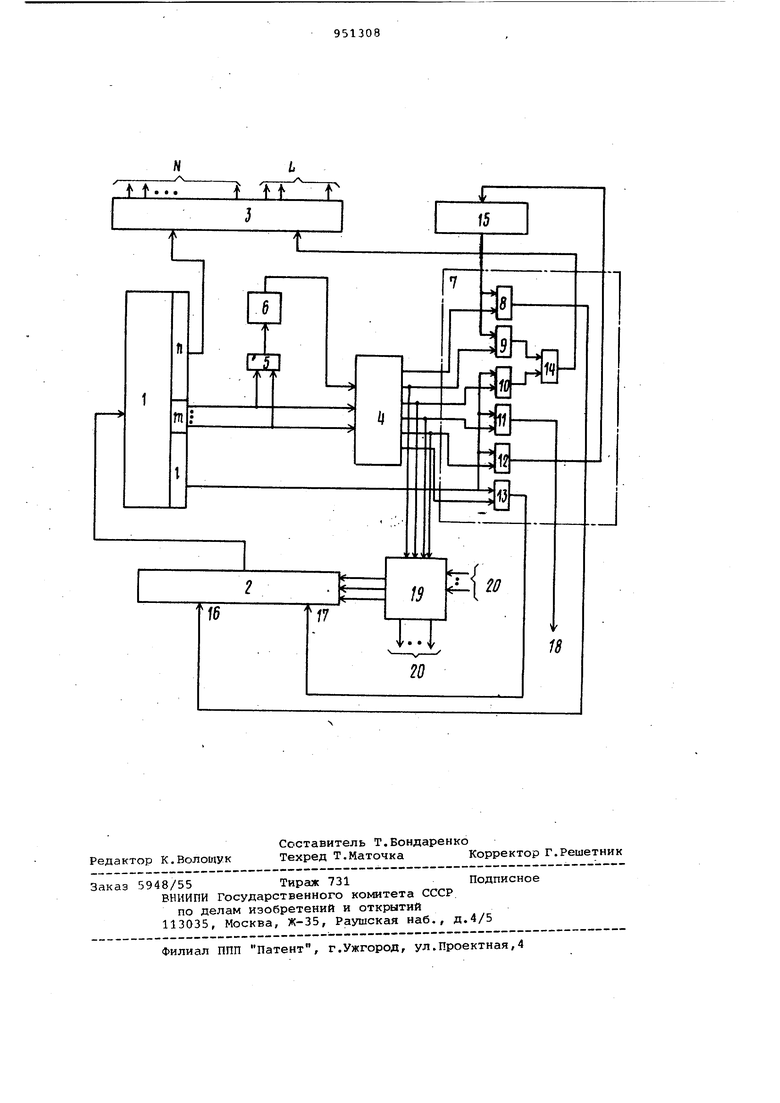

30 через элемент задержки к первому входу дешифратора управления, другие входы которого соединены с соответствующими входами элемента И и выхо дами m разрядов запоминающего блока выходы f разрядов которого подключе ны к информационным входам первого, второго, третьего, четвертого элементов И блока переключения, информационные входы пятого и шестого эл ментов И блока переключения соедине с выходом буферного регистра, вход которого соединен с выходом второго элемента И Гэлока переключения, первый и шестой выходы дешифратора упр ления подключены соответственно к управляющим входам первого и шестог элементов И блока переключения,- управляющие входы второго, третьего, четвертого и пятого элементов И бло ка переключения соединены с одноиме ными выходами дешифратора управлени и с второй группой входов блока мес ного управления, выходы четвертого и пятого элементов И блока переключения подключены соответственно к первому и второму входам элемента ИЛИ блока переключения, выход элеме та ИЛИ которого подключен к второму входу распределительного блока, выходы которого соединены с группой выходов устройства, выходы первого и шестого элементов И блока переключения соединены соответственно с первым и вторым информационными вхо дами регистра адреса, выход третьего элемента И блока переключения соединен с выходом устройства. На чертеже приведена схема предлагаемого устройства микропрограммн го управления. Запоминающий блок 1 связан по входу с регистром адреса 2, по разрядам п - с первыми входами ра.спределительного блока 3| по разрядам m - с входами дешифратора управления 4 и элемента И 5, выход которог через элемент задержки 6 подключен также к входу дешифратора управления 4.Блок переключения 7 содержит элементы И.8 - 13, а также элемент ИЛИ 14, входы которого.подключены соответственно к выходам элементов И 9 и 10, а выход подключен к вторым входам распределительного блока 3. Управляющие входы всех элементов И блока переключения подключены к соответствующим выходам дешифратора управления 4. Информационные входы элементов И 10 13 подключены к выходам разрядов запоминающего блока 1. Информационные входы элементов И 8 и 9 подключены к выходу буферного регистра 15. Выход элемен тов И 8 подключен к входам старших разрядов 16 регистра адреса 2, а выходы младших разрядов 17 регистра адреса 2 подключены к JBMXOду элемента И 13. Выход элемента И 11 подключен к выходу устройства 18. Выход элемента И 12 подключен к входам буферного регистра 15. Блок местного управления 19 имеет первую группу входов 20 (признаков условий ветвления). Блок местного управления 19 также подключен к управляющим входам регистра адреса 2. Запоминающий блок 1 предназначен для хранения и выдачи микрокоманд, регистра адреса 2 - для приема, хранения и выг, дачи адреса микрокоманды в запоминающее устройство 1, распределительный блок 3 - для выработки и распределения управляющих сигналов в зависимости от значения разрядов микрокоманды. Элемент 5 и элемент задержки 6 служит для выработки и задержки на один цикл работы устройства сигнала, свидетельствующего о наличии определенного кода на выходах разрядов запоминающего блока 1, блок переключения 7 - для коммутации засылки разрядов С микрокоманды либо в распределительный блок 3 через элемент ИЛИ 14, либо в старшие разряды 16 регистра адреса микрокоманд 2 через элемент И 8, либо в младшие разряды 17 через элемент И 13, либо в буферный регистр 15 через элемент И 12, либо через элемент И 11 на выход 18. Буферный регистр.15 предназначен для временного- хранения разрядов , микрокоманды, блок местного управления 19 - для синхронизации pa6oTi3 узлов устройства. Выход устройства 18 служит для подключения информационных входов операционного устройства вычислительной машины, либо для связи с управляющими входами устройств, подключаеких к машине с целью увеличения ее функциональных возможностей {арифметического расширителя, дополнительные внешние устройства и т.д.). В первом случае информация, поступающая на выход 18, может обрабатываться в текущем или последующих циклах как операнд, а во втором случае служит для выработки сигналов, управляющих работой подключенных : устройств. Предлагаемое устройство работает следующим образом. Под воздействием сигналов блока местного управления 19 адрес микрокоманды из регистра алреса 2 поступает на вход запоминающего блока 1. Через некоторое время, равное времени считывания запоминающего блока 1, на его выходах появляется код микрокоманды, содержащий (n+m-i-t) разрядов. При этом п разрядов поступают на первые входы распределительного блока 3 и участвуют в формировании N управляю1т1их сигналов операций, где величина N является функцией количества разрядов п и зависит от способа,кодирования этих разрядов. Разряды t постудают на входы элементов И 10 13 блока 7, а разряды m - на.входы дешифратора управления 4 и элемента 5. Возбуждается один из выходов дешифратора управления 4 и открывает соответствуклций элемент И блока пере лючения 7. Если открывается элемент И 10, то разряды передаются через элемент ИЛИ 14 на вторые входы блока 3 и участвуют в формировании L управ ляющих сигналов. Таким образом, общее количество вырабатываемых при этом сигналов определяется мощностью суммарного множества микроопераций (N4L). Одновременно с этим выход дешифратора управления 4 открывает эле мент И 10, возбуждает 5лок местного управления 19 по одному из соответствукяцих входов 10. Блок местного управления 19 вырабатывает сигнал, который поступает на соответствующий вход регистра адреса 2 и увеличивает его содержимое на единицу, формируя адрес следующей микрокоманды (естест венная адресация 7, Естественная адресация осуществляется также, когда открывается один из элементов И 11, 12 и 9 и осуществляется передача разрядов 6 соответственно на внешнюю информационную шину 18, на регистр 15 или передача содержимого этого регистра на вторые входы блока 3 через элемент ИЛИ 14. Если открывается элемент И 13, разряды поступают в младдаие разряды 17 регистра адреса микрокоманды 2 под воздействием управляющего сигнала с выхода блока 19, образуя адрес следующей микрокоманды способом принудительной адресации в преде лах сегмента микропрограммной памяти, номер которого определяется содержимым старших разрядов 16 регистpa 2. Изменение номера сегмента осуществляется засылкой кода из буферного регистра 15 через элемент И. -: Принудительная адресация в пределах всего объема микропрограммной памяти осуществляется при одновременном отк рытии элементов И 8 и 13. При этом код в буферный регистр 15 должен быть занесен в одной из предыдущих микрокоманд. В режиме принудительной адресации распределительный блок 3 может вырабатывать управл51ющие сигна лы только на выходах N под воздействием разрядов п запоминающего блока 1 (разряды t передаются при этом в качестве кода следукхцего гщреса на регистр адреса 2). Однако при перерсодах внутри сегмента мощность. мик- рокоманды может не уменьшаться,tak как если дешифратор управления 4 открывает одновременно элементом И 13 элемент И 9,на входы распределительного блока 3подается содержимое регистра 15, и могут вырабатываться сигналь на всех (N-H) выходах блока 3. Кроме того, буферный регистра 15 oжeт служить в качестве регистра косвенного или остаточного управления и, тем самым, позволяет уменьшить объем микропрограммной памяти. В частности, если есть несколько микропрограмм, отличающихся только одной микрокомандой, например, направлением или видом сдвига, выполняемым над операндом, или ВЫПОЛНЯ1ЭЩИХ одинаковые операции над содержимым разных регистров . Ссложить с аккумулятором А, сложить с аккумулятором Б и др),. то вид сдвига или номер аккумулятора предварительно заносится из разрядов t запоминающего устройства 1 в буферный регистр 15, а в общей микропрогррмме при помощи разрядов m указывается необходимость передачи содержимого регистра 15 через элемент И 9 и элемент ШШ 14 на вторые входы блока 3. Характер использования разрядов в текущей микрокоманде, а также содержимого буферного регистра 15 определяется разрядами m как текущей, так и предыдущей микрокоманд, так как на входы дешифратора управления 4 поступают сигналы не только с выходом разрядов m запоминакнцего устройства 1, но и с выхода элемента И 5 через элемент задержки 6. Элемент И 5 проверяет наличие в разрядах m определенного кода (для этого на соответствующие ВХОДЫ элемента И подаются прямые или инверсные значения выходов разрядов т), а элемент задержки 6 задерживает сигнал на выходе элемента И 5 до следующего цикла (до появления , на входах дешифратора управления 4 разрядов m следукяцёй микрокоманду . Таким образом обеспечивается интерпретация последующего кода в разрядах m в зависимости от предыдущего и тем самым уменьшается необходимое количество разрядов т. Условные переходы в предлагаемом устройстве реализуются путем модифиг кации адреса микрокоманды блоком местного управления 19 по управляющим входам в соответствии с признаками условий ветвлений, поступающими на группу входов 20. Таким образом, предлагаемое техническое решение позволяет упростить устройство за счет сокращения объема запоминающего блока. Оно внедряется в микро-ЭВМ, выполненной на больших интегральных схемах. Формула изобретения Устройство микропрограммного управления, содержащее запоминающий

6J3OK, регистр адреса, распределительннй блок г блок местного управления, элемент задержки, блок переключения, содержащий элемент ИЛИ, шесть элементов И, причем выходы блока 1« стного управления подключены к управляющим входам регистра адреса, выход которого подключен ко входу запоминающего блока, первая группа входов блока местного управления подключена к первой группе входов устройства, выходы п разрядов запоминающего блока подключены к первому входу .распределительного блока, отличающееся тем, что, с целью упрощения устройства за счет сокращения объема запоминающего блока, в устройство введены де|11Ифратор управления, буферный регистр, элемент И, выход которого подключен через элемент задержки к nepBor/iy входу дешифратора управления, другие входы которого соединены с соответствующими входами элемента И и выходами т -разрядов запоминающего блока, выходы 6 - разрядов которого подключены к информационным входам первого, второго, третьего, четвертого элементов И блока переключения, информационные входы пятого и шестого элементов И блока переключения соединены с выходом буферного регистра, вход которого соединен с выходом второго элемента И блока переключения, первый и шестой выходы десшфратора управления подключены соответственно к управляющим входам первого и шестого элементов И блока переключения, управляющие входы второго, третьего, четвертого и пятого элементов И блока переключения соединены с одноименными выходами дешифратора управления и со второй группой вхо- , дов блока местного управления, выходы четвертого и пятого элементов И блока переключения подключены соответственно- к первому и второму входам элемента ИЛИ блока переключения, выход элемента ИЛИ которого подключен ко второму входу распределительного блока, выходы которого соединены с группой выходов устройства, выходы первого и шестого элементов И блока переключения соединены соответственно с первым и вторым информационными входами регистра адреса, выход третьего элемента И блока переключения соединен с выходом устройства,

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 264783, кл. G ОбР 9/16.

2.Авторское свидетельство СССР № 3217066, КЛ.С Об F 9/16, 22.03,67

Ч прототип,

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство КЭШ-памяти | 1988 |

|

SU1675881A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство микропрограммного управления | 1981 |

|

SU985788A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1983 |

|

SU1108447A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

Авторы

Даты

1982-08-15—Публикация

1976-05-03—Подача