(5) УСИЛИТЕЛЬ СЧИТЫВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1980 |

|

SU938316A1 |

| Усилитель считывания на КМДП - транзисторах | 1986 |

|

SU1348904A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Усилитель считывания (его варианты) | 1983 |

|

SU1137923A1 |

| Усилитель считывания | 1981 |

|

SU970461A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Выходное буферное устройство | 1980 |

|

SU908230A1 |

| Статическая ячейка памяти на мдп- ТРАНзиСТОРАХ | 1979 |

|

SU799004A1 |

1

Изобретение относится к вычислительной технике и может быть использовано для создания запоминающих устройств на НДП-транзисторах и ПЗС.

Известны уси/тители считывания, предназначенные для считывания информации из накопителей запоминающих устройств, выполненных на однОтранзисторных .запоминающих ячейках памяти на МДП-транзисторах. Усилитель считыва- ,д ния, используемый в качестве адресной защелки и представляющий собой триггерную схему, информация на внутренние информационные узлы которой задается входным транзистором, описан в J5 литературе

Недостаток схемы - малое быстродействие вследствие наличия дополнительного такта, необходимого для формирования напряжения на внутренних 20 информационных узлах, и перезарядка больших емкостей внутренних информационных узлов в процессе работы формирователя.

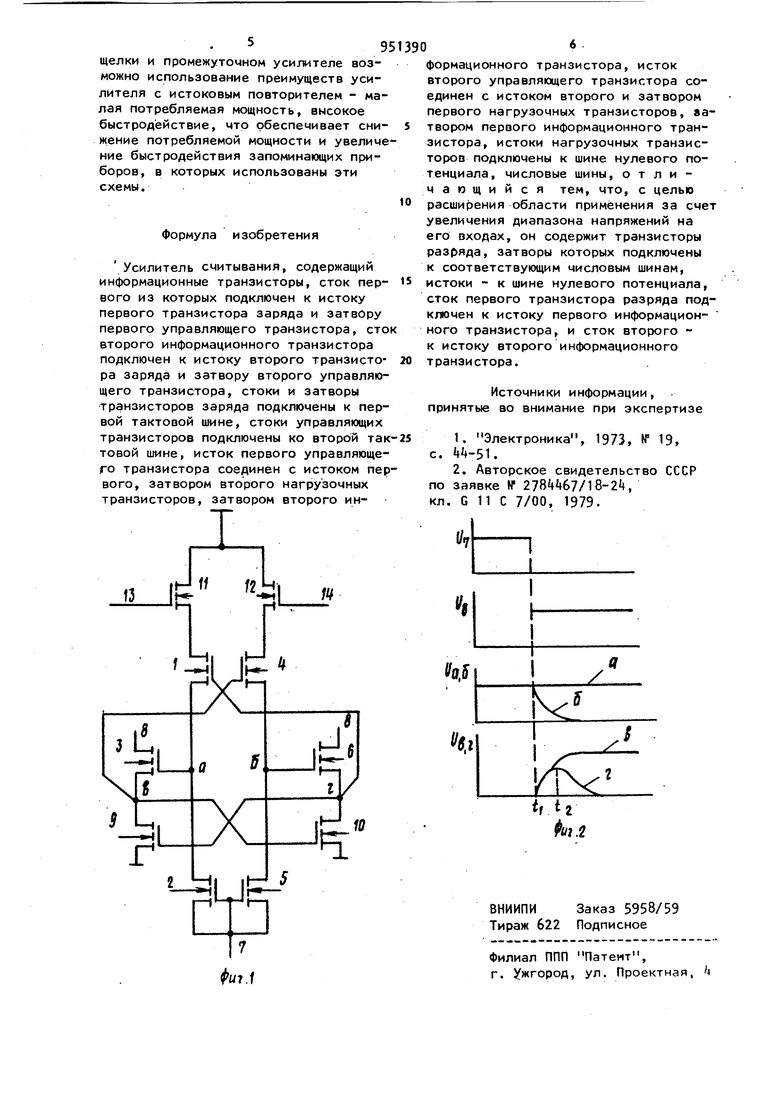

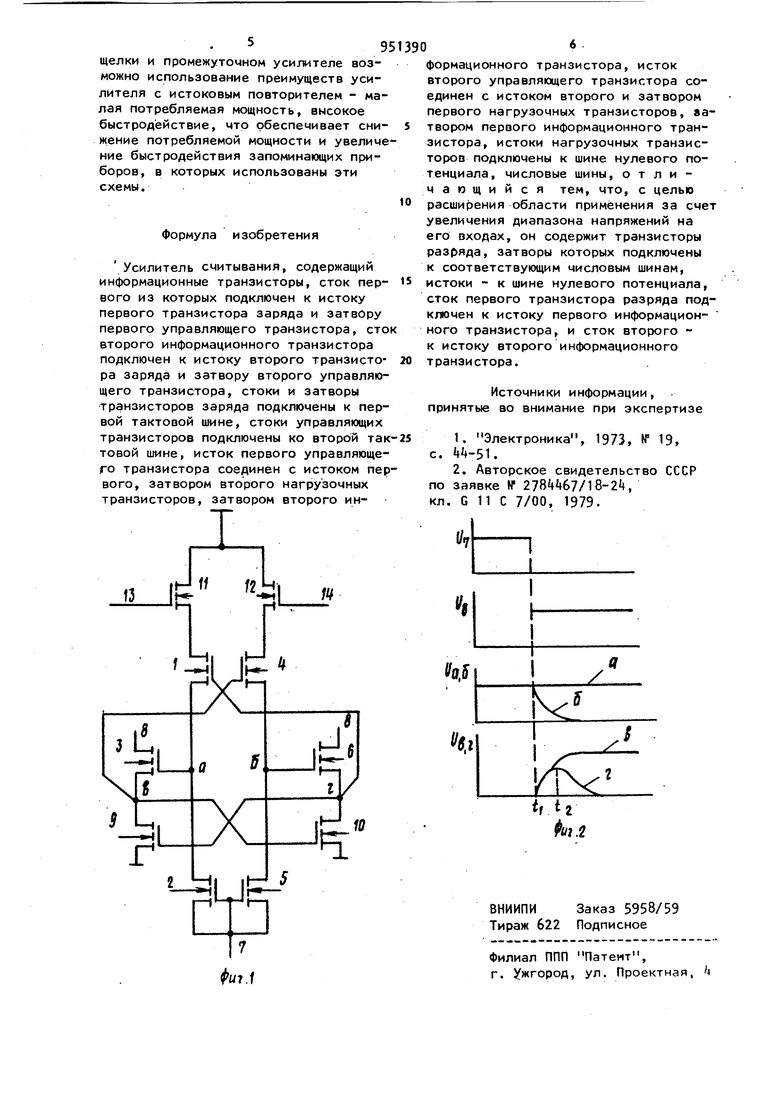

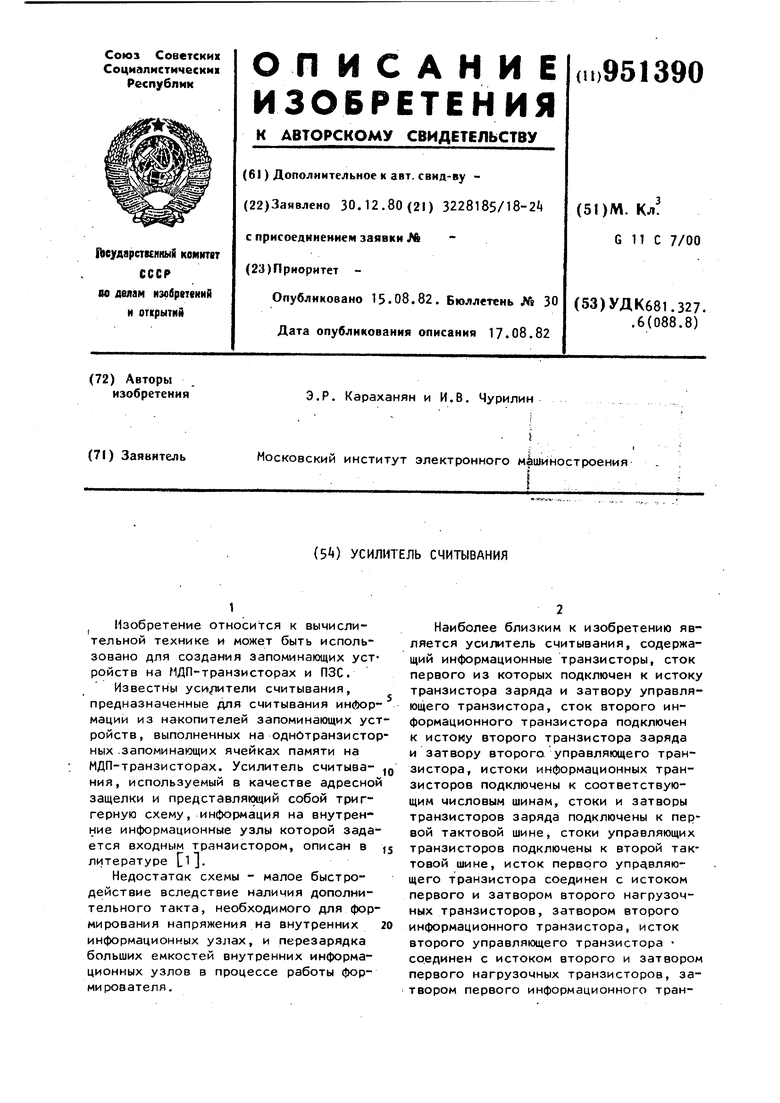

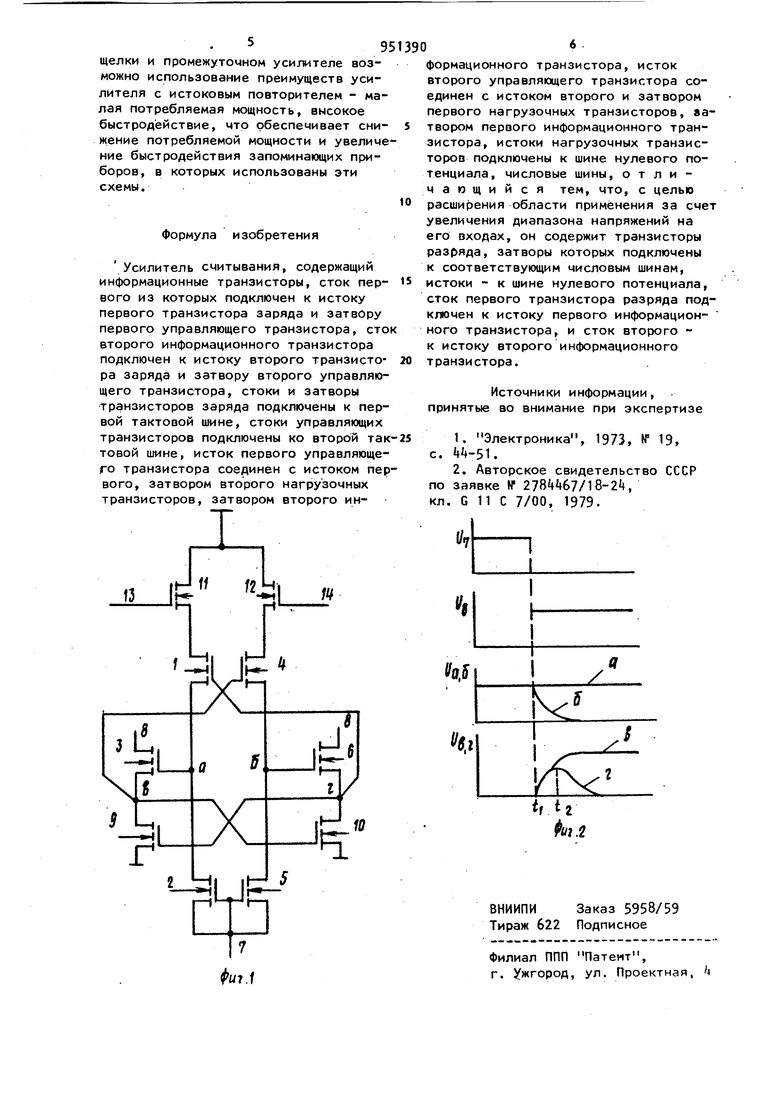

Наиболее близким к изобретению является усилитель считывания, содержащий информационные транзисторы, сток первого из которых подключен к истоку транзистора заряда и затвору управляющего транзистора, сток второго информационного транзистора подключен к истому второго транзистора заряда и затвору второго управляющего транзистора, истоки информационных транзисторов подключены к соответствующим числовым шинам, стоки и затворы транзисторов заряда подключены к первой тактовой шине, стоки управляющих транзисторов подключены к второй тактовой шине, исток первого управляющего транзистора соединен с истоком первого и затвором второго нагрузочных транзисторов, затвором второго информационного транзистора, исток второго управляющего транзистора соединен с истоком второго и затвором первого нагрузочных транзисторов, затвором первого информационного транзйстора, истоки нагрузочных транзиЬт ров подключены к шине нулевого потенциала, числовые шины. Данный усилитель считывания обладает высокой чувствительностью, высоким быстродей ствиом и малым потреблением мощноети Г2. Однако он работает от предварител ного разряда числовых шин, что ограничивает область его применения. Цель изобретения - расширение области применения усилителей считывания за счет увеличения диапазона напряжений на его входах. Цель достигается тем, что в усили тель считывания, содержащий информац онные транзисторы,сток первого из ко торых подключен к истоку первого тра зистора заряда и затвору первого упр ляющего транзистора, сток второго ий формационного т-ранзистора подключен к истоку второго транзистора заряда и затвору второго управляющего транзистора, стоки и затворы транзисторов заряда подключены к первой тактовой шине, стоки управляющих транзисторов подключены к второй тактовой шине, исток первого управляющего тра зистора соединен с истоком первого, затвором второго нагрузочных транзисторов, затвором второго информационно го транзистора, исток второго управля ющего транзистора соединен с истоком второго и затвором первого нагрузочных транзисторов, затвором первого ин формационного транзистора, истоки нагрузочных транзисторов подключены к шине нулевого потенциала, числовые шины, введены транзисторы разряда, затворы которых подключены к соответствующим числовым шинам, истоки - к шине нулевого потенциала, сток первого транзистора разряда подключен к истоку первого информационного транзи тора и сток - к истоку второго информационного транзистора. На фиг. 1. представлена схема усилителя считывания; на фиг. 2 - временная диаграмма его работы. Усилитель считывания состоит из ин формационного транзистора 1, сток которого подключен к истоку первого транзистора 2 заряда и затвору первого управляющего транзистора 3, сток второго информационного транзистора k подключен к истоку второго транзисто ра 5 и затвору второго управляющего транзистора 6, сто.ки и затворы транзисторов заряда подключены к первой тактовой шине 7, стоки управляющих транзисторов подключены к второй тактовой шине 8, исток первого управляющего транзистора 3 соединен с истоком первого Э, затвором второго 10 нагрузочных транзисторов, затвором второго информационного транзистора 4; исток второго управляющего транзистора 6 соединен с истоком второго 10 и затвором первого 9 нагрузочных транзисторов, затвором первого информационного транзистора 1 , сток первого транзистора разряда 11 подключен к истоку первого информационного транзистора 1, сток второго транзистора разряда 12 подключен к истоку второго информационного транзистора k, затворы транзисторов 11 и 12 разряда подключены к соответствующим числовым шинам 13 и 14, истоки нагрузочных транзисторов 9 и 10 и транзисторов 11 и 12 разряда подключены к шине нулевого потенциала.j Усилитель считывания работает следующим образом. В исходном состоянии (до момента времени t., фиг. 2) 1)7 Е. Напряжение на числовой шине 13 равно а на шине - ().., составляющее пол сумму величин напряжений,на числовой шине 13 при считывании логического О и логической 1 (опорное напряжение). Транзисторы 3 и 6 открыты, а так как Ug О, то транзисторы 9 и 10, 1 и 4 закрыты. С момента времени t. и О 3 б высокое. Напряжение на узлах и 2. возрастает и в момент времени t- открываются информационные транзисторы 1 и 4. За счёт разности сопротивлений транзисторов 1 1 и 12 разряда, разряд одного из узлов, например,5 происходит быстрее, и напряжение в этом узле уменьшится до О, а в узле а за счет положительной обратной связи, останется высоким. Введение в усилитель считывания транзисторов разряда обеспечивает работу усилителя от более широкого диапазона напряжений на его входе и уровня предварительного заряда, что в свою очередь обеспечивает расширение области применения усилителя считывания. Предложенная схема усилителя считывания расширяет область применения прототипа-усилителя считывания с истоковым повторителем и делает его схему универсальной для создания ЗУПВ. В созданных на ее основе адресной за- .

Авторы

Даты

1982-08-15—Публикация

1980-12-30—Подача