Изобретение относится к вычислительной технике.

Известно арифметическое устройство последовательного действия, содержшцее регистры слагаемых, элементы И, ИЛИ, триггер и блок управления 1J.

Однако это устройство характеризуется огрсшиченными фун кциональным возможностями, поскольку число операндов ограничено двумя и отсутствует возможность операции одновременного сложения-вычитания.

Наиболее близким по технической сущности к предлагаемому является последовательный цифровой сумматор/ содержащий регистр слагаемых, iTi элементов И, элемент ИЛИ, генератор тактовой частоты и распределитель импульсов {2.

Недостатком этого устройства является невозможность одновременного сложения и вычитания п чисел, подаваекых последовательными кодами младшими разрядами вперед.

Цель изобретения - расширение класса решаекых задач за счет получения возможности в|1читания п чисел, подаваемых последовательными кодами мпгщшими разрядами впереЛ

Поставленная цель достигается тем, что в последовательный сумматор, содержащий регистр слагаемых,п элементов И, элемент ИЛИ, генератор тактовой частоты и распределитель импульсов, причем п выходов регистра слагаемых соединены соответственно с первыми входами п элементов И,вторые входы которых соединены соответ10ственно с п выходами распределителя импульсов, вход которого соединен с выходом генератора тактовой частоты, ) h выходов элементов И соединены.со- ; ответственно с И входами элемента

15 ИЛИ, введены счетчик, регистр цикла, триггер .цикла, триггер устаноззки в ноль и блок управления, содеркащий первый, второй, третий и четвертый элементы И, первый вход первого эле20мента И блока управления- соединен с выходом первого разряда регистра цикла, первый-вход .второго элемента i блока управления соединен с выходом третьего разр1Зда регистра цикла,

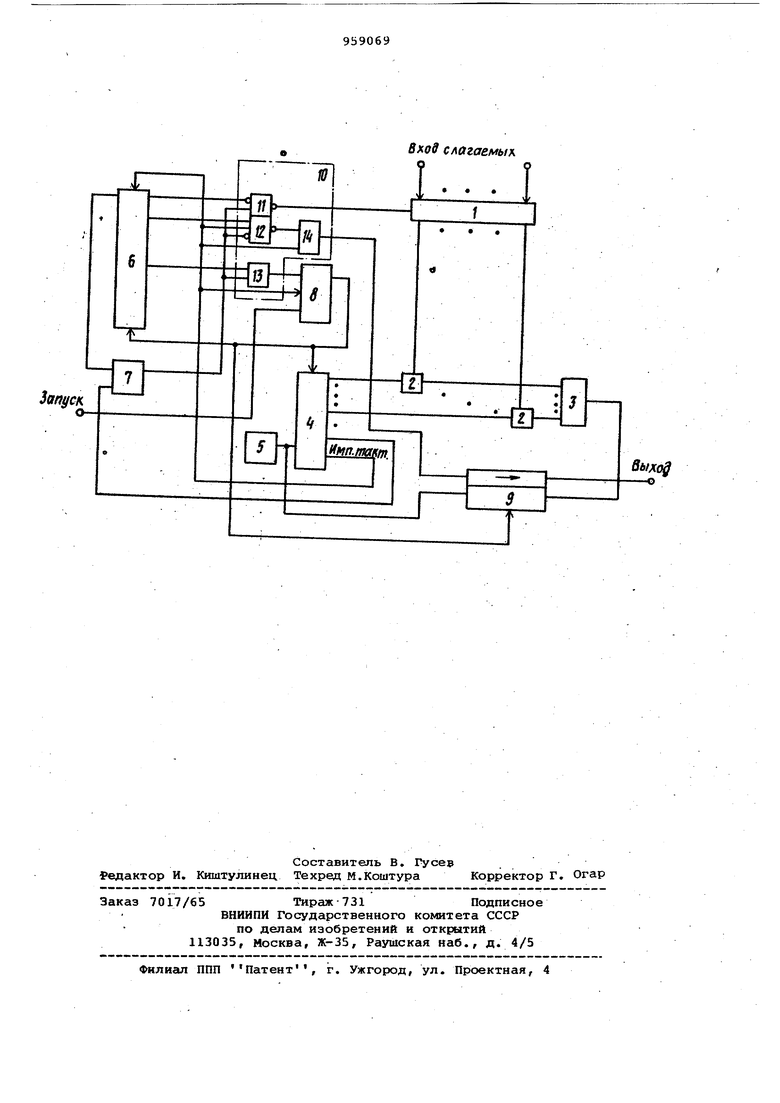

25 первый вход третьего элемента И блока управления соединен с выходом (2 ( ) разряда регистра цикла, .вторые входы первого,- второго, третьего элементов И объединены и соеди30 нены с прямь1М выходом триггера цикла. вход установки в ноль которогр соединен с выходом первого разряда регистра цикла, вход установки в единицу - с п + 2 выходом распределителя импульсов, выход тактовых импульсов которого соединен с управляющим входом регистра цикла, счетным входо триггера установки в ноль, третьим входом второго элемента И-и первым входом четвертого элемента И блока управления, выход первого элемента блока управления соединен с входом разрешения записи регистра anaraeivtix выход второго элемента И блока управления соединен с вторым входом четвертого элемента И блока управления, выход которого соединен со сдви говым входом счетчика, счетный вход которого соединен с выходом генератора тактовой частоты, управляющий вход - с выходом элементаИЛИ, а выход является выходом сумматора, выход третьего элемента И блока управления соединен с К-входом триггера установки в ноль, D-вход которого является входом Запуск сумматора а прямой выход соединен с входами установки в ноль регистра цикла, рас пределителя импульсов и счетчика. На чертеже изображена схема последовательного цифрового сумматора. Последовательный цифровой сумматор содержит регистр 1 слагаемых, п. элементов И 2, элемент ИЛИ 3, распр делитель 4 импульсов, генератор 5 тактовой частоты, регистр б цикла, триггер 7 цикла, триггер 8 установки в ноль, счетчик 9, блок 10 управ ления, содержащий первый, второй, третий, четвертый элементы И 1-1,12 13 и 14. Устройство работает следующим образом. Пусть необходи ю одновременно сло жить и вычесть несколько чисел с раз личными знаками. Положительные числ записаны в прямом коде, отрицательны в дополнительном. Вычитание числа пр псдачё инвертируют. Числа подают на параллельные входы регистра 1 слагаeivtjx (каждое число на свой разряд регистра) младшими разрядами вперед По сигналу Запуск снимается установка в ноль регистра цикла, распределителя импульсов и счетчика. В liepBOM цикле работы сумматора в ра ряда регистра 1 слагаемых,на которые будут подаваться вычитаеи«де числа, записываются единицы и с распределителя .4 импульсов на вторале входы « элементов И 2 поступает серия из импульсов.С выхода элемента ИЛИ 3 н управляющий вход счетчика 9 импульсов поступает и записывается число, равное количеству вычитае «х чисел. Сигнал, поступающий с выхода элемента И 14 блока 10 управления запрещае сдвиг информации в счетчике 9 и в следующем цикле в разряды регистра 1 слагаемых подаются младшие разряды всех чисел, участвующих в процессе сложения-вычитания, а затем на вторые входы элементов И 2 с выходов распределителя 4 импульсов вновь подается серия изп импульсов. Состояние счетчика 9 суммируется с количеством единиц в младщих разрядах чисел, Ь частвующих в операции сложения-вычитания. В следующих циклах работы устройства производится сдвиг информации, записанной в счетчике 9, на один разряд в сторону младших разрядов и запись в разряды регистра 1 слагаемых последующих разрядов чисел с подачей на вторые входы п элементов И 2 серий из п импульсов с выходов распределителя 4 импульсов и запись полученной информации в счетчик 9. С каждым сдвигом счетчика 9 выводится соответствующий разряд результата сложения-вычитания. Положительный результат получается в прямом коде, отрицательный - в дополнительном. После введения в разряды регистра 1 слагаемых знаковых разрядов чисел, в начале (п+1)-го цикла распределителя 4 импульсов (так как в первом цикле вводятся единицы поправки мпадшего разряда) на выходе элемента И 1Г блока 10 управления формируется сигнал запрета записи в регистр 1 слагае «ых, который сохраняется до конца операции. Триггер 7 цикла устанавливается в единицу по (п+2)-му импульсу распределителя 4. импульсов в конце п цикла, поэтому для введения знаковых разрядов чисел в регистр 1 слагае ых, на выходе элемента И 11 блока 10 управления нужно иметь разрешение еще на один такт сдвига, для чего на первый вход элемента И 11 блока 10.управления подается значение первого разряда регистра б цикла, которое задерживает действие триггера 7 цикла на время, достаточное для ввода знаковых разрядов чисел в регистр 1 слагаемых. Окончание операции сложения-вычитания п чисел происходит после прохождения (1+п+} о(5дп) циклов распределителя 4 импульсов-, (п+1)-й цикл полностью проходит при наличии единицы во втором разряде регистра 6 цикла и при значении триггера 7 цикла, равном единице, значит для получения результату необходимо после введения знаковых разрядов чисел провести еще (I ofijinC ) циклов распределителя -4 импульсов. Для этого на первый вход И 13 блока 10 управления подается значение- ( )-го разряда регистра 6,и в конце этого цикла по тактовому импульсу распределителя 4 импульсов происходит установ сумматора в ноль. Таким образом, данный сумматор может проводить операцию сложениявычитания над числами с любым натуральным основанием, числа могут быт целыми, правильными или смешанными дробями. Приведенный режим сложения вычитания можно использовать не тол ко при последовательной, но и при параллельной подаче чисел. Количеств или разрядность чисел, участвующих в операции, неограничено. Формула изобретения Последовательный цифровой суюлатор, содержащий регистр слагаемых,п элементов И, элемент ИЛИ, генератор тактовой частоты и распределитель импульсов, причем гт выходов регистра слагаеьФах соединен соответственно с первыми входами п элементов И, вторые входы которых соединены соответственно с п. выходами распределителя импульсов, вход которого соединен с выходом генератора тактовой частоты, п выходов элементов И соедит ны соответственно с п входами эледМента ИЛИ, отличающийся Тем, что, с целью расширения класса решаемых задач за счет получения возможности вычитания и чисел, подаваемых последовательнымикодами млад шими разрядами вперед, в него введены счетчик, регистр цикла, триггер цикла, триггер установки в ноль и блок управления, содержащий первый, второй, третий и четвертый элементы И, первый вход первого элемента И ,.. блока управления соединен с выходом первого разряда регистра цикла, nepi вый вхЬд второго элемента .И блок. управления соединен с выходом третьего разряда регистра цикла, первый вход третьего элемента И блока управления соединен с выходом (2+ ,2.чС ) разряда регистра цикла, вторые входы первого, второго, третьего элементов 1л объединены и соединены с прямлм выходом триггера цикла, вход установки в ноль которого соединен с выходом первого разряда регистра цикла, авход установки в единицу - с п +2 выходом распределителя импульсов, илход тактовых импульсов которого соединен с управляющим входом регистра цикла, счетным входом триггера установки в ноль, третьим входом второго элемента И и первым входом четвертого элемента И блока управления, выход первого элемента блока управления соединен с входом разрешения зсшиси регистра -слагаемых., выход второго элементами блока управления соединен с вторым входом четвертого элемента И блока управления, выход которого соединен со сдвиговым входом счетчика, счетный вход которого соединен с выходом генератора тактовой частоты, управляющий вход - с выходом элемента ИЛИ, а выход является выходом сумматора, выход третьего элемента И блока управления соединен с К -входом триггера установки в ноль,J -вход которого является входом Запуск суммато- тора, а прямой выход соединен с входами установки в ноль регистра цикла, распределителя импульсов и счетчика, . . . . . Источники информации, во внимание при экспертизе 1.Авторское свидетельство СССР 693371, кл. G Об F 7/50, 1976. 2.Малиновский Б.Н. Введение в кибернетическую технику. Киев, Наукова думка , 1979, с. 122, рис. 34 (прототип). Запаек о BxoS слагаемы)(.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Отсчетное устройство | 1976 |

|

SU661548A1 |

| Медианный рекурсивный фильтр | 1988 |

|

SU1654837A1 |

| Устройство для определения среднего арифметического значения | 1986 |

|

SU1310840A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Устройство для деления нормализованных чисел | 1985 |

|

SU1290302A1 |

| Арифметико-логическое устройство для сложения и вычитания чисел по модулю | 2017 |

|

RU2639645C1 |

| СПЕЦИАЛИЗИРОВАННОЕ ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU408304A1 |

Авторы

Даты

1982-09-15—Публикация

1980-12-12—Подача