блока счетчика-адреса, первый вход блока сравнения соединен с выходом блока приема ответных сигналов и с информационным входом блока кодирования, а второй вход - с выходом адреса первого блока постоянной памяти, выход условного адреса которого соединен с адресным входом блока кодирования.

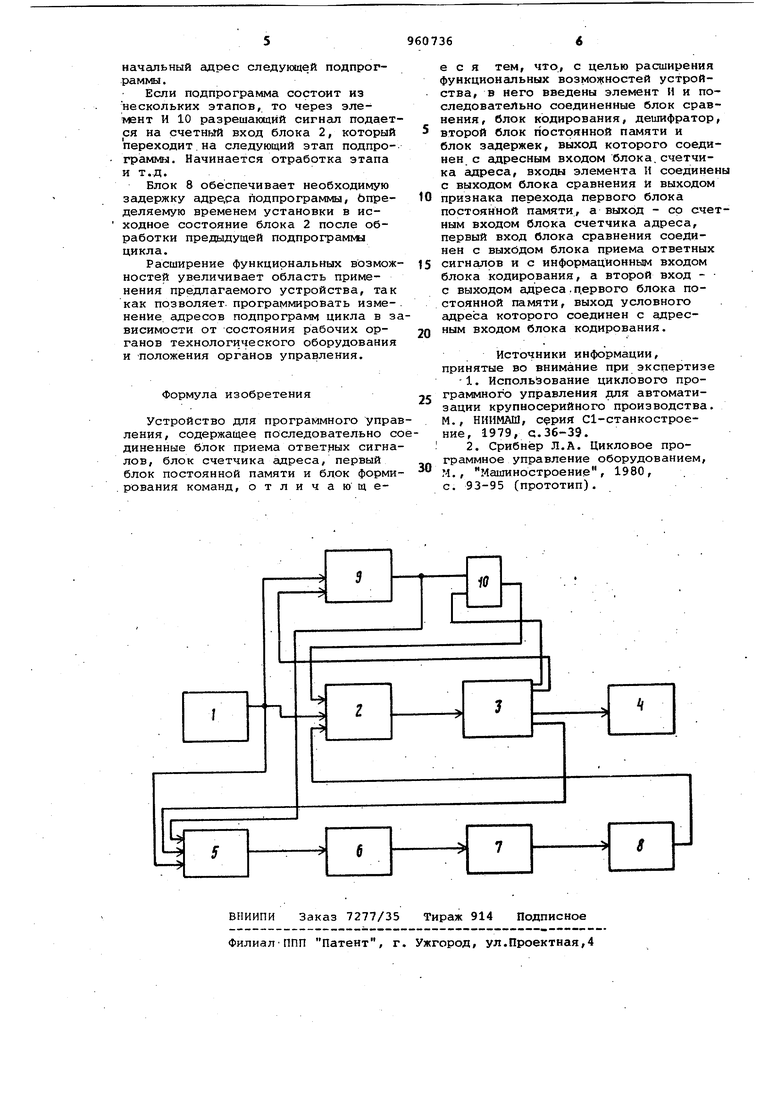

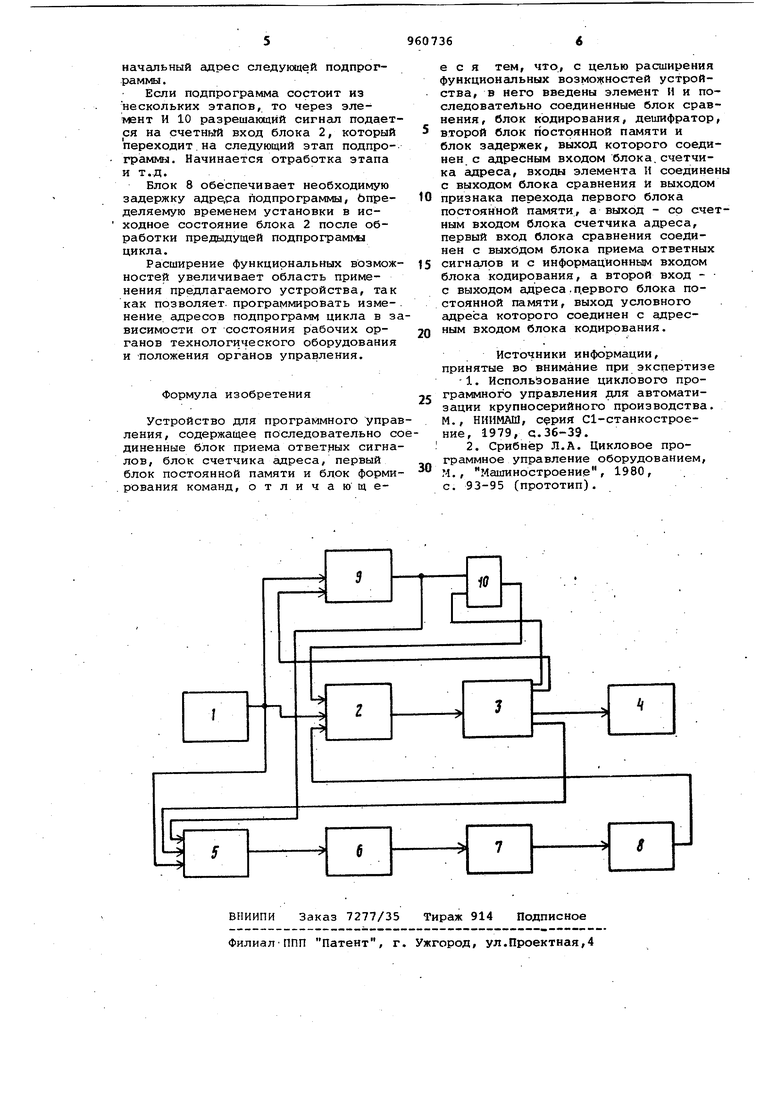

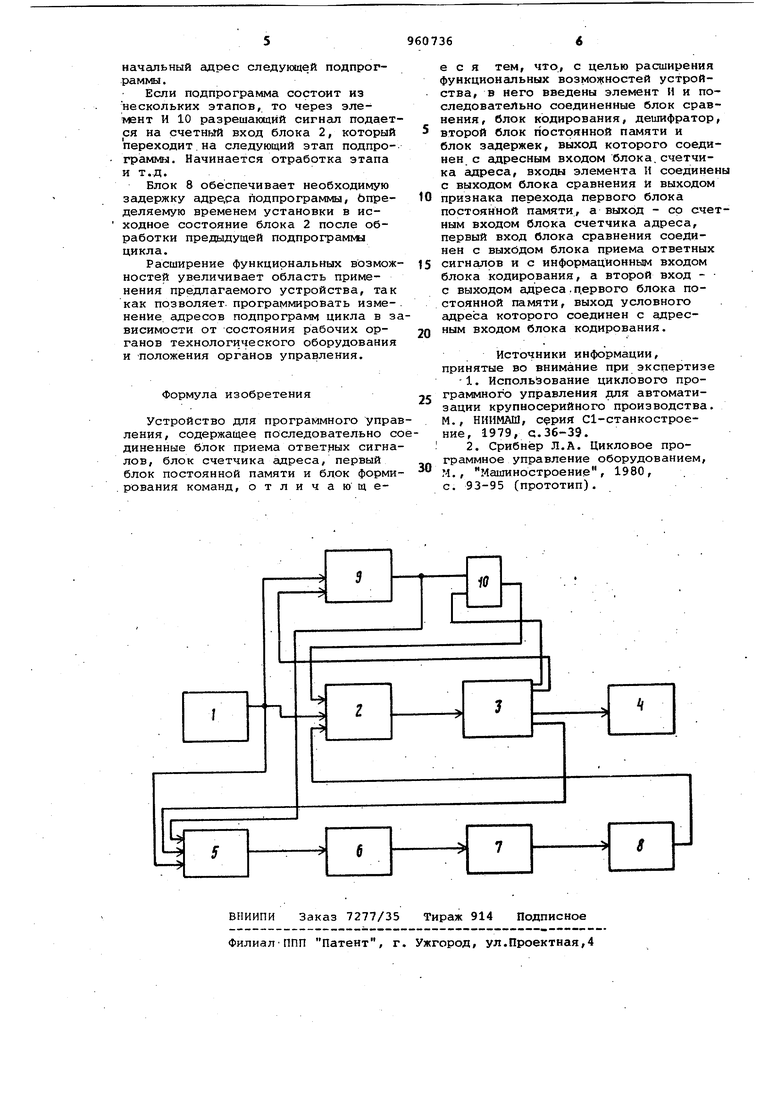

На чертеже дана схема устройства для программного управления.

Устройство содержит блок 1 приема ответных сигналов, блок 2 счетчика адреса, первый блок 3 постоянной памяти, блок 4 формирования команд, блок 5 кодирования, дешифратор 6, второй блок 7 постоянной памяти, блок 8 задержек, блок 9 сранения и элемент И 10.

.Поле слова блока 3 разбито дополнительно на зону программирования кода адреса условного перехода к подпрограммам цикла (выход условного адреса блока), зону программирования признака перехода по коду (выход признака перехода блока 3) и зону кода входного адреса (выход адреса блока 3).

. Устройство работает следующим образом.

Информационные сигналы, определящие состояние объекта и положение органов управления, поступает с выходов блока 1 приема ответных сигналов на соответствующие входы блока сравнения, блока 5 кодирования и блока 2 счетчика адреса, вы.ходные сигналы которого определяют адрес ячейки блока 3 (номер отрабатываемого этапа), где программируются в соответствующих зонах, согласно алгоритма работы объекта, команды включения исполнительных механизмовпризнака перехода по коду, а также код адреса условного перехода к подпрограммам цикла и код входного адреса.

Код входного адреса определяет вход, на котором при наличии разрешающего сигнала необходимо закончить обработку этапа и перейти к .следующим этапам программ согласно алгоритма работы.

Блок 9 сравнивает выходные сигналы блоков 1 и 3 и при совпадении указанных сигналов на его выходе появляется разрешающий сигнал, поступающий на вход элемента И 10 и управляющий вход блока 5.

Код адреса условного перехода к подпрограммам цикла определяет совокупность начальных адресов подпрограмм цикла, переход к которым возможен после отработки текущего этапа.

Дальнейший выбор конкретной подпрограммы реализуется следующим образом.

Блок 5 формирует код адреса подпрограммы в зависимости от выходных сигналов блока 1, блока 3, которьтй появляется на выходе блока 5 при наличии разрешающего сигнала на его управляющем входе.

Признак условного перехода программируется с целью обеспечения радельного управления блоком 2 по счетному и адресному входам.

При наличии признака условного прехода на входе элемента И 10 появляется запрещаюо1ий сигнал и при появлении разрешающего сигнала с выхода блока 9 происходит формирова ние адреса подпрограммы, а управление блоком 2 осуществляется по адресным входам,

Если же признак условного перехода не запрограммирован на данном этапе, то управление блоком 2 осуществляется по счетному входу управления сигналом, поступающим с выхода элемента И 10. В этом случае блок 2 переходит на следующий этап.

При поступлении сигнала с выхода блока 1 на пусковой вход блока 2 последний переходит на первый этап. При этом из первой ячейки блока 3 считывается запрогра1умированная в соответствии с алгоритмом работы информация. Код входного адреса на выходе блока 3 определяет исходтное состояние входов и при наличии сигналов, подтверждающих исходное состояние объекта, на выходе блока появляется разрешающий сигнал.

Если запрограммирован признак перехода по коду, то на входе элемента И 10 появляется сигнал, запрещакйций переход блока 2 на следующий второй этап, а блок 5.зависимости от положения органов управления и состояния управляемого объекта формирует код адреса подпрограммы.

Далее код адреса подпрограммы дешифрируется дешифратором 6, сигнал которого возбуждает ячейку памяти второго блока 7, где записан адрес первой подпрограммы цикла. Этот адрес через блок 8 поступает на адресные входы блока 2 и устанавливает на его выхода1Х начальный адрес первой подпрограммы, чт.о приводит к включению соответствующей ячейки памяти блока 3. Начинается отрабатывание запрограммированных команд. Выполнение этих команд буде продолжаться до тех пор, пока не появится сигнал, подтверждающий их окончание на входе устройства. Это, в свою очередь, вызовет появление на выходе блока 9 разрешающего сигнала, определяющего переход к вьшолнению следующих .этапов.

При-напичии признака условного перехода к выполнению следующей, подпрограммы в блоке 5 формируется

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1988 |

|

SU1511750A1 |

| Устройство для программного управления | 1990 |

|

SU1716482A1 |

| Устройство для программированияблОКОВ пОСТОяННОй пАМяТи | 1979 |

|

SU794667A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1367013A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Программируемый логический контроллер | 1988 |

|

SU1647518A1 |

| Устройство для сбора телеметрителеметрической информации | 1975 |

|

SU527727A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

Авторы

Даты

1982-09-23—Публикация

1981-01-28—Подача