1

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении быстродействующих двоично-десятичных преобразователей в вычислительных машинах, цифровых автоматических системах управления и контроля.

Цель изобретения - повышение быстродействия и упрощение преобразователя.

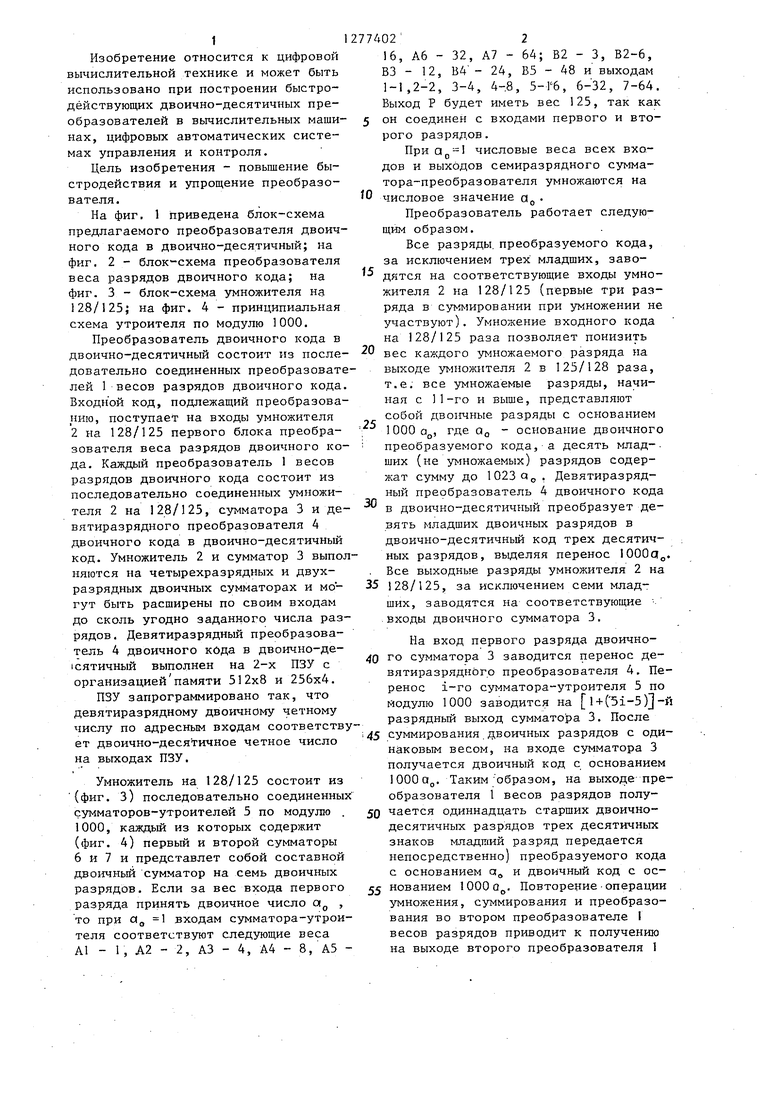

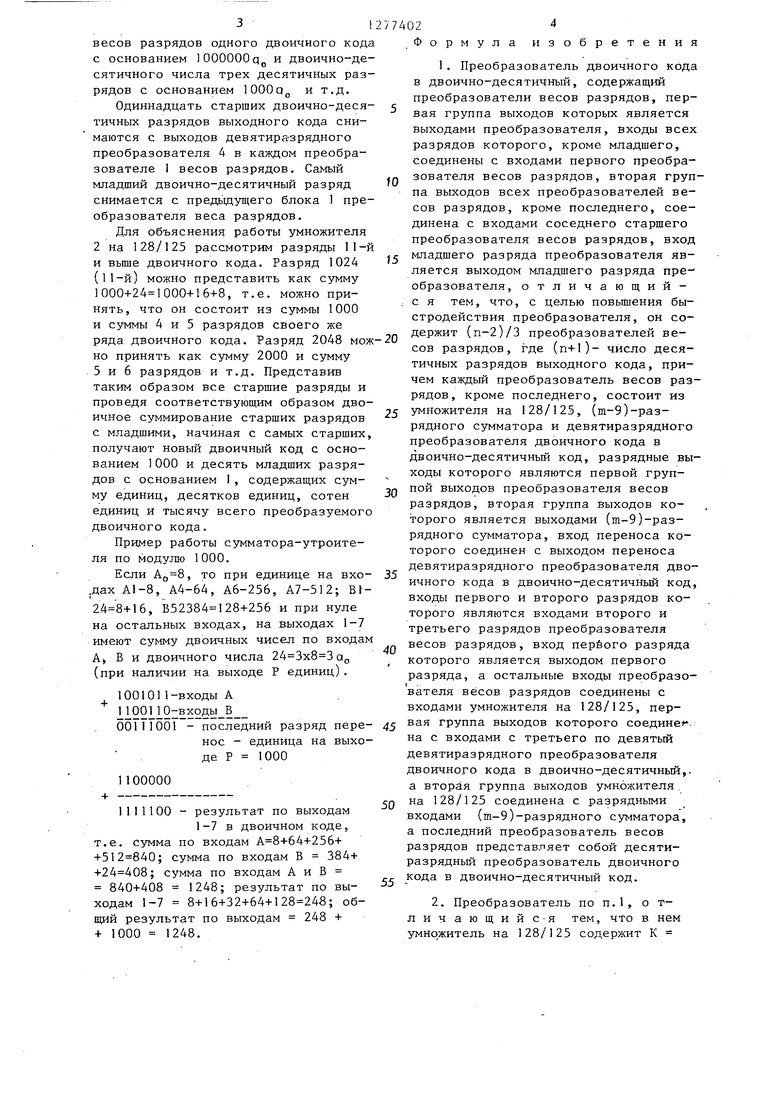

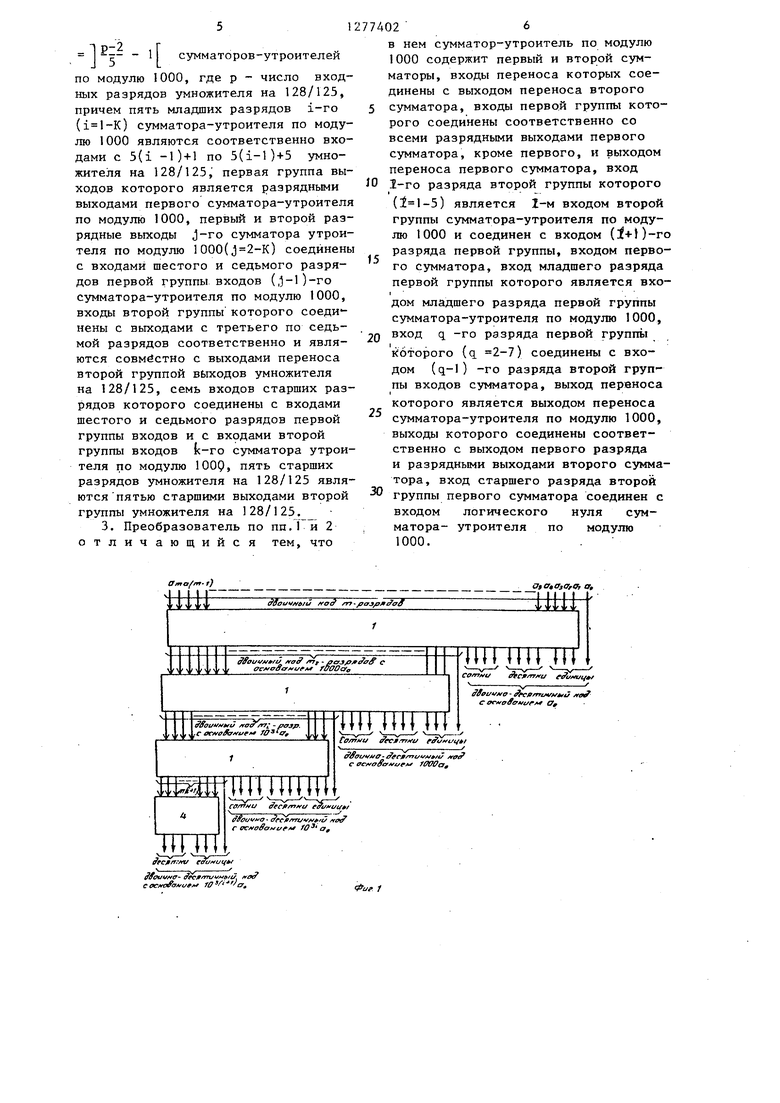

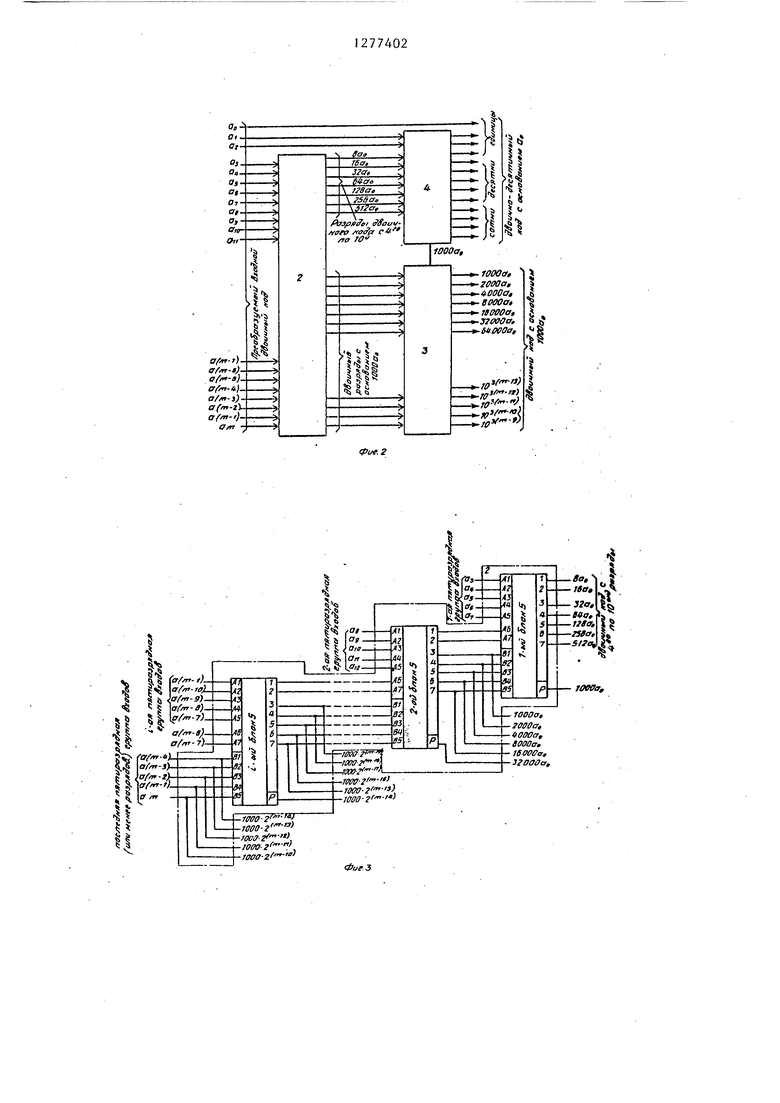

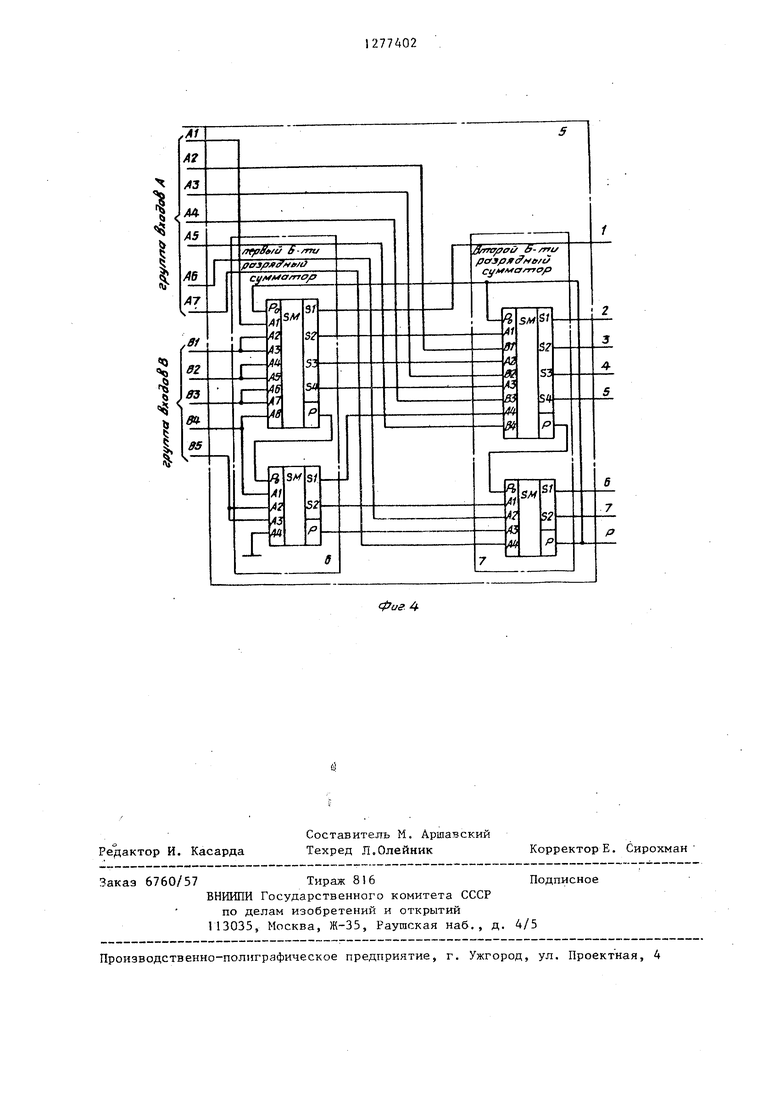

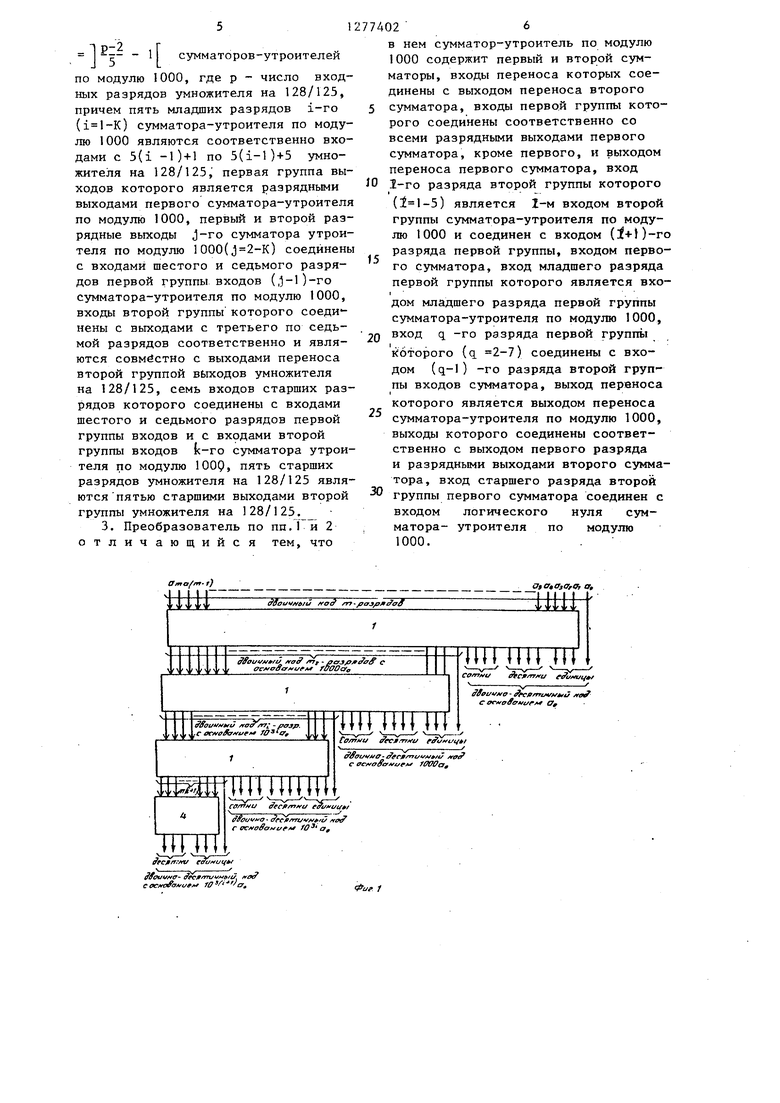

На фиг. 1 приведена блок-схема предлагаемого преобразователя двоичного кода в двоично-десятичный; на фиг. 2 - блок-схема преобразователя веса разрядов двоичного кода; на фиг. 3 - блок-схема умножителя на 128/125; на фиг. 4 - принципиальная схема утроителя по модулю 1000.

Преобразователь двоичного кода в двоично-десятичный состоит из последовательно соединенных преобразователей 1 весов разрядов двоичного кода Входной код, подлежащий преобразованию, поступает на входы умножителя 2 на 128/125 первого блока преобразователя веса разрядов двоичного кода. Каждый преобразователь 1 весов разрядов двоичного кода состоит из последовательно соединенных умножителя 2 на 128/125, сумматора 3 и девятиразрядного преобразователя 4 двоичного кода в двоично-десятичный код. Умножитель 2 и сумматор 3 выполняются на четырехразрядных и двухразрядных двоичных сумматорах и могут быть расширены по своим входам до сколь угодно заданного числа разрядов . Девятиразрядный преобразователь 4 двоичного кода в двоично-де- 1СЯТИЧНЫЙ выполнен на 2-х ПЗУ с организацией памяти 512x8 и 256x4.

ПЗУ запрограммировано так, что девятиразрядному двоичному четному числу по адресным входам соответству ет двоично-десятичное четное число на выходах ПЗУ.

Умножитель на 128/125 состоит из {фиг. З) последовательно соединенных сумматоров-утроителей 5 по модулю 1000, каждый из которых содержит (фиг. 4) первый и второй сумматоры 6 и 7 и представлет собой составной двоичный сумматор на семь двоичных разрядов. Если за вес входа первого разряда принять двоичное число а , то при Од 1 входам сумматора-утрои- теля соответствуют следующие веса А1 - Г, А2 - 2, A3 - 4, А4 - 8, А5 25

77402 2

16, А6 - 32, А7 - 64; В2 - 3, В2-6, ВЗ - 12, В4 - 24, В5 - 48 и выходам 1-1,2-2, 3-4, 4-8, 5-1-6, 6-32, 7-64. Выход Р будет иметь вес 125, так как

5 он соединен с входами первого и второго разрядов.

ПриОр числовые веса всех входов и выходов семиразрядного сумматора-преобразователя умножаются на

0 числовое значение а.

Преобразователь работает следующим образом.

Все разряды, преобразуемого кода, за исключением трех младших, заво дятся на соответствующие входы умножителя 2 на 128/125 (первые три разряда в суммировании при умножении не участвуют). Умножение входного кода на 128/125 раза позволяет понизить

2 вес каждого умножаемого разряда на выходе умножителя 2 в 125/128 раза, т.е. все умножаемые разряды, начиная с П-го и выше, представляют собой двоичные разряды с основанием lOOOOj,, где QO - основание двоичного

преобразуемого кода, а десять млад-, ших (не умножаемых) разрядов содержат сумму до 1023 о о . Девятиразрядный преобразователь 4 двоичного кода

в двоично-десятичный преобразует девять младших двоичных разрядов в двоично-десятичный код трех десятичных разрядов, выделяя перенос ЮООа,,. Все выходные разряды умножителя 2 на

35 128/125, за исключением семи младших, заводятся на соответствующие -. Входы двоичного сумматора 3,

На вход первого разряда двоично40 го сумматора 3 заводится перенос де- вятиразрядногр преобразователя 4. Перенос i-ro сумматора-утроителя 5 по модулю 1000 заводится на 1+( 51-5)-й разрядный выход сумматора 3. После

45 суммирования двоичных разрядов с одинаковым весом, на входе сумматора 3 получается двоичный код с основанием ЮОООд. Таким образом, на выходе преобразователя 1 весов разрядов полу50 чается одиннадцать старших двоично- десятичных разрядов трех десятичных знаков младгаий разряд передается непосредственно) преобразуемого кода с основанием а и двоичный код с ос55 нованием ЮООо, Повторение операции умножения, суммирования и преобразования во втором преобразователе I весов разрядов приводит к получению на выходе второго преобразователя 1

3

весов разрядов одного двоичного кода с основанием 1 000000q и двоично-десятичного числа трех десятичных разрядов с основанием lOOOa и т.д.

Одиннадцать старших двоично-десятичных разрядов выходного кода снимаются с выходов девятира-зрядного преобразователя 4 в каждом преобразователе 1 весов разрядов. Самый младший двоично-десятичный разряд снимается с предьщущего блока 1 преобразователя веса разрядов.

Для объяснения работы умножителя 2 на 128/125 рассмотрим разряды II-и и выше двоичного кода. Разряд 1024 (и-и) можно представить как сумму 1000+24 1000+16+8, т.е. можно принять, что он состоит из суммы 1000 и суммы 4 и 5 разрядов своего же ряда двоичного кода. Разряд 2048 мож но принять как сумму 2000 и сумму 5 и 6 разрядов и т.д. Представив таким образом все старшие разряды и проведя соответствующим образом двоичное суммирование старших разрядов с младшими, начиная с самых старших, получают новый двоичный код с основанием 1000 и десять младших разрядов с основанием I, содержащих сумму единиц, десятков единиц, сотен единиц и тысячу всего преобразуемого двоичного кода.

Пример работы сумматора-утроите- ля по модулю 1000.

Если А,8, то при единице на вхо- .дах А1-8, А4-64, Аб-256, А7-512; Bt- 2., В52384 128+256 и при нуле на остальных входах, на выходах 1-7 имеют сумму двоичных чисел по входам А В и двоичного числа (при наличии на выходе Р единиц).

1001011-входы А

ii2 i 2lS525bi B

OOTTlOOl - последний разряд перенос - единица на выходе Р 1000

1100000

1111100 - результат по выходам 1-7 в двоичном коде, т.е. сумма по входам А 8+64+256+ сумма по входам В 384+ сумма по входам А и В 840+408 1248; результат по выходам 1-7 8+16+32+64+128 248; общий результат по выходам 248 + + 1000 1248.

774024

Формула изобретения

1. Преобразователь двоичного кода в двоично-десятичный, содержащий преобразователи весов разрядов, пер вая группа выходов которых является выходами преобразователя, входы всех разрядов которого, кроме младшего, соединены с входами первого преобраIQ зователя весов разрядов, вторая группа выходов всех преобразователей весов разрядов, кроме последнего, соединена с входами соседнего старшего преобразователя весов разрядов, вход

j младшего разряда преобразователя является выходом младшего разряда преобразователя, отличающий- . с я тем, что, с целью повьш1ения быстродействия преобразователя, он со,„ держит (п-2)/3 преобразователей

сов разрядов, где (п+1J- число десятичных разрядов выходного кода, причем каждый преобразователь весов разрядов, кроме последнего, состоит из

25 умножителя на 128/125, (ni-9)-разрядного сумматора и девятиразрядного преобразователя двоичного кода в двоично-десятичный код, разрядные выходы которого являются первой груп Q пой выходов преобразователя весов разрядов, вторая группа выходов которого является выходами (т-9)-разрядного сумматора, вход переноса которого соединен с выходом переноса девятиразрядного преобразователя двоичного кода в двоично-десятичный код, входы первого и второго разрядов которого являются входами второго и третьего разрядов преобразователя

JQ весов разрядов, вход перёого разряда , которого является выходом первого

разряда, а остальные входы преобразователя весов разрядов соединены с входами умножителя на 128/125, пер вая группа выходов которого соединен, на с входами с третьего по девятый девятиразрядного преобразователя двоичного кода в двоично-десятичньш,. а вторая группа выходов умножителя

Q на 128/125 соединена с разрядными входами (т-9)-разрядного сумматора, а последний преобразователь весов разрядов представляет собой десятиразрядный преобразователь двоичного

ее кода в двоично-десятичный код.

2. Преобразователь по п.1, о т- лич ающий с-я тем, что в нем умножитель на 128/125 содержит К

35

- 1 сумматоров-утроителей

по модулю 1000, где р - число входных разрядов умножителя на 128/125, причем пять младших разрядов i-ro () сумматора-утроителя по модулю 1000 являются соответственно входами с 5(1 -1) + 1 по 5(1-1 ) умножителя на 128/125, первая группа выходов которого является разрядными выходами первого сумматора-утроителя по модулю 1000, первый и второй разрядные выходы J-ro сумматора утрои- теля по модулю 1000() соединены с входами шестого и седьмого разрядов первой группы входов (,j-l)-ro сумматора-утроителя по модулю 1000, входы второй группы которого соединены с выходами с третьего по седьмой разрядов соответственно и являются совместно с выходами переноса второй группой выходов умножителя на 128/125, семь входов старших разрядов которого соединены с входами шестого и седьмого разрядов первой группы входов и с входами второй группы входов fc-ro сумматора утрои- теля по модулю 1009, пять старших разрядов умножителя на 128/125 являются пятью старшими выходами второй группы умножителя на 128/125.

3. Преобразователь по пп,1 и 2 отличающийся тем, что

Omaf -t ),а,а,а, а.

Шй

о /тт

5

в нем сумматор-утроитель по модулю 1000 содержит первый и второй сумматоры, входы переноса которых соединены с выходом переноса второго сумматора, входы первой группы которого соединены соответственно со всеми разрядными выходами первого сумматора, кроме первого, и выходом переноса первого сумматора, вход 1-го разряда второй группы которого () является 1-м входом второй группы сумматора-утроителя по модулю 1000 и соединен с входом (i+))-ro разряда первой группы, входом первого сумматора, вход младшего разряда

первой группы которого является вхоI

дом младшего разряда первой группы

сумматора-утроителя по модулю 1000, Q вход q -го разряда первой группь которого (q 2-7) соединены с входом (q-l) -го разряда второй группы входов сумматора, выход переноса которого является выходом переноса сумматора-утроителя по модулю 1000, выходы которого соединены соответственно с выходом первого разряда и разрядными выходами второго сумматора, вход старшего разряда второй группы первого сумматора соединен с входом логического нуля сумматора- утроителя по модулю 1000.

0

Sfe-t/VAc / a /Пг - с ffc ero- -«

tfLf /foef /Пг - acfjjOA pffo tffAf f&OOcfe

lunuTTu

™,f

Cff/rr tf ffecjtfrrfftj fffi/fft/t t/

i75#l7i/V Vff- r /TT4/W /i/ w с ffC/ 00iy fi/fM

lUIIUIlU

,--/ -X

ГДТЛУй/ fffCJf/Tf t/ ffft/Mt/iftt

V /

ffffffUVffO - fTfCJP/rn/ V /U ffff г O ffoSof t fAf fO Cff

ЩГТПТЖ.

Cff t/ Cf/TTffU A vW/v/

//ffLfvjver - ff/rrtMf ftf /eer с ffc-M(yffff ft/ff CV

Gt/VHtf frOff

ФLff. 1

i:§

rOOOa, ZaffOa, «ООРа, SOOOtr ISOOCa,

згоооа.

Редактор И. Касарда

Составитель М. Аршавский Техред Л.Олейник

Заказ 6760/57Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раугаская наб., д. 4/5

.....«..«...-..««,«.« -.™-.- - ™,-,..„ - .„ - -. - - ---...-,.-.--- - - - -. - -.-.- - ,.

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фиг. 4

Корректор Е. Сирохман

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771659A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1205137A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU960794A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1983 |

|

SU1095169A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691844A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU888104A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1979 |

|

SU877521A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU881730A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении быстродействующих двоично-десятичных преобразователей в вычислительных машинах, цифровых автоматических системах управления и контроля. Цель изобретения - повышение быстродействия преобразователя. Поставленная цель достигается тем, что преобразователь двоичного кода в двоично-десятичный содержит (п-2)/3 преобразователей весов разрядов двоичного кода, где (п+1) - число десятичных разрядов выходного кода, причем каждый преобразователь, кроме последнего, состоит из умножителя на 128/125, (т-9)-разрядного сумматора и девятиразрядного преобразователя двоичного кода в двоично-десятичньй код, а также тем, что умножитель содержит К J(p-2)/5-lL сумматоров-утроителей по модулю 1000, каждый из которых содержит первый и второй сумматоры с соответствующими связями. 2 з.п. ф-лы, 4 ил. i (Л е

| Авторское свидетельство СССР № , кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Огарков B.C., Тихонов Ю.Г | |||

| Прямое преобразование двоичного кода в двоично-десятичный и двоично-десятичного кода в двоичный | |||

| Приборы и техника эксперимента, 1983, № 4, с | |||

| Прялка для изготовления крученой нити | 1920 |

|

SU112A1 |

Авторы

Даты

1986-12-15—Публикация

1984-01-26—Подача