(54),ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1980 |

|

SU911522A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU922760A2 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU920716A2 |

| Арифметическое устройство | 1977 |

|

SU728127A2 |

| Цифровой гармонический анализатор | 1979 |

|

SU873148A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU678488A1 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

| Функциональный преобразователь | 1977 |

|

SU693379A2 |

Изобретение относится к цифровой вычислительной технике и может найти применение для аппаратной реализации вычисления функций.

По основному авт.св. №591861 известен функциональный преобразователь 1, содержащий три сумматоравычитателя, два регистра, блок анализа и б-лок управления. Выход первого сумматора-вычитателя соединен с входом блока анализа, первый выход которого подключен к входу блока управления, а второй выход соединен с первыми входами сумматоров-вычитателей. Первый выход блока управле.ния соединен с вторьлми входами сум-, маторов-вычитателей, а второй выход - с первыми входами регистров. Выход первого регистра соединен с третьим входов первого сумматоравычитателя, выход второго регистра - с третьими входами второго итретьего сумматоров-вычитателей. Второй вход первого регистра и четвертые входы второго и третьего сумматоров-вычитателей соединены с первыми входами функционального преобразователя. Второй вход второго регистра и четвертый вход первого сумматора-вычитателя соединены с

вторым входом функционального преобразователя. Функциональный преобразователь предназначен для одновременного вычисления двух функций

I (х - /).|t

у )

Недостатком преобразователя являются его ограниченные функциональные

10 возможности, так как он предназначен для вычисления только двух функций.

Цель изобретения - расширение класса решаемых задач за счет возможности дополнительного вычисления

15 функций

л 1 -ZУ - X ,

Поставленная цель достигается

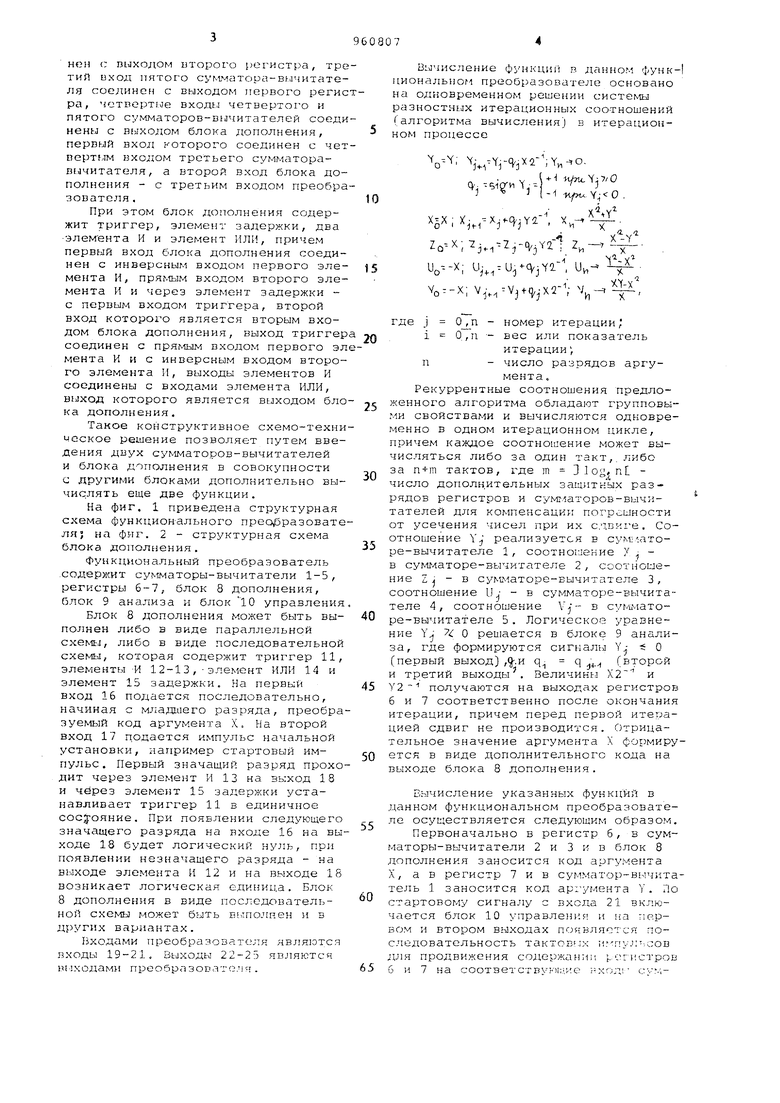

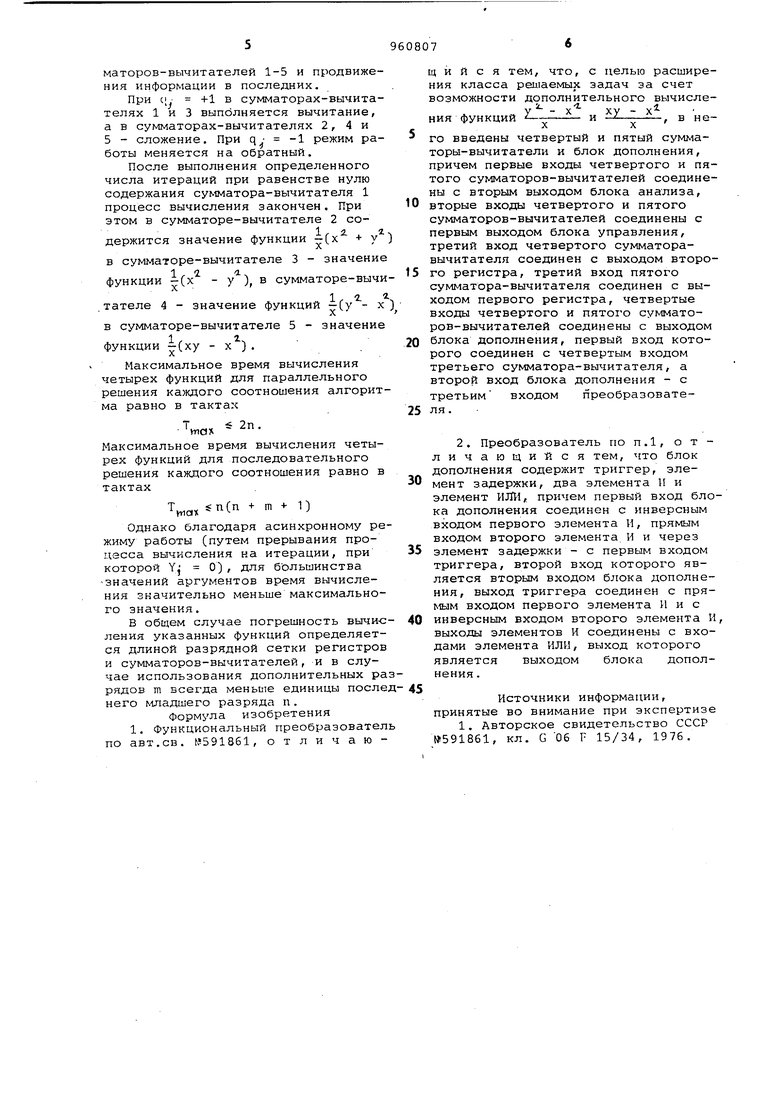

20 тем, что в функциональный преобразователь дополнительно введены четвертый и пятый cy 1мaтopы-вычитaтeли и блок дополнения, причем первые входы четвертого и пятого сумматоров25вычитателей соединены с вторым выходом блока анализа, вторые входы четвертого и пятого сумматоров-вычитателей соединены с первым выходом блока управления, третий вход чет30вертого сумматора-вычитателя соединен с выходом второго регистра, тр тий вход пятого сумматора-вичитате лд соединен с выходом первого реги ра, четвертые входы четвертого и пятого сумматоров-вычитателей соед нены с В 21ходом блока дополнения, первый вход которого соединен с че пертым 13ХОДОМ третьего сумматоравычитателя, а второй вход блока до полнения - с третьим входом преобр зователя , При этом блок дополнения содержит триггер, элемент задержки, два -элемента И и элемент ИЛИ, причем первый вход блока дополнения соединен с инверсным входом первого эле мента Н, прямым входом второго эле мента И и через элемент задержки с первым входом триггера, второй вход которого является вторым входом блока дополнения, выход тригге соединен с прямым входом первого э мента И и с инверсным входом второ го элемента И, выходы элементов И соединены с входами элемента ИЛИ, выход которого является выходом бло ка дополнения. Такое конструктивное схемо-техни ческое решение позволяет путем введения двух сумматоров-вычитателей и блока дополнения в совокупности с другими блоками дополнительно вы чирлять еще две функции. На фиг. 1 приведена структурная схема функционального прео Зразовате ля; на фиг. 2 - структурная схема блока дополнения. Функциональный преобразователь .содержит сук маторы-вычитатели 1-5 , регистры 6-7, блок 8 дополнения, блок 9 анализа и блок 10 управления Блок 8 дополнения может быть выполнен либо в виде параллельной cxeNttJ, либо в виде последовательной схемы, которая содержит триггер 11 элементы И 12-13,-элемент ИЛИ 14 и элемент 15 задержки. На первый вход 16 подается последовательно, начиная с младьиего разряда, преобра зуемый код аргумента X. На второй вход 17 подается импульс начальной установки, например стартовый импульс. Первый значащий разряд прохо дит через элемент И 13 на выход 18 и через элемент 15 задержки устанавливает триггер 11 в единичное состояние. При появлении следующего значащего разряда на входе 16 на вы ходе 18 будет логический нуль, при появлении незначащего разряда - на выходе элемента И 12 и на выходе 18 возникает логическая единица. Блок 8 дополнения в виде последовательной схемы может быть выполнен и в ддругих вариантах. Входами преобразователя являются входы 19-21. Вьаходы 22-25 являются выходами преобразовлтсг..я . Вычисление функциГ в данном функциональном преобразователе основано на одновременном решении системы разностных итерационных соотношений (алгоритма вычисления) в итерационном процессе VvY -qjXa-iY.-.o. q..,,WHXr-l j 3 МИ , , , , X, . Zo-X; j.,-2,-(V3V2l U,4,U-cVjYi-, Uv, Vo-x; . -0,n - номер итерации; О,,п - вес или показатель итерации , - число разрядов аргумента . Рекуррентные соотношения предложенного алгоритма обладают групповыми свойствами и вычисляются одновременно в одном итерационном цикле, причем каждое соотношение может вычисляться либо за один такт,.либо за n + m тактов, где m Dlog uL число дополнительных защитных разрядов регистров и сумтлаторов-вычитателей для компенсации погрешности от усечения чисел при их с.дпихе. Соотношение Y-, реализуется в сум латоре-вычитателе 1, соотногление У в сумгдаторе-вычитателе 2 , соотношение Z J - в сумматоре-вычитателе 3, соотношение U; - в сум-маторе-вычитателе 4, соотношение j в сумматоре-вычитателе 5. Логическое уравнение Y,j 7 О решается в блоке 9 анализа, где формируются сигналы Y.J -s О (первый выход) ,д-.и q q ,,. (второй и третий выходы. BeличинfcJ Х2 и получаются на выходах регистров б и 7 соответственно после окончания итерации, причем перед первой итерацией сдвиг не производится. Отрицательное значение аргумента X формируется в виде дополнительного кода на выходе блока 8 дополнения. Вычисление указанных функций в данном функциональном преобразователе осуществляется следующим образом. Первоначально в регистр б, в сумматоры-вычитатели 2 и 3 и в блок 8 дополнения заносится код аргумента X, а в регистр 7 и в сумматор-вычитатель 1 заносится код ар:умента Y. По стартовому сигналу с входа 21 включается блок 10 управления и .:а первом и втором выходах появляется последовательность тактовмх .1;-.сов для продвижения содержанш; регистров б и 7 на соответствукицие .);т|- cv/,маторов-вычитателей 1-5 и продвиже ния информации в последних. При с;- +1 в сумматорах-вычита телях 1 и 3 выполняется вычитание а в су1 Ф/ аторах-вычитателях 2, 4 и 5 - сложение. При q -1 режим р боты меняется на обратный. После выполнения определенного числа итераций при равенстве нулю содержания сумматора-вычитателя 1 процесс вычисления закончен. При этом в сумматоре-вычитателе 2 со 1 5 держится значение функции - (х в сумматоре-вычитателе 3 - значен 12. 1 функции -(х - у ), в сумматоре-вы 1 7, тателе 4 - значение функций -(у Лв сумматоре-вычитателе 5 - значени функции -(ху - X ). Максимальное время вычисления четырех функций для параллельного решения каждого соотношения алгори ма равно в тактах уяах - 2 Максимальное время вычисления четы рех функций для последовательного решения каждого соотношения равно тактах . ( + m 1) Однако благодаря асинхронному р жиму работы (путем прерывания продасса вычисления на итерации, при которой YJ 0), для большинства -значений аргументов время вычисления значительно меньше максимально го значения. В общем случае погрешность вычи ления указанных функций определяет ся длиной разрядной сетки регистро и сумматоров-вычитателей, и в случае использования дополнительных р рядов m всегда меньше единицы посл него младшего разряда а. Формула изобретения 1. Функциональный преобразовате по авт.св. №591861, отличаю щийся тем, что, с целью расширения класса решаемых задач за счет возможности дополнительного вычисления функций - и -, в неУ-XГО введены четвертый и пятый сумматоры-вычитатели и блок дополнения, причем первые входы четвертого и пятого сумматоров-вычитателей соединены с вторым выходом блока анализа, вторые входы четвертого и пятого сумматоров-вычитателей соединены с первым выходом блока управления, третий вход четвертого сумматоравычитателя соединен с выходом второго регистра, третий вход пятого сумматора-вычитателя соединен с выходом первого регистра, четвертые входы четвертого и пятого сумматоров-вычитателей соединены с выходом блока дополнения, первый вход которого соединен с четвертым входом третьего сумматора-вычитателя, а второй вход блока дополнения - с третьим входом преобразователя. 2. Преобразователь по п.1, о т личающийся тем, что блок дополнения содержит триггер, элемент задержки, два элемента И и элемент ИЛИ, причем первый вход блока дополнения соединен с инверсным входом первого элемента И, прямым входом второго элемента И и через элемент задержки - с первым входом триггера, второй вход которого является вторым входом блока дополнения, выход триггера соединен с прямым входом первого элемента И и с инверсным входом второго элемента И, выходы элементов И соединены с входами элемента ИЛИ, выход которого является выходом блока дополнения. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №591861, кл. G 06 F 15/34, 1976.

Авторы

Даты

1982-09-23—Публикация

1980-06-19—Подача