(5) ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 2017 |

|

RU2642381C1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU911522A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Цифровой функциональный преобразователь | 1976 |

|

SU748434A1 |

| Устройство для вычисления экспоненциальной функции | 1977 |

|

SU711578A2 |

| Устройство для вычисления кубического корня | 1973 |

|

SU516037A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Устройство для вычисления элементарных функций | 1975 |

|

SU553612A1 |

| Устройство для вычисления функции ( @ - @ )/ @ | 1982 |

|

SU1076912A1 |

,1 . , ,

Изобретение относится к цифровой вычислительной технике и может найти применение для аппаратной реализ ацИи вычисления функций.

По основному авт.св. № известен цифровой преобразователь, содержащий блок анализа, первый и второй сумматоры-вычитатели , первый и второй регистры и блок управления, причем выход первого регистра соединен с первым входом первого сумматора-вычитателр, выходы блока управления соединены с управляющими входами первого и второ го регистров и тактовыми входами первого и второго сумматоров-вычитателей, выходы которых соединены с входами блока анализа, первый выход которого подключён ко входу блока управления, а второй выход соединен с управляющими входами первого и второго сумМаторов-вычитателей.выход второго регистра соединен с первым входом второго сумматора-вычитателя,вторые входы первого и второго сумматоров-вычитателей соединены с информационными входами соответственно второго и первого и являются входами преобразователя.

Преобразователь предназначен для вычисления функции частного суммы квадратов на сумму двух аргумен- тов t1 .

Недостатком известного преобразова10теля является то, что он не предназначен для вычисления других функций.

Цель изобретения - расширениефункциональных возможностей за счет дополнительного вычисления, кроме частISного суммы квадратов на сумму двух аргументов,также частного разности аргументов на их сумму.

Поставленная цель достигается тем, что в преобразователь введены

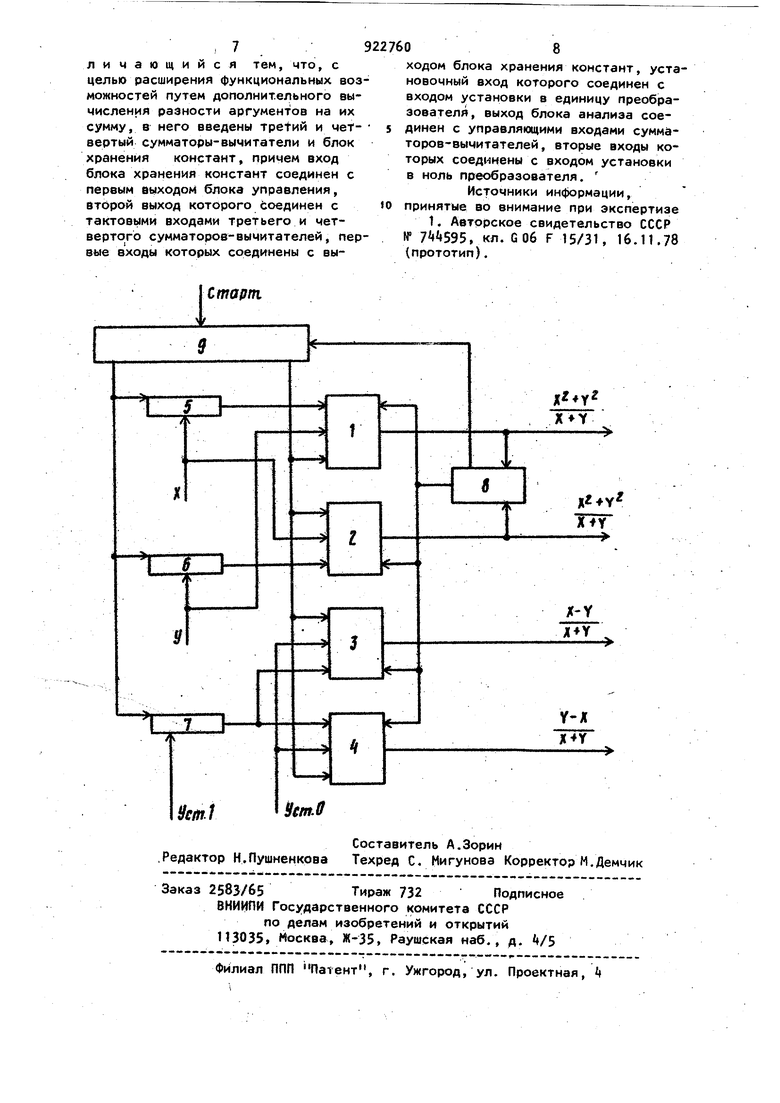

10 третий и .четвертый сумматоры-вычитатели и блок хранения констант, причем вход блока хранения констант соединен с первым выходом блока управления, второй выход которого соедин с тактовыми входами третьего и четв того сумматоров-вычитателей, первые входы которых соединены с выходом блока хранения констант, установочный вход которого соединен с входом установки в единицу преобразователя выход блока анализа соединен с упра ляющими входами сумматоров-вычитате лей, вторые входы которых соединены с входом установки в ноль преобразо вателя. На чертеже приведена блок-схема преобразователя. Преобразователь содержит сумма- торы-вычитатели 1-4, регистры 5-6, блок 7 хранения констант, блок 8 анализа и блок 9 управления. Входами преобразователя являются информационные вхоДы регистра 5 (дл аргументе ч) и регистра 6 (для аргумента :(} , установочный вход блока 7 хранения констант для записи единицы) и вторые входы сумматоров вычитателей 3- (для установки нуля). Стартовый импульс (начало вычисления) подается на второй вход блока 9 управления. Выходами преобразователя являются выходы сум аторов-вычитателей 1-i. Сумматор-вычитатель 1- может быть выполнен из одноразрядного сум матора-вычитателя и накопительного сдвигового регистра. Первый вход Одноразрядного сумматора является первым входом сумматора-вычитателя, второй вход которого является инфо мационным входом регистра, выход которого является выход сумматоравычитателя. Выход младшего разряда регистра соединен с другим входом одноразрядного сумматора-вычитателя, выход которого соединен с входом старшего разряда регистра. Тактовый вход соединен с входом сдвига регистра. Управляющий вход соединен с входом одноразрядного сумматоравычитателя, сигнал на котором управляет режимом сложения-вычитателя по первому входу. Сумматор-вычитатель может быть реализован так же на параллельной комбинационной схеме. Регистр 5 или 6 содержит регистр и элементы. И и ИЛИ. Выход (от младшего разряда) регистра соединен через элемент И со своим входом (вход старшего разряда). Выходы блока управления Э через элемент ИЛИ соединены с входом сдвига регистра. При параллельном выполнении регистр может быть реализован в виде сдвигающей матрицы. Блок 8 анализа может содержать схему сравнения, входы которой являются входами блока 8. Первый и второй выходы схемы сравнения через первый и второй элементы И соединены с входами триггера. Третий выход схемы сравнения ( равенство ) соединен через третий элемент И с первым выходом блока 8 анализа. Вторые входы всех элементов И соединены с вторым выходом блока 9 управления. Блок 7 хранения констант вида 2 может быть реализован на сдвиговом рециркуляционном регистре,старший разряд которого соединен со схемой установки единицы, а на вход сдвига регистра подаются сдвигающие тактовые импульсы (второй выход блока 9 управления). Блок 7 хранения констант может быть реализован в виде одностороннего запоминающего устройства. Работа данного преобразователя основана на одновременном решении системы рекуррентных разностных уравнений в интерационном процессе..где п - число разрядов аргумента. Все уравнения решаются одновременно (х в сумматоре-вычитателе 2; у, в сумматоре-вычитателе 1; 2 в сумматоре-вычитателе 3; Un сумматоре-вычитателе , оператор q;определяется в блоке В анализа, величина .U+i получается в регистре 5, величина получается в регистре 6, величина 2 формируется в блоке 7 формирования констант) , причем каждое из уравнений может 5 вычисляться либо послеловательно, либо параллельно. Вычисления в предлагаемом преобразователе осуществляются следующим образом. Перед началом работы в регистр 5 умматор-вычитатель 2 устанавливает ,. 9 первый аргумент х , в регистр 6 и в сумматор-вычитатель 1 устанавливается второй аргумент у. При после;Довательном принципе вычисления в бло 7формирования констант заносится единица (старший разряд регистра бл ка 7) . На вторые входы сумматоров-вы читателей 3- подается сигнал установки нулевого значения. Затем на блок 9 управления подается стартовый импульс. С первого выхода блока 9 управления на регистры 5-6 и блок 7 хранения констант подается тактовый импульс, который сдвигает значения регистров на оДин двоичный разряд вправо от двоичной запятой. Затем тактовые, импульсы свторого выхода блока 9 управления прод вигают содержания регистров 5-6 и регистры блока 7 на входы соответствующих сумматоров-вычитателей 1-1 8последних производится сложение или вычитание поступающих операндов . с предыдущими значениями. Режим сложения-вычитания на следующей итерации определяется по. разности X; - у в блоке 8 анализа : В случае положительной разности (х - у-7,0) с второго выхода GrloKa анализа выдается сигнал q- (в виде уровня напряжения), который определяет сложение в сумматорахвымитателях 1 и 3 и вычитание-в сумматорах-вычитателях 2 и k. При отрицательной разности в сумматорахвычитателях 2 и выполняется сложе ние, а всумматорах-вычитателях 1 и 3 выполняется вычитание. Изменение сигнала q. производится после выполнения каждой итерации в момент появления тактового импульса на первом выходе блока 9 управления. При выполнении п итераций или при равенстве содержания в сумматорах-вычитателях 1 и 2 вычисления заканчиваются и блок управления перестает выдавать тактовые импульсы Для большинства значений аргументов X и вычисления заканчиваются на итерации, номер которой j значитель но меньше значения п . В сумматорах-вычитателях содержится значение функции (х + у)/ K + У) V в сумматоре-вычитателе 3 содержится значение функции (х - у)/ /(х + у) , а в сумматоре-вычитателе А содержится значение функции (у - xj/ /(X + у) . Максимальное время вычисления одновременно трех указанных функций в предлагаемом преобразователе при использовании последовательных сумматоров- вычитателей в тактах равно n{n+m+1) ,гдеm -число дополнительных разрядов perVicTpoB и сумматоров для компенсации Иогреш-.. ности усечения чисел при сдвиге. Максимальное время вычисления при параллельном вычислении каждой итерации (при использовании параллельных сумматоров-вычитателей) в тактах равно Точность .вычисления определяется длиной разрядной сетки преобразователя и соответственно числом итераций. Повышение точности приводит к увеличению аппаратурных затрат и увеличению времени вычисления. По сравнению с известным предлагаемый преобразователь обладает расширенными функциональными, возможностями, поскольку обеспечивает одновременно с вычислением функции ( ) / ( X-t- ) также вычисление функций (х - у)/Чх + у) и (у х)/ /(х + у), причем время вычисления остается прежним. Расширение функциональных возможностей достигается путем минимальных затрат, путем добавления только двух сумматоров-вычитателей и блока формирования констант. Предлагаемый преобразователь предназначен для аппаратной реализации вычисления указанных функций, которые находят широкое применение в измерительной технике (для подсчета коэффициента модуляции, определения относительных погрешнрстей), в радиолокационной технике например, при нормировании сигналов условных оши бок, при автосопровождении и т.д.), в специализированных вычислителях для научных расчетов и управления технологическими процессами и физическими объектами. Формула изобретения Цифровой функциональный преобразователь по авт.св. № , о т личающийся тем, что, с целью расширения функциональных воз можностей путем дополнительного вычисления разности аргументов на их сумму, в него введены тpetий и четвертый сумматоры-вычитатели и блок хранения констант, примем вход блока хранения констант соединен с первым выходом блока управления, второй выход которого Соединен с тактовыми входами третьего и четвертого сумматоров-вычитателей, пер вые входы которых соединены с выI Старт Ф 08 ходом блока хранения констант, установочный вход которого соединен с входом установки в единицу преобразователя, выход блока анализа соединен с управляющими входами сумматоров-вычитателей, вторые входы которых соединены с входом установки в ноль преобразователя. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № , кл. G06 F 15/31, 16.11.78 (прототип).

Авторы

Даты

1982-04-23—Публикация

1980-01-18—Подача