Изобретение относится к вычислительной технике и может быть использовано в вычислительнЬк системах для сопряжения, например, периферийного устройства, осуществляющего последовательную выдачу данных, с оперативной памятью.

Известны устройства для сопряже- . ния, содержащие блок коммутации, преобразователь кода, блок буферной памяти, узел формирования, два триггера, регистры управления и группу элементов И 1.

Недостаток этих устройств состоит в низкой достоверности обработки информации.

Наиболее близким по технической сущности к предлагаемому является устройство для управления передачей данных, с:одержащее коммутатор информационного массива, регистр-счетчик начального адреса, регистры конечно-, го адреса и информации, схему сравнения адресов, блок управления и коммутатор адресов памяти. Для ввода информации в память в этом устройстве используются два. первых слова массива, в первом - начальный адрес п.чмяти, во втором - количество cnot(2)

Недостаток этого устройства низкая достоверность обработки из-за отсутствия контроля адресных слов и массива передаваемой информации.

Цель изобретения - повышение достоверности обработки массивов информации .

Поставленная цель достигается тем,, что в устройство, содержащее

10 коммутатор входной информации, первый и второй входы которого подключены соответственно К информационному входу устройс;тва и к первому выходу блока управления, а первый,

15 второй и третий выходы - соответственно к первым входам счетчика адреса, регистра конечного адреса .и регистра информации, второй и третий входы счетчика адреса соеди20нены соответственно с первым и вторьм выходами, блока управления, а первый и второй выходы соответственно с первыми входами коммутатора адресов памяти и схемы сравнения

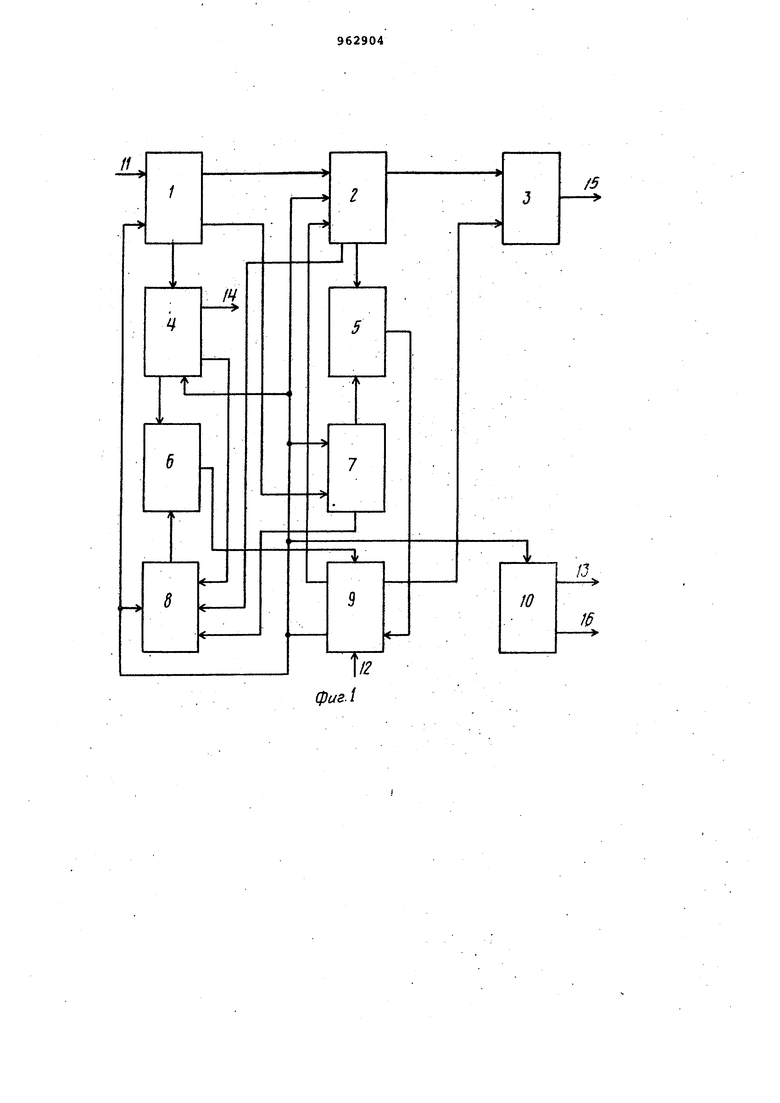

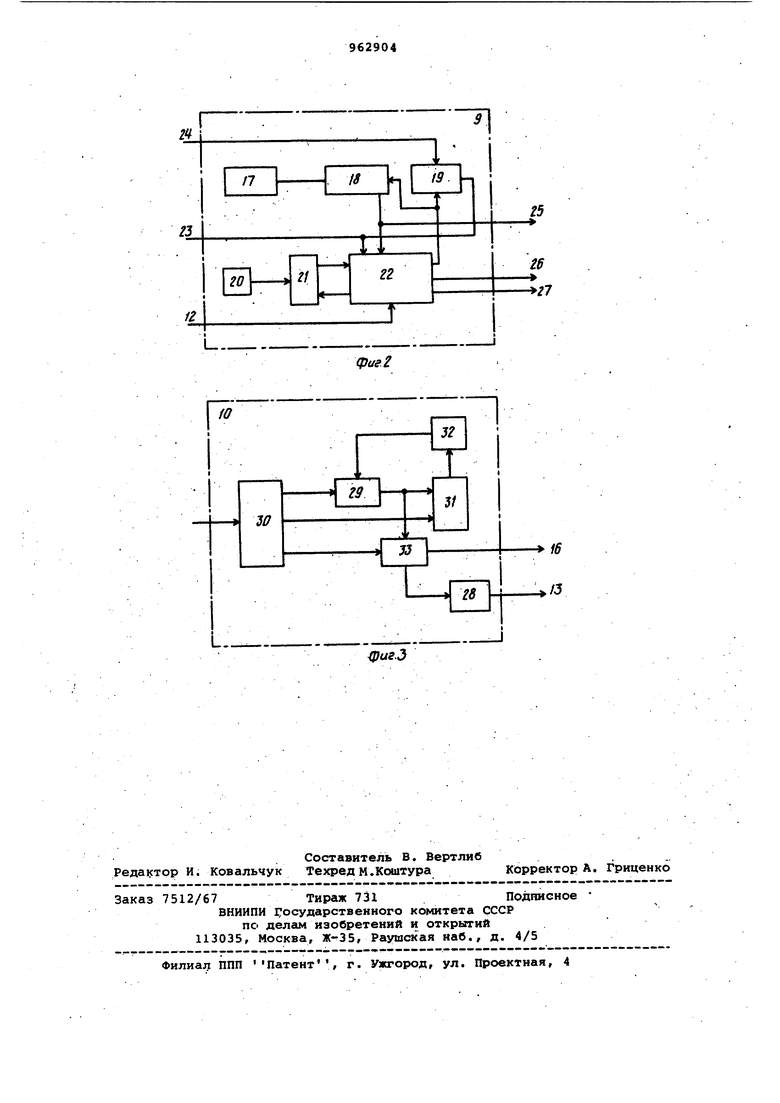

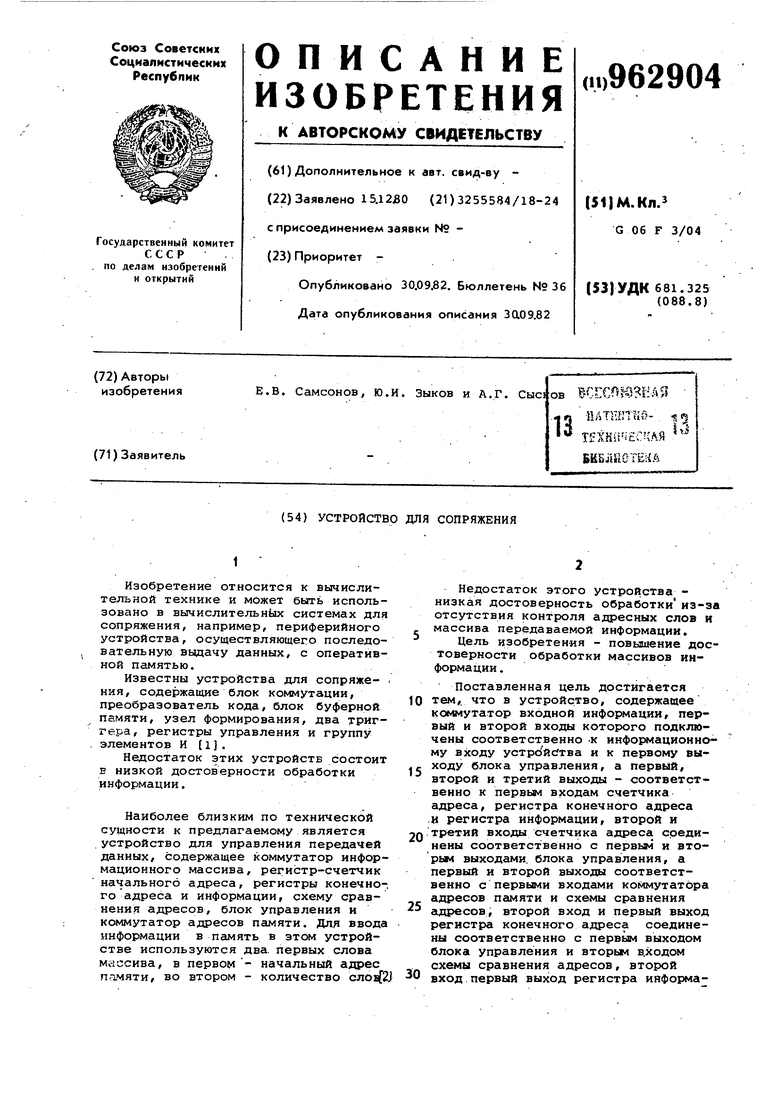

25 адресов, второй вход и первый выход регистра конечного адреса соединены соответственно с первым выходом блока управления и вторые в.ходом схемы сравнения адресов, второй 30 вход первый выход регистра информаЦии соединены соответственно с первым выходом блока управления и инфор мационньм выходом устройства, второй вход и первый выход коммутатора адресов памяти соединены соответственно с третьим выходсэм блоки управления и адресным выходом устройства, перв.ый и второй входы блока управления соединены соответственно со входом команд устройства и выходом схемы сравнения, введены формирователь управляющих слов,схем сравнения информации и сумматор, причем первый - четвертый входы сум матора соединены соответственно с первым выходом блока управления, с третьим выходом счетчика адреса, с вторыми выходами регистра конечного адреса и регистра информации, а выход - с первым входом схемы сра нения информации, второй вход которой соединен с третьим выходом регистра информации, а выход - с третьим входом блока управления,пер вый выход которого соединен с входо формирователя управляющих слов, два выхода которого подключены соответственно к выходу передачи управляющих слов и выходу прерывания устрой ства. . Кроме того, формирователь управляющих слов содержит входной дешифратор, генератор импульсов, счетчик тактов, дешифратор числа тактов, регистр сдвига и дешифратор команды прерывания, причем вход входного дешифратора является входом формиро вателя, а выходы подключены соответственно к первым входам генератора импульсов, счетчика тактов и регистра сдвига, первый выход которого соединен с первым выходом фор мирователя, второй выход через дешифратор команды прерывания с вторы выходом формирователя, а второй вход - с выходом генератора импульсов и вторым входом счетчика тактов выход которого через деи ифратор чис ла-тактов подключен к второму входу генератора импульсов, На фиг.1 представлена блок-схема устройства; на фиг.2 и 3 -.функциональные схемы блока управления и формирователя управляющих слов, Устройство содержит (фиг. 1) -коммутатор 1 входной информации,счетчик 2 адреса, коммутатор 3 адресов памяти, регистр 4 информации, схему 5 сравнения адресов, схему б сравне ния информации, регистр 7 конечного адреса, сумматор 8, блок 9-управлен формирователь 10 управляющих слов, шины 11 входной последовательной информации информационного входа устройства, шины 12 входа команд устройства, шины 13 выхода передачи управляющих слов устройства, шины 14 информационного устройства, цданы 15 адресного выхода устройства и шины 16 выхода прерывания . устройства. Блок 9 управления (фиг.2) содержит элемент НЕ 17, элементы И 18 и 19, генератор 20 меток, счетчик 21 меток и дешифратор 22, входы 23, 24 и выходы 25-27 блока. Формирователь 10 управляющих слов содержит (фиг.З) дешифратор 28 команды прерывания, генератор 29 импульсов, входной дешифратор 30, счетчик 31 тактов, дешифратор 32 числа тактов и регистр 33 сдвига. Устройство работает следующим образом.. Информационный массив, поступающий по шинам 11, состоит из паспорта, (первые три слова), тела массива и контрольной паспорта и тела массива (последнее слово). Паспорт по порядку следования состоит из следующих слов - начальный адрес памяти, конечный адрес памяти и контрольная сумма первых двух слов. При поступлении команды начать ввод по шинам 12 блок 9 с первого выхода выдает сигналы установки в исходное коммутатора 1, счетчика 2, регистров 4 и. 7 и сумматора 8, а также вывод команды запрос по шинам 13. Первое слово, поступающее по шинам 11, заносится в счетчик 2, после чего складывается с содержимым сумматора 8. второе слово поступает в регистр 7, после чего складывается с содержимым сумматора 8, Третье слово поступает в регистр 4 информации. Блок 9 читает состояние схемы 6 сравнения. При положительном результате контроля паспорта .блок 9 через формирователь 10 по шинам 13 выводит команду готовность, при отрицательном - в процессор по шинам 16 передается сигнал прерывания, а по шинам 13 - код отрицательный результат контроля . После вывода команды готовность организуется следующий цикл работы. Очередное слово поступает на регистр 4, складывается с содержимым сумматора 8. Блок 9, опрашивая схему 6 сравнения, модифицирует счетчик 2 и организует передачу в па-мять содержимого регистра 4 по шинам 14 по адресам коммутатора 3; блок 9 опрашивает схему 5 сравнения, причем, если содержимое счетчика 2 не сравнилось с содержимым 7, то блок 9 через формирователь 10 производит по шинам 13 вывод команды готовность на очередное слово. Если содержимое счетчика 2 сравнилось с содержимым регистра 7 то блок 9 через формирователь 10 производит вывод команды готовность, , подготавливает блокировку приема информации сумматором 8 от регистра 4. После приема очередного слова блок 9 опрашивает схему 6 сравнения Если содержимое регистр 6 и сумматора 8 сравнилось, то через формирователь 1.0 в процессор по шинам 16 передается сигнал прерьшания, а по шинам 13 - код конец ввода . Есл содержимое регистра 4 и сумматора 8 не сравнилось, то через формирователь 10 в процессор по шинам 16 передается сигнал прерывания, а по шинам 13 - код отрицательный результат контроля . Таким образом, устройство позволяет обеспечить защиту принимаемого массива и повысить достоверность обработки и ввода массивов информац Формула изобретения 1. Устройство для сопряжения, содержащее коммутатор входной информации, первый и второй входы которого подключены соответственно к информационному входу устройства и к первому выходу блока управления, а первый, второй и третий выходы соответственно к первым входам счетчика адреса, регистра конечного адреса и регистра информации, второ к третий входы счетчика адреса сое динены соответственно с первым и вт рьш1 вьгхо.цами блока управления, а первый и второй выходы - соответст венно с пгрвыми входами коммутатора адресов памяти и схемы сравнени cycipe OB, второй вход и первый выход регистра конечного адреса соединен соответственно с первым выходом бл а управления и вторым входом схемы сравнения адресов, второй вход и первый выход регистра информации соединены соответственно с первьдм выходо.м блока управления и информа ционным выходом устройства, второй вход я выход коммутатора адресов памяти соединены соответственно с третьим выходом блока управления и адресным выходом устройства, первы ;И второй входы блока управления соединены соответственно с входом команд устройства и выходом схемы сравнения, отлич ающе еся тем, что, с целью повышения достоверности обработки массивов информации, в устройство введены формирователь управляющих слов, схема сравнения информации и сумматор,причем первый - четвертый входы сумматора соединены соответственно с первым выходом блока управления, с третьим выходом счетчика адреса, с вторыми выходами регистра конеч- , ного адреса и регистра информации, а выход - с первым входом схемы сравнения информации, второй вход которой соединен с третьим выходом регистра информации, и выход - с третьим входом блока управления, первый выход которого соединен с формирователя управляющих слов, два выхода которого подключены соответственно к выходу передачи управляющих слов и выходу прерывания устройства. -2. Устройство по п, 1, о т л ичающееся тем, что формирователь управляющих слов содержит входной дешифратор, генератор импульсов, счетчик тактов, дешифратор числа тактов, регистр сдвига и дешифратор команды прерывания, причем вход входного дешифратора является входом формирователя, а выходы подключены соответственно к первым входам генератора импульсов, счетчика тактов и регистра сдвига, первый выход которого соединен с первым выходом формирователя, второй выход через .дешифратор команды прерывания - с вторым выходом формирователя, а второй вход - с выходом генератора импульсов и вторьм входом счетчика тактов, выход которого через дешифратор числа тактов подключен к второму входу генератора импульсов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 516031, кл. G 06 F 3/00, 1973. 2.Патент США № 4133030, кл. 364-200, опублик. 1978 (прототип) .

фиг.1

L..

фиг.Э

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения периферийного устройства с ЭВМ | 1987 |

|

SU1451707A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

Авторы

Даты

1982-09-30—Публикация

1980-12-15—Подача