переноса во второй разряд данной тетрады разрядов устройства; выход переноса которого соединен с вторым входом второго элемента ИЛИ данной тетрады разрядов устройства, выход которого соединен с входом переноса в третий разряд данной тетрады разрядов устройства, входы блока коррекции данной teтpaды разрядов устройства подключены к выходу переноса из четвертого разряда данной тетрады разрядов устройства, к выходам суммы второго, третьего и четвертого разрядов данной тетрады разрядов устройства и к входу раз решения выполнения операций над десятично-двоичными числами устройства соответственно, при этом блок коррекции каждой тетрады разрядов устройства содержит элементы И, ИЛИ и триггер, причем входы первого элемента ИЛИ подклю 1ены к входам суммы второго и

третьего разрядов.данной тетрады разрядов устройства блока соответственно, выход первого элемента ИЛИ подключен к первому входу первого элемента И, второй вход которого подключен к входу суммы третьего разряда данной тетрады разрядов устройства блока, выход первого элемента И подключен к первому входу второго элемента ИЛИ, второй вход которого подключен к входу переноса из четвертог разряда данной тетрады разрядов устройства, выход второго элемента ИЛИ подключен к входу триггера, выход которого подключен к первому входу второго элемента И, второй вход которого подключен к вхбду разрешения выполнения операций над десятично-двоичными числами устройства, второго элемента И подключен к выходу блока коррекции данной тетрады разрядов устройства. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Накапливающий сумматор | 1982 |

|

SU1166096A1 |

| Устройство для арифметической и логической обработки двоичных и двоично-десятичных @ -разрядных чисел | 1980 |

|

SU962922A1 |

| Суммирующее устройство с контролем | 1983 |

|

SU1140112A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Арифметическое устройство с микропрограммным управлением | 1990 |

|

SU1797108A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

ДВОИЧНО-ДЕСЯТИЧНОЕ АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО НАКАПЛИВАЮЩЕГО ТИПА, каждый разряд которого содержит элементы И, ИЛИ, элемент памяти и мультиплексор, стробирующий вход которого подсоединен к входу разряжения работы устройства, информационные входы мультиплексора подключены к первому, второму, третьему и четвертому настроечным входам устройства соответственно, управляющие входы мультиплексора подключены к информационному входу данного разряда устройства и к выходу элемента памя- , ти данного разряда устройства соответственно, вход которого подключен к выходу первого элемента ИЛИ, первый вход которого подключен к выходу мультиплексора, второй вход первого элемента ИЛИ подключен к входу переноса из предыдущего разряда устройства и к первому входу первого элемента И, второй вход которого подключен к выходу элемента памяти, вы ход первого элемента И соединен с первым входом второго элемента ИЛИ, выход элемента памяти подключен к выходу суммы данного ра;зряда устройства, отличающееся тем, что, с целью расширения области применения за счет возможности реализации операций над десятично-двоичными числами, каждая тетрада разрядов устройства содержит элементы ИЛИ и блок коррекции, каждый разряд устройства содержит элемент задержки и второй элемент И, первь1Й вход которого подключен к пятому настроечному входу устройства, второй, третий и четвертый входы второго Элемента И подключены к входу разрешения работы устройства, информационному входу данного разряда устройства и к ВЫХ9ДУ элемента памяти дан ного разряда устройства соответствен(Л но, выход второго элемента И соединен с вторым входом второго элемента ИЛИ, выход которого подключен к входу S элемента задержки, выход которого еподключен к выходу переноса из данного разряда устройства, при этом каждый элемент памяти содержит тригD N9 гер и элемент задержки, вход которого подключен к входу элемента памяiU ти, выход элемента задержки подклю:о чен к счетному входу триггера, выход которого подключен к выходу lib элемента памяти, выход блока коррекции каждой тетрады разрядов устройства подключен к первым входам элементов ИЛИ данной тетрады устройства, второй вход первого элемента ИЛИ данной тетрады разрядов устройства подключен к выходу переноса из первого разряда данной тет,рады разрядов устройства, выход первого элемента ИЛИ данной тетрады разрядов устройства соединен с входом

Устройство относится к вычислительной технике и предназначено для арифметической и логической обработки двоичных и двоично-десятичных кодов .

Известно устройство для сложения двоично-десятичных кодов, содержащее сумматоры, схемы переноса и коррекции tn.,

Недостатке устройства является то, что оно не реализует операций сложения двоичных кодов, а также не реализует логических операций.

Наиболее близким по технической сущности к изобретению является устройство для арифметической и логической обработки кодов, каждый разряд которого содержит элемент И, два элемента ИЛИ, триггер И два мультиплексора, входы которых подключены к управляющим входам устройства, а их управляющие входы подключены к информационным входам данного разряда и выходу триггера, счетный вход которого подключен к выходу первого элемента ИЛИ, входы которого подключены к выходу первого мультиплексора и выходу переноса разряда, Стробирующие входы мультиплексоров подключены к входу разрешения выполнения операций устройства. Выход второго мультиплексора подключен к первому входу второго элемента ИЛИ, выход которого является выходом переноса разряда, а его второй вход подключен к выходу элемента И, первый вход которого подключен к вхбду перенос разряда, а второй - к выходу триггера. Выход триггера, является выходом результата данного раЗряда 23. Недостатком известного устройства является то, что оно реализует операции арифметической и логической обра|6отки двоичных сичел, но не реализует операции над двоично-десятичными кодами, что ограничивает область его- применения.

Целью изобретения является расширение области применения за счет возможности реализации операций над двоично-десятичными числами.

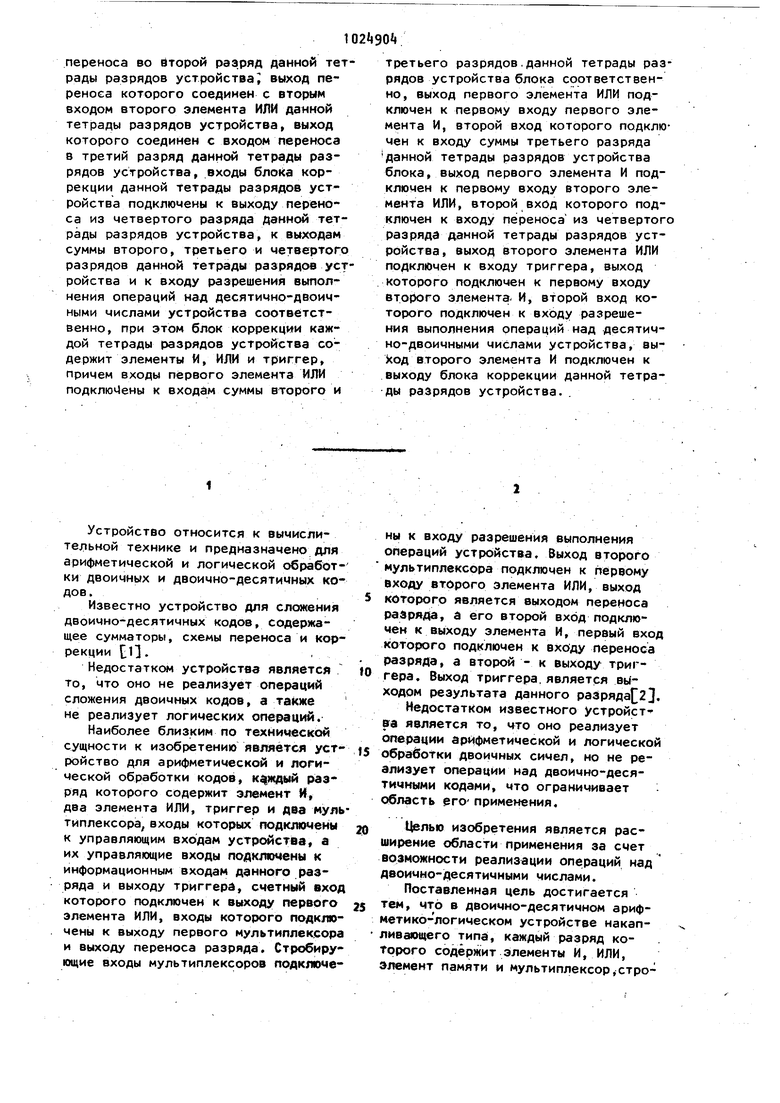

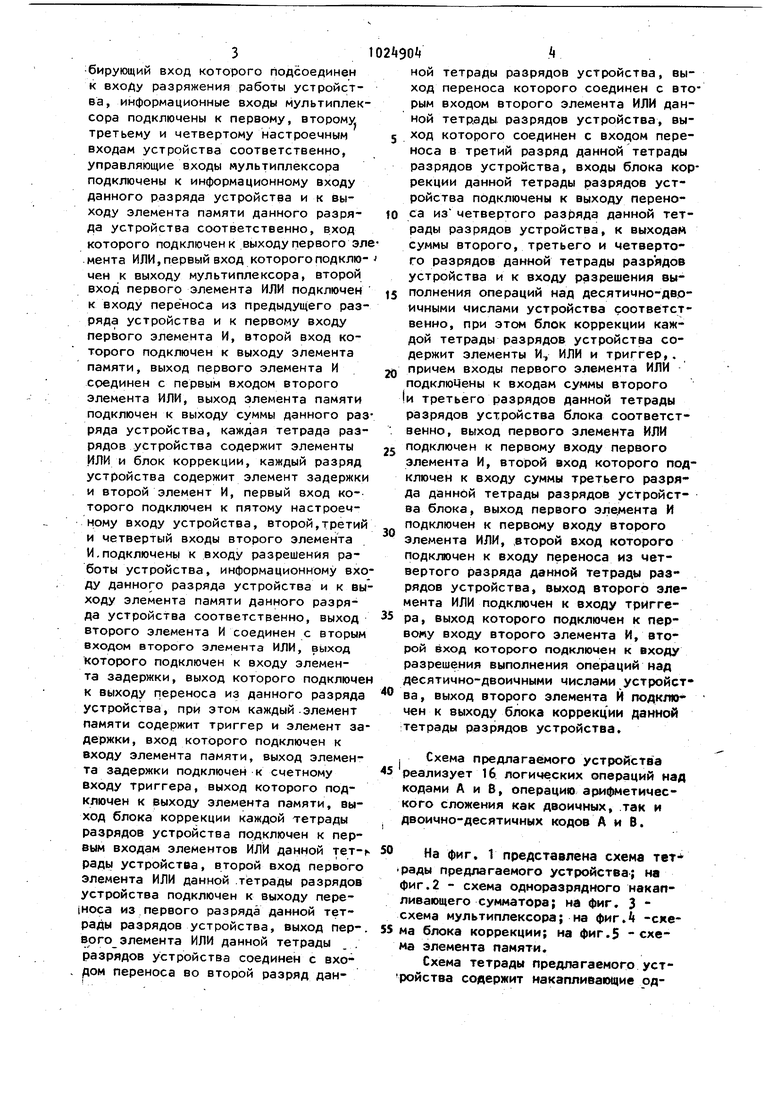

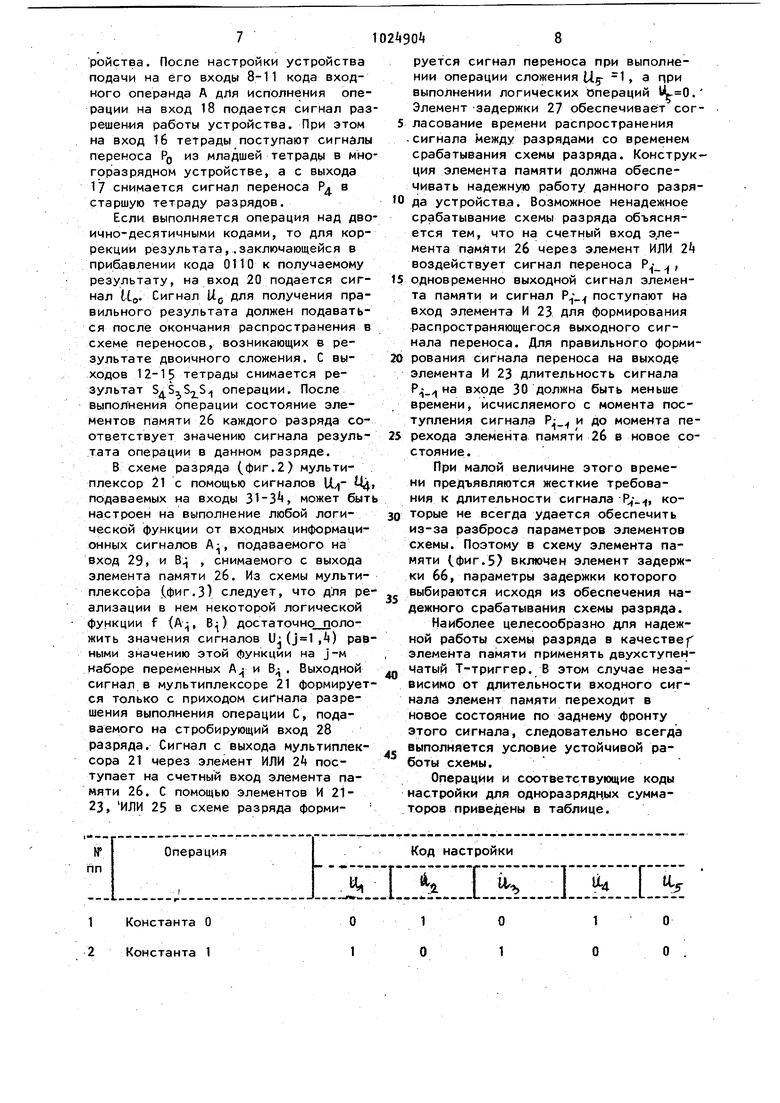

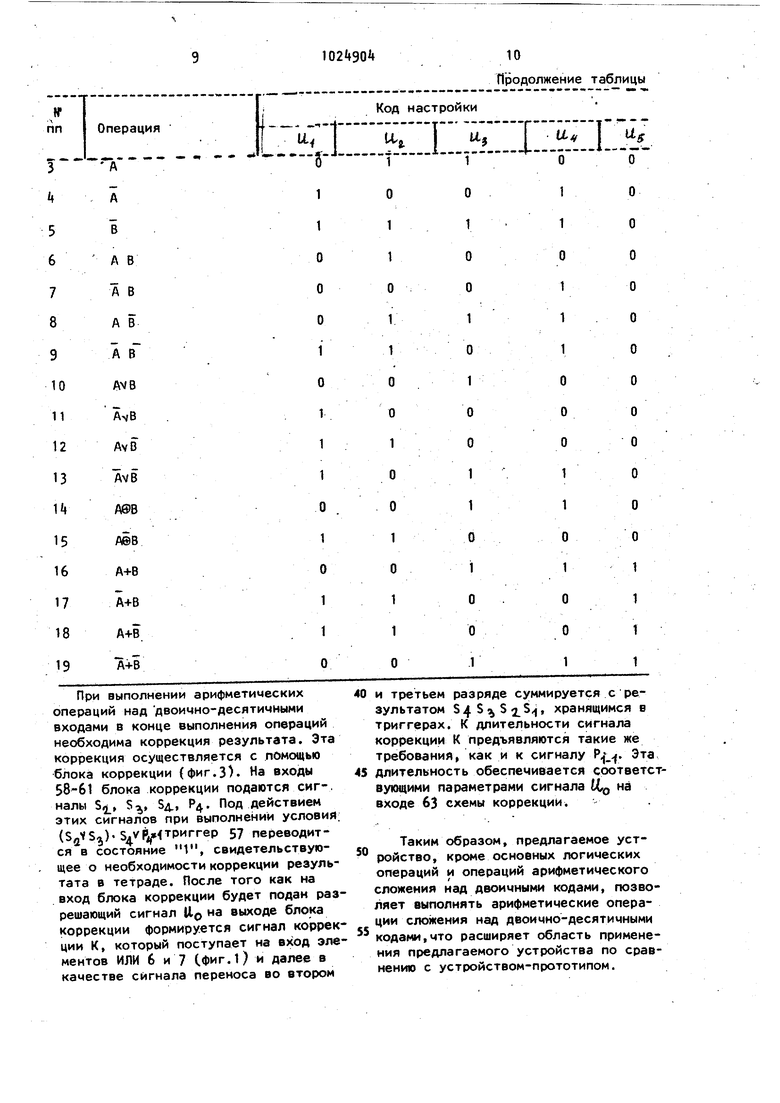

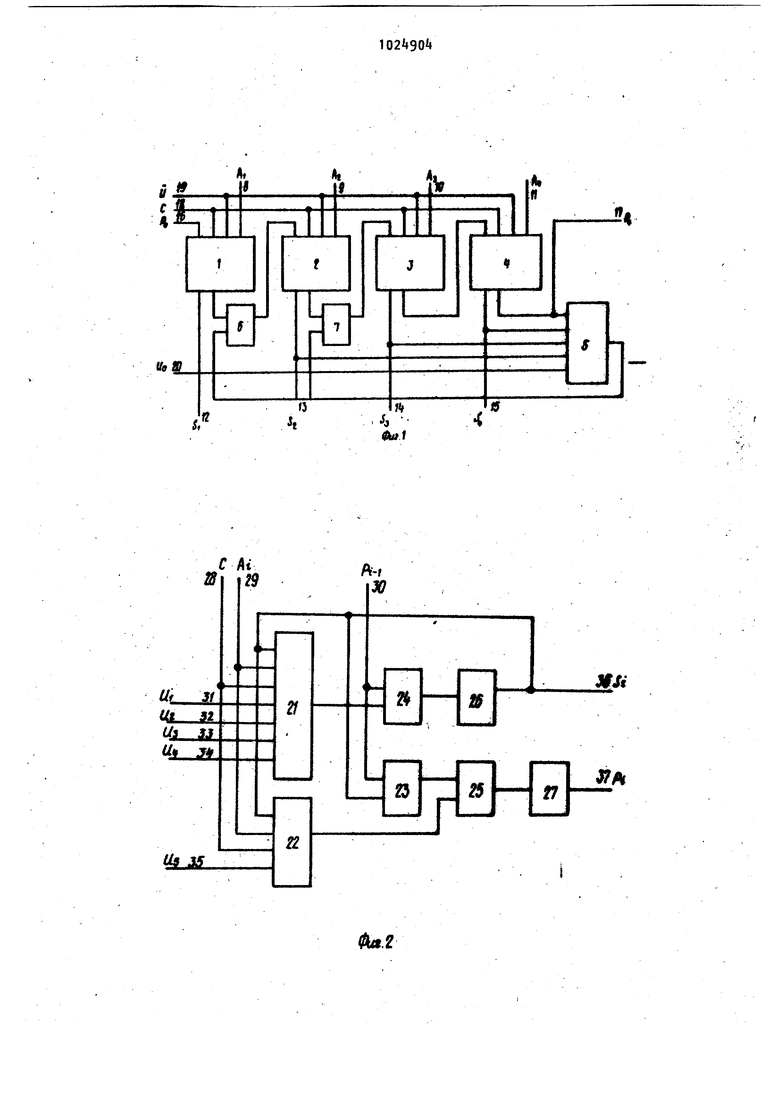

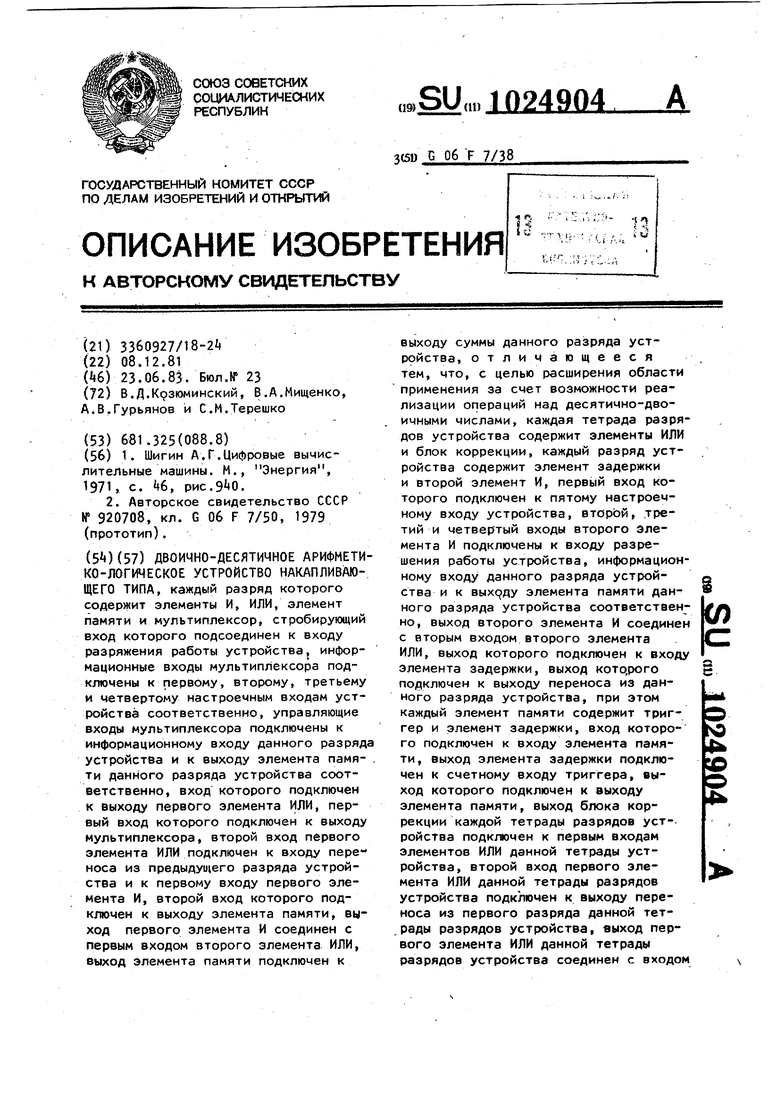

Поставленная цель достигается тем, что в двоично-десятичном арифметико-логическом устройстве накапливающего типа, каждый разряд которого содержит элементы И, ИЛИ, элемент памяти и мультиплексор,стробирующий вход которого подсоединен к входу разряжения работы устройства, информационные входы мультиплексора подключены к первому, второму третьему и четвертому настроечным входам устройства соответственно, управляющие входы мультиплексора подключены к информационному входу данного разряда устройства и к выходу элемента памяти данного разряда устройства соответственно, вход которого подключен к выходупервого эл . мента ИЛИ,первый вход которого подклюмен к выходу мультиплексора, второй вход первого элемента ИЛИ подключен к входу переноса из предыдущего разряда устройства и к первому входу первого элемента И, второй вход которого подключен к выходу элемента памяти, выход первого элемента И соединен с первым входом второго элемента ИЛИ, выход элемента памяти подключен к выходу суммы данного раз ряда устройства, каждая тетрада разрядов устройства содержит элементы ИЛИ и блок коррекции, каждый разряд устройства содержит элемент задержки и второй элемент И, первый вход которого подключен к пятому настроечному входу устройства, второй,третий и четвертый входы второго элемента И,подключены к входу разрешения работы устройства , информационному вхо ду данного разряда устройства и к вы ходу элемента памяти данного разряда устройства соответственно, выход второго элемента И соединен с вторым входом второго элемента ИЛИ, выход которого подключен к входу элемента задержки, выход которого подключе к выходу переноса из данного разряда устройства, при этом каждый -элемент памяти содержит триггер и элемент за держки, вход которого подключен к входу элемента памяти, выход элемента задержки подключен к счетному входу триггера, выход которого подключен к выходу элемента памяти, выход блока коррекции каждой тетрады разрядов устройства подключен к первым входам элементов ИЛИ данной тетрадь устройства, второй вход первого элемента ИЛИ данной .тетрады разрядов устройства подключен к выходу пере носа из первого разряда данной тетрады разрядов устройства, выход перврго элемента ИЛИ данной тетрады разрядов устройства соединен с входом переноса во второй разряд дан0тетрады разрядов устройства, выход переноса которого соединен с вторым входом второго элемента ИЛИ данной тетрады разрядов устройства, выход которого соединен с входом переноса в третий разряд данной тетрады разрядов устройства, входы блока кор рекции данной тетрады разрядов устройства подключены к выходу переноса из четвертого разряда данной тетрады разрядов устройства, к выходам суммы второго, третьего и четвертого разрядов данной тетрады разрядов устройства и к входу разрешения выполнения операций над десятично-двоичными числами устройства соответственно, при этом блок коррекции каждой тетрады разрядов устройства содержит элементы И., ИЛИ и триггер,. причем входы первого элемента ИЛИ подключены к входам суммы второго 1и третьего разрядов данной тетрады разрядов устройства блока соответственно, выход первого элемента ИЛИ подключен к первому входу первого элемента И, второй вход которого подключен к входу суммы третьего разряда данной тетрады разрядов устройства блока, выход первого элемента И подключен к первому входу вторюго элемента ИЛИ, .второй вход которого подклочен к входу переноса из четвертого разряда данной тетрады разрядов устройства, выход второго элемента ИЛИ подключен к входу триггера , выход которого подключен к первому входу второго элемента И, второй вход которого подключен к входу разрешения выполнения операций над десятично-двоичными числами устройст ва, выход второго элемента И подкл чен к выходу блока коррекции данной тетрады разрядов устройства. Схема предлагаемого устройства реализует 16 логических операций над кодами А и В, операцию арифметического сложения как двоичных, .так и двоично-десятичных кодов А и В. На фиг, 1 представлена схема тет рады предлагаемого устройства; на фиг.2 - схема одноразрядного накапливающего сумматора; на фиг. 3 схема мультиплексора; на фиг.4 -скема блока коррекции; на фиг.5 -схема элемента памяти. Схема тетрады предлагаемого устройства содержит накапливающие од5норазрядные сумматоры 1-, блок коррекции 5 элементы ИЛИ 6 и 7у информационные входы 8-11, выходы результата 12-15, вход переноса 16 и выход переноса 17, вход разрешения работы устройства 18, группу входов настроек 19 и вход настройки 20. Одноразрядный накапливающий сумм тор содержит мультиплексор 21, элементы И 22 и 23, ИЛИ 2 и 25, элемент памяти 26, элемент задержки 27,стробирующий вход 28, информационный вход 29, вход переноса 30, настроечные входы 31-35, выход результата 36 и выход переноса 37. Мультиплексор содержит элементы И , ИЛИ it2, НЕ 3 и kk, управляющие входы , синхровход kf f информационные входы 48-51, выход 52.: Блок коррекции содержит элементы И 53 и 5А, ИЛИ 55 и 56, триггер 57, входы 58-63 и выход 6k, Элемент памяти содержит трИ1- гер б5, счетный вход которого подключен к выходу элемента задержки 66, вход которого является счетным Входом элемента памяти 67 а выход триггера подключен к выходу элемента памяти 68. В схеме одноразрядного накапливающего сумматора ( фиг.2) управляющие входы мультиплексора 21 подклЮ чены к стробирующему входу разряда 28,к информационному входу 29 и выходу элемента памяти 26, информационные входы мультиплексора 21 под ключены кНастроечным входам разряда. Выход мультиплексора 21 со динен с входом элемента ИЛИ 2U, дру гой вход которого подключен к еходу переноса 30 разряда, а его выход счетному входу элемента памяти 2б, выход которого является выходом результата 36 разряда. Входы элемента И 22 подключены соответственно: 1-й вход к выходу элемента памяти 2б, 2-й вход к информационному входу 29 разряда, 3-й вход объединен с синхровходом мультиплексора 21 и подключен к стробирующему входу 28, k-й вход - к настроечному входу 35. Выход элемента И 22 соединен с вхо дом элемента ИЛИ 25, другой вход которого подключен к В1ходу злемемта И 23, входы которого подключены к выходу элемента памяти 26 и входу переноса 30. Выход элемента задержки 27 является выходом переноса 37 tt разряда, а его вход подключен к выходу элемента И 25. В схеме тетрады устройства ( фиг.1) настроечные входы 3.1-35 одноразрядных накапливающих сумматоров (фиг.2) подключены к группе настроечных входов 19 устройства, а их стробирующие входы 28 - к соответствующему входу 18 устройства. Вход переноса одноразрядного накапливающего сумматора 1 является входом переноса 16 тетрады, а выход переноса накапливающего сумматора 4 - выходом переноса 17 тетрады. Входы блока коррекций 5 подключены к выходам результатов разрядов сумматоров 2- и выходу переноса сумматора . Выход блока коррекции подключен к первым входам элементов ИЛИ 6 и 7, вторые входы которых подключены к выходам переноса соответственно разрядов сумматоров 1 и 2, а выходы элементов ИЛИ 6 и 7 подключены к входам переносов соответственно разрядов сумматоров 2 и 3. В блоке коррекции (фиг.i) входы элемента ИЛИ 55 подключены к входам блока 58 и 59 э его выход - с первым входом элемента И 53, второй вход которого подключен к входу 60 блока. Выход элемента И 53 соединен с входом элемента ИЛИ 5б, другой вход которого подключен к входу 61 блока коррекции. Выход элемента ИЛИ 56 подключен к входу установки триггера 57 в единичное состояние, а его нулевой вход - к входу 62 уста- новки блока коррекции в исходное состояние. Выход триггера 57 соединен с входом элемента И 5, другой вход которого подключен к входу 63 блока коррекции, а выход элемента И 5 является выходом 6 блока коррекции. I Устройство работает следующим образом. На информационные входы 8-11 тетрады устройства 6фиг.1) подается четырехразрядный двоичный или двоичноДесятичный код А4 А 2 А . Код второго операнда, участвующего в выполняемой операции, предварительно заносится в элемент памяти 2б одноразрядных сумматоров (фиг.2. Настройка устройства на выполнение требуемой операции осуществляется с помощью группь настроечных входов 19, которая включает настроечные входы разрядов устройства. После настройки устройства подачи на его входы 8-11 кода входного операнда А для исполнения операции на вход 18 подается сигнал раз решен-ия работы устройства. При этом на вход 16 тетрады поступают сигналы переноса Р из младшей тетраду в мно горазрядном устройстве, а с выхода 17 снимается сигнал переноса Рд в старшую тетраду разрядов. Если выполняется операция над дво ично-десятичными кодами, то для коррекции результата,.заключающейся в прибавлении кода 0110 к получаемому результату, на вход 20 подается сигнал UQ. Сигнал U.Q для получения правильного результата должен подаваться после окончания распространения в схеме переносов, возникающих в результате двоичного сложения. С выходов 12-15 тетрады снимается результат операции. После выполнения операции состояние элементов памяти 26 каждого разряда соответствует значению сигнала результата операции в данном разряде. В схеме разряда (фиг.2) мультиплексор 21 с помощью сигналов Щ- Ц4 подаваемых на входы 31 З может быт настроен на выполнение любой логической функции от входных информационных сигналов А-, подаваемого на вход 29, и В , снимаемого с выхода элемента памяти 26. Из схемы мультиплексора {.фиг.3) следует, что ре ализации в нем некоторой логической функции f tA достаточно положить значения сигналов U-(j 1 ,) рав ными значению этой функции на j-м наборе переменных А и В . Выходной сигнал в мультиплексоре 21 формирует ся только с приходом сигнала разрешения выполнения операции С, подаваемого на стробирующий вход 28 разряда. Сигнал с выхода мультиплексора 21 через элемент ИЛИ 2k поступает на счетный вход элемента памяти 26. С помощью элементов И 2123, ИЛИ 25 в схеме разряда формируется сигнал переноса при выполнении операции сложения Ц5- -1 , а пРи выполнении логических Операций . Элемент задержки 27 обеспечивает согласование времени распространения сигнала между разрядами со временем срабатывания схемы разряда. Конструкция элемента памяти должна обеспечивать надежную работу данного разряда устройства. Возможное ненадежное срабатывание схемы разряда объясняется тем, что на счетный вход э.лемента памйти 2б через элемент ИЛИ 2k воздействует сигнал переноса одновременно выходной сигнал элемента памяти и сигнал поступают на вход элемента И 23 для формирования распространяющегося выходного СИ1- нала переноса. Для правильного формирования сигнала переноса на выходе элемента И 23 длительность сигнала входе 30 должна быть меньше времени, исчисляемого с момента поступления сигнала Р: и до момента перехода элемента памяти 2б в новое состояние. При малой величине этого времени предъявляются жесткие требования к длительности сигнала , которые не всегда удается обеспечить из-за разброса параметров элементов схемы. Поэтому в схему элемента памяти (,фиг.5) включен элемент задержки 66, параметры задержки которого выбираются исходя из обеспечения надежного срабатывания схемы разряда. Наиболее целесообразно для надежной работы схемы разряда в качестве f элемента памяти применять двухступенчатый Т-триггер. В этом случае независимо от длительности входного си|- нала элемент памяти переходит в Новое состояние по заднему фронту этого сигнала, следовательно всегда выполняется условие устойчивой работы схемы. Операции и соответствующие коды настройки для одноразрядных сумматоров приведены в таблице.

При выполнении арифметимеских операций над двоично-десятичными входами в конце выполнения операций необходима коррекция результата. Эта коррекция осуществляется с помощью блока коррекции (фиг.З). На входы 58-61 блока коррекции подаются сиг-, налы S, S-J, 5д., Рд. Под действием этих сигналов при выполнении условия; (SjiVS)S viV4TpHrrep 5 переводится в состояние 1, свидетельствующее о необходимости коррекции результата в тетраде. После того как на вход блока коррекции будет подан разрешающий сигнал U-o на выходе блока коррекции формируется сигнал коррекции К, который поступает на вход элементов ИЛИ 6 и 7 СФИГ.1) и далее в качестве сигнала переноса во втором

10 Продолжение таблицы

40 и третьем разряде суммируется с результатом $4 S 52.5, хранящимся в триггерах. К длительности сигнала коррекции К предъявляются такие же требования, как и к сигналу . Эта

45 длительность обеспечивается соответствующими параметрами сигнала it на входе 63 схемы коррекции.

Таким образом, предлагаемое устройство, кроме основных логических операций и операций арифметического сложения над двоичными кодами, позволяет выполнять арифметические операции сложения над двоично-десятичными кодами,что расширяет область применения предлагаемого устройства по сравнению с устройством-прототипом.

VAJ

и с 4

3

п

,

lOZOOi

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ШИРИН А.г.Цифровые вычислительные машины | |||

| М., Энергия, 1971, с | |||

| , рис. | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Накапливающий сумматор | 1979 |

|

SU920708A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-23—Публикация

1981-12-08—Подача