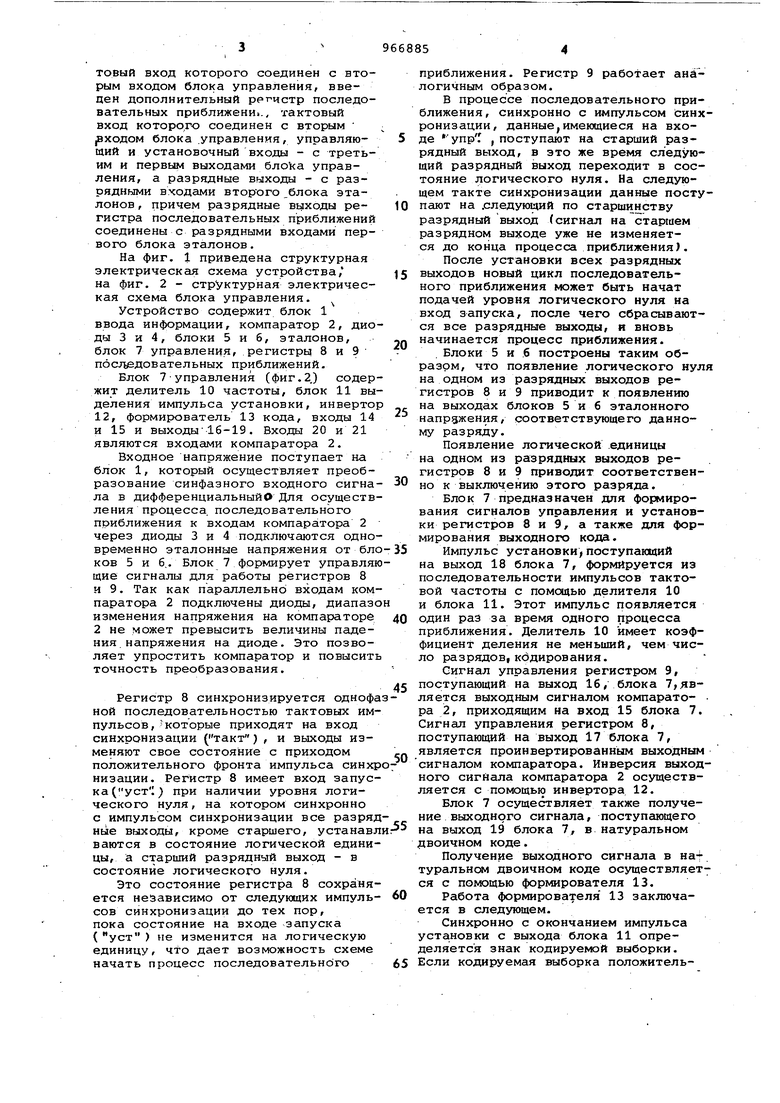

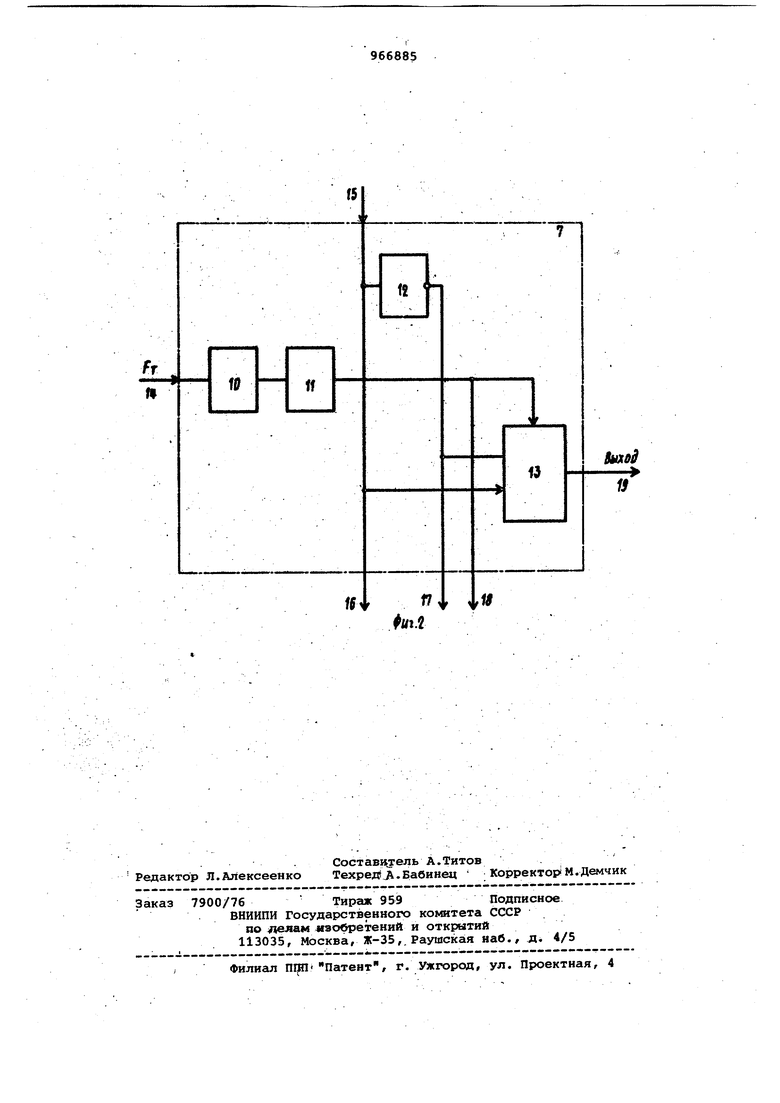

Изобретение относится к импульс ной технике и может быть использовано в системах связи и электронной коммутации. Известно кодирующее устройство последовательного приближения, содержащее генератор тактовых импульсов, выход которого через блок управления соединен с входами цифр аналогового преобразователя, выход которого соединен с входом компаратора, выход которого соединен с управляющим входом блока управления, а выход источника опорного напряжения соединен с опорным входом цифроаналогового преобразователя С . Недостатком устройства является низкая точность преобразования. Известно кодируюьдее устройство последовательного приближения, содержащее блок ввода информации, вы ходы которого соединены с входами компаратора, параллельно входам ко паратора подключены два диода, вкл ченных встречно-параллельно, входы компаратора соединены с выходами двух блоков эталонов, а выход с входом блока управления, первый и второй выходы которого соединены с установочным и управляющим входами регистра последовательного приближения, третий выход соединен с управляющими входами двух коммутаторов, разрядные входы которых подключены к разрядным выходам регистра последовательного приближения, а разрядные выходы к разрядным входам блоков эталонов 2 1. . Недостатком устройства является низкая точность преобразования. Цель изобретения - повьлшение точности преобразования. Указанная цель достигается тем, что в кодирующее устройство последовательного приближения, содержащее блок ввода информации, первый выход которого соединен с первым входом, компаратора, выходом первого блока эталонов, анодом первого и катодом второго диодов, второй выход - с вторым входом компаратора, выходом второго блока эталонов, катодом первого и анодом второго диодов, выход компаратора соединен с первым входом блока управления, первый и второй . выходы которого соединены с убтановочным и управляющим входами регистра последовательных приближений, тактовый вход которого соединен с вторым входом блока управления, введен дополнительный регистр последовательных приближени., тактовый вход которого соединен с вторым ,входом блока .управления, управляющий и установочный входы - с третьим и первым выходами блoka управления, а разрядные выходы - с разрядными входами второго блока эталонов , причем разрядные выходы регистра последовательных приближений соединены с разрядными входами первого блока эталонов. На фиг. 1 приведена структурная электрическая схема устройства/ на фиг. 2 - структурная электрическая схема блока управления. Устройство содержит блок 1 ввода информации, компаратор 2, дио ды 3 и 4, блоки 5 и 6, эталонов, блок 7 управления, регистры 8 и 9 последовательных приближений. Блок 7 управления (фиг.2.) содер жит делитель 10 частоты, блок 11 вы деления импульса установки, инверто 12, формирователь 13 кода, входы 14 и 15 и ВЫХОДЫ16-19. Входы 20 и 21 являются входс1ми компаратора 2. Входное напряжение поступает на блок 1, который осуществляет преобразование синфазного входного сигна ла в дифференциальныйО Для осуществ ления процесса, последовательного приближения к входам компаратора 2 через диоды 3 и 4 подключаются одно временно эталонные напряжения от бл ков 5 и 6.. Блок 7 формирует управля щие сигналы для работы регистров 8 и 9. Так как параллельнЬ входам ком паратора 2 подключены диоды, диапаз изменения напряжения на компараторе 2 не может превысить величины падения напряжения на диоде. Это позволяет упростить компаратор и повысит точность преобразования. Регистр 8 синхронизируется одноф ной последовательностью тактовых им пульсов, которые приходят на вход синхронизации ( , и выходы изменяют свое состояние с приходом положительного фронта импульса синх низации. Регистр 8 имеет вход запус ка (уст ) при наличии уровня логического нуля, на котором синхронно с импульсом синхронизации все разря ные выходы, кроме старшего, устанав ваются в состояние логической едини цы, а старший разрядный выход - в состояние логического нуля. Это состояние регистра 8 сохраня ется независимо от следующих импуль сов синхронизации до тех пор, пока состояние на входе запуска ( уст ) не изменится на логическую единицу, что дает возможность схеме начать процесс последовательного приближения. Регистр 9 работает аналогичным образом. В процессе последовательного приближения, синхронно с импульсом Синхронизации, данные,имеющиеся на входе упрГ , поступают на старший разрядный выход, в это же время следующий разрядный выход переходит в состояние логического нуля. На следующем такте синхронизации данные поступают на .следующий по старшинству разрядный выход (сигнал на старшем разрядном выходе уже не изменяется до конца процесса приближения). После установки всех разрядных выходов новый цикл последовательного приближения может быть начат подачей уровня логического нуля на вход запуска, после чего сбрасываются все разрядные выходы, и вновь начинается процесс приближения. Блоки 5 и б построены таким образом, что появление логического нуля на одном из разрядных выходов регистров 8 и 9 приводит к появлению на выходах блоков 5 и б эталонного напрджения, соответствз щего данному разряду. Появление логической единицы на одном из разрядных выходов регистров 8 и 9 приводит соответственно к выключению этого разряда. Блок 7 предназначен для формирования сигналов управления и установки регистров 8 и 9, а также для формирования выходного кода. Импульс установкИ|поступающий на выход 18 блока 7, формируется из последовательности импульсов тактовой частоты с помодью делителя 10 и блока 11. Этот импульс появляется один раз за время одного процесса приближения. Делитель 10 имеет коэффициент деления не меньший, чем число разрядов, кодирования. Сигнал управления регистром 9, поступающий на выход 16, блока 7,лвляется выходным сигналом компаратора 2, приходящим на вход 15 блока 7. Сигнал управления регистром 8, поступающий на выход 17 блока 7, является проинвертированным выходным сигналом компаратора. Инверсия выходного сигнала компаратора 2 осуществляется с помощью инвертора 12. Блок 7 осуществляет также получение выходного сигнала, поступающего на выход 19 блока 7, в натуральном двоичном коде. Получение выходного сигнгша в Haf туральном двоичном коде осуществляется с пo жэщью формирователя 13. Работа формирователя 13 заключается в следующем. Синхронно с окончанием импульса установки с выхода блока 11 определяется знак кодируемой выборки. Если кодируемая выборка положительна, то выходной сигнал компаратора поступает на выход 16 блока 7 непо редственно, если же выборка отрица тельна - то с выхода инвертора 12. В процессе уравновешивания рабо та отдельных блоков устройства и их взаимодействия осуществляются следующим образом. Процесс уравновешивания рассмат ривается для четырехразрядного кодирующего устройства. Введены еледующие обозначения:: К - логическ переменная, принимающая значение логический ноль (в дальнейшем если выходной сигнал компаратора 2 соответствует логическому нулю, или ая единица (в дальнейшем зсли выходной сигнал компаратора 2 соответствует логической единице, логическая переменьая К обозначает инверсию, логической переменной К, 1,1) напряжения на входах 20 и 21 компаратора в -м такте по.сле-. довательного приближения/ U -Ц.- U дифференциальное Йс1пряжение на входе компаратора 2 в i-M такте последолате-ibHoro приближения, ; и выходные напряжения блоко 5 и б в -м такте последовательного приближения. Блоки 5. и 6 имеют эталоны со следующими значениями: u2A, 4Д где величина 4д - соответствует эталону старшего разряда, а Дсоответственно млгщшего. В этом слу чае мак,симальная величина выборки кодируемого сигнала U «, Предположим, что вйтичина выборки сигнала, действующего на входе блока 1 11 3 1/2д, тогда напря жения U(4 и Uta, действующие на вхо дах 20 и 21 компаратора , определяются следующим образом: Ucu 1 3/4 и, Ucl -1 3/4 л. В первом такте процесса последов тельного приближения на входы уст регистров 8 и 9 подается уровень логического нуля, и с приходом поло жительного фронта тактовой частоты входы такт. регистров 8 и 9 стар шие разрядные выходы этих регистров устанавливаются в состояние логичес кого нуля, включая тем самы старши разряд в Обоих блоках 5 и б. напряжения гДЗ;, и U. входах :20 и 21 компаратора 2 определяются следующим образом Ч сг14г 1 -4 - |А.л , , г Ui-UcaVJav U U U --2ii-( Так как напряжеиие на входе 20 комп ратора 2 превышает напряжение на вх де 21, то (КгО),а это означаег, что в соответствии с алгоритмом работы блока 7 и регистров 8 и 9, стггрший разряд блока 5 должен остаться включенным до конца процесса приближения, а старший разряд блока 6 должен быть отключен. Данный тактовый интервал является моментом определения знака кодируемой выборки входного сигнала, а значение переменной означает, что данная выборка положительна.В следующий тактовый интервал с приходом положительного фронта тактовой час- f тоты регистры 8 и 9 выдают команду fa включение следующего по старшинству разряда блоков 5 и 6, при этом напряжения U соответственно равныи --ис,-иэг1яД-4л 2д-4|д1 UVUcx-V) . Ua-uVua---4|i-()-iu. При этом ( К-1), следовательно второй разряд блока 5 должен быть отключен, а второй разряд блока 6 остаться включенным на весь период процесса приближения. В третьем тактовом интервале подключаются младшие разряды обоих блоков 5 и 6 и напряжения U, соответственно равны н- сГи И й-Дд-Л-. u|Ue2-U, ..и «и и|--5|&-(-4|д)--ид. При, этом ( h После, получения результата сравнения компаратора 2 младший разряд блока 5 остается включенным, а блока- 6 - выключается и напряжения О соответственно равны 1 ис - э1 Ь-4л-Д -э|л.,i-U j-fK-26--3 ui (-з|А)4лПри этом ). Этот последний этап процесса последовательного приближения необходим для получения шага квантования устройства равиогоД. Процесс уравновешивания заканчивается выходной код, полученный в соответствии с алгоритмом, соответствует двоичному числу 1011. Кодирование отрицательных выборок входного сигнала происходит ана- логичным образом, а выходной код образуется с помощью соответствующих узлов блока 7.

Формула изобретения

Кодирующее устройство последовательного приближения, содержащее блок ввода информации, первый выход которого соединен с первым входом компаратора, выходом первого блока эталонов, анодом первого и катодом второго диодов, второй выход - с вторым входом компаратора, выходом второго блока эталонов, катодом первого и анодом второго диодов, выход компаратора соединен с первым входом блока управления, первый и второй выходы которого соединены с устано- вочным и управляющим входами регистра последовательных приближений, тактовый вход которого соединен с вторым входом блока управления,о т л и ч а е с я тем, что, с целью повышения точности преобразования, введен дополнительный регистр последовательных приближений, тактовый вход которого соединен с вторым входом блока управления, управляющий и установочный входы - с третьим и первым выходами блока управления, а разрядные выходы - с разряднымивходами второго 0лока эталонов, причем разрядные выходы регистра последовательных приближений соединены с разрядными входами первого блока эталонов.

Источники информации, принятые во внимание при экспертизе

1.вахтияров Г.Д. Аналого-цифровые. преобразователи, М., Сов.радио,

1980, с. 30, рис,2,

2.Анёшого-цифровое оборудование ИКМ-4Д-2. Сборник рефератов НИОКР, реферат Г ЗОЗбб, 76,А.Т. 01,13б7, серия AT, вып. 2, 1976, с. 10 (прототип)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1358094A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1562971A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Многоканальный преобразователь угол-код | 1983 |

|

SU1117304A1 |

| Устройство для извлечения квадратного корня из напряжения | 1989 |

|

SU1721615A1 |

| Способ многоканального аналого-цифрового преобразования сигналов и устройство для его осуществления | 1986 |

|

SU1411972A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

W

ff

ftao3 19

W

164

If

Авторы

Даты

1982-10-15—Публикация

1980-06-27—Подача