1

Изобретение относится к запоминающим устройствам и может .быть использовано для функционального контроля как отдельных корпусов микросхем, оперативных запоминающих устройств (ОЗУ), так и построенных на их основе массивов полупроводниковых ОЗУ произвольной емкости и организации.

Известны устройства для контроля полупроводниковой памяти С 3

Одни из известных устройств основаны на использовании ЭВМ или контроллеров на базе ЭВМ для хранения программ входных воздействий тестовых процедур микросхем ОЗУ, а также для реализации процесса контроля выходных реакций тестируемых микросхем ОЗУ D.

Недостатками этих устройств являются их громоздкость и сложность при проведении функционального контроля каким-либо методом. Кроме того, недостатком является неполнота тестирования, так как контроль микросхем ocyj :

ществляеТся только по считываемой информации, остальные состояния таблицы истинности не учитываются.

Наиболее близким техническим решением к изобретению является устройство для контроля полупроводниковюй памяти, содерж1аи(ее генератор тактовых импульсов, генератор тестовых импульсов, блок формирования временной диаграммы, компаратор, мультиплексор, накопители и блок управления f2j.

Недостатками этого устройства являются большие аппаратурные затраты и невысокое быстродействие, объясняющееся тем, что для локализации неисправностей требуется значительное время.

Целью изобретения является повыше ние быстродействия и упрощение устройства.

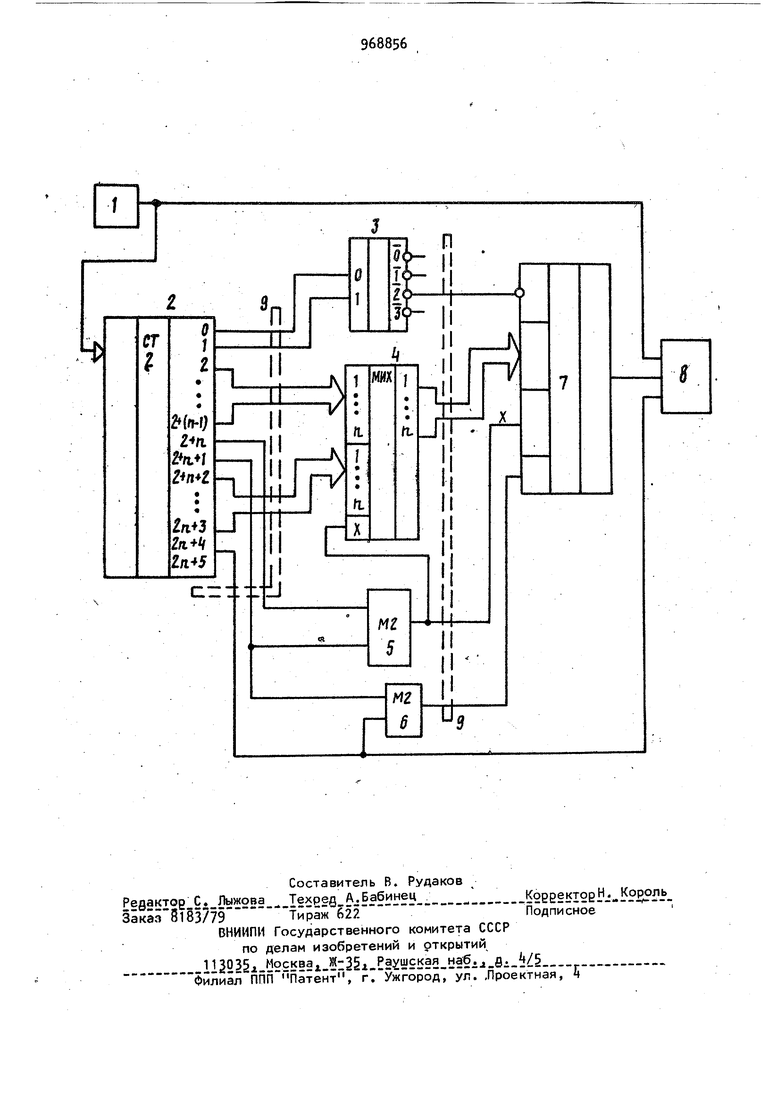

Поставленная цель достигается тем, что в устройство для контроля полупроводниковой памяти, содержащее генератор синхросигналов, выход которого подключен к первому входу анализатора сигналов, втррой вход которого являет ся входом устройства, мультиплексор, выход которого является одним из выходов устройства, введены дешифратор сумматоры по модулю два и счетчик, вход которого подключен к выходу гене ратора синхросигналов, а выходы соединены соответственно со входами дешифратора, одними из входов мультиплексора, входами сумматоров по модул два и третьим входом анализатора сигн лов, выход одного из сумматоров по модулю два соединен с другим входом мультиплексора, один из выходов дешифратора и выходы сумматоров по модулю два являются другими выходами устройства. На чертеже изображена функциональная схема устройства для контроля полупроводниковой памяти. Устройство содержит генератор 1 синхросигналов, двоичный счетчик 2 с количеством разрядов .кн-6 ( где И количество адресных входов контролируемого ОЗУ), дешифратор 3 (2. -), мультиплексор 4 (2 И - vi), сумматоры 5 и 6 по модулю два. Входы и выходы устройства подключаются к блоку контролируемой полупроводниковой па-° мяти 7 СВИС ОЗУ). В качестве анализатора 8 сигналов в устройстве используется сигнатурный анализатор 3 3Конструктивно устройство выпoJ нeно так, что блок 7 соединяется с остальными элементами устройства и анализатором 8 с помощью интерфейсной коммутационной матрицы 9, различной для различных цоколевок корпусов (показанной пунктиром). Устройство работает следующим образом. Генератор 1 синхросигналов запуска ет счетчик 2, который, работая в режи ме непрерывного пересчёта, с помощью выходов разрядов О . и 1 и дешифратора 3 вырабатывает следующие друг за другом сигналы дешифрируемых статусов О, 1, 2 и 3 длительноетью каждый по такту (периоду ) синхросигнала и имеющие активным нулевое значение. Один из этих сигналов - ста тус 2 используется в качестве сигна ла разрешения выборки тестируемого Kopпуса блока 7. Такое формирование сигнала разрешения выборки гарантирует, что его переключения имеют место внут ри сигналов чтение/запись, Входа данных и, что самое главное, - внутри пере1спючения адресов. Выходы разрядов, 2,3,... ,(и-1 - высокочастотная адресная группа - счетчика 2 подключаются соответственно к двум группам по К входов мультиплексора 4, Управляющий вход мультиплексора при своем нулевом состоянии (х 0 передает на выход, мультиплексора i, т,е. на вход тестируемого блока 7, низкочастотную адресную группу разрядов (2+И+2;, (2+ii+3h..(2n+3) счетчика 2, а при X 1 - высокочастотную адресную группу разрядов 2,3,..., (2+И-(-1) счетчика 2. При х О имеет место команда Запись информации, а при X 1 - команда Чтение, которые производятся при подаче через мультиплексор на адресные входы блока 7 высокочастотной адресной группы, т.е, чтение всегда производится по всему лолю адресов, перебираемых высокочастотной адресной группой, а запись производится по адресу, заданному низкочастотной адресной группой, которая сдвигает записываемую информацию по медленно перебираемым адресам, и после записи в каждый адрес происходит переключение на задание адресов высокочастотной адресной группой, когда производится считывание информации по всему полю блока 7. Стимуляция сигнала запись/чтение .производится разрядом 2+и, следующим за старшим разрядом 2+И-1 высокочастотной адресной группы счетчика 2. Этот сигнал логически объединяется сумматором по модулю два 5 со следующим (2+УН-1)-ым разрядом счетчика 2, что обеспечивает формирование последовательности команд вида Запись, Чтение, Чтение, Запись, т.е. выход разряда 2-«-и счетчика 2 с изменением фазы в середине с помощью сумматора по модулю два 5, на один вход которого подан разряд 2+и счетчика 2, а на второй вход - следующий разряд (2+уг+11 счетчика 2, являющийся одноВременно стимулятором входа данных тестируемого блока 7. Во время теста, например сдвига нуля на фоне единиц, происходит обязательное восстановление фона после теста каждой ячейки. Так что после Первой половины общего теста, т.е. теста сдвига нуля в поле тестируемого блока 7 будет исходный фон единиц, который должен быть заменен полностью на фон нулей для реализации во время второй половины общего теста, теста сдвига единиц на фоне нулей. Для этого сумматор по модулю два 6 меняет фазу стимуляции сигнала входа данных тестируемого бло ка 7, поскольку на один вход сумматора по модулю два 6 подан разряд (2-ни-О стимуляции входа данных, а на второй вход - выход последнего исполь зуемого разряда (.) счетчика 2. Таким образом, D первой четверти общего времени теста происходит заполнение поля тестируемого блока 7 фо ном единиц, во второй четверти - тест сдвиг нуля на фоне единиц и восстанов ление фона единиц после теста каждой ячейки. В третьей четверти имеет место заполнение поля тестируемого блока 7 фоном нулей, в четвертой четверти .- тест сдвиг единицы на фоне нулей и восстановление фона нулей после теста каждой ячейки, что и реализует общую концепцию теста сдвига информации на инверсном фоне. Выход тестируемого блока 7 подается на информацион ный вход используемого в качестве ана лизатора сигналов сигнатурного анализатора 8,. вход старт/стоп которого управляется от последнего используемо го разряда счетчика 2, а синхровход получает сигналы синхронизации от ге нератора 1 синхросигналов. Использование сигнатурного анализатора 8 обес печивает возможность контроля выходны реакций тестируемого блока 7 не только во время считывания, но,что особен но существенно, контроля выходных реакций при всех возможных состояниях таблиц истинности тестируемого блока а именно: при запрете чтения, при запрете записи, при разрешении записи, Это обусловлено,тем, что прием вУхадHbtx реакций в сигнатурный анализатор производится по каждому без исключения синхросигналу генератора 1, Поэтому за время каждого адреса будет принята с опредленной избыточностью выходная реакция при запрете записи. 968 6 при разрешении записи, при запрете чтения и при разрешении чтения. Имеющая место избыточность особого значения не имеет в связи с применением сигнатурного анализа, обеспечивающего сжатие двоичной информации произвольной длины в короткую сигнатуру с .ведьма высокой достоверностью. Время тестирования предложенным устройством достаточно мало по сравнению со временем, реализуемым известным устройством. Формула изобретения Устройство для контроля полупроводниковой памяти, содержащее генератор синхросигналов, выход которого подключен к первому входу анализатора, сигналов, второй вход которого является входом устройства, мультиплексор, выход которого является одним из выходов устройства, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, в него введены дешифратор, сумматоры по модулю два и счетчик, вход которого подключен к выходу генератора синхросигналов, а выходы соединены соответственно со входами дешифратора, одними из входов мультиплексора, входами сумматоров по модулю два и третьим входом анализатора сигналов, выхоД одногоиз сумматоров по модулю два соединен с другим входом мультиплексора, один из выходов дешифратора и выходы сумматоров по модулю два являются другими выходами устройства. Источники информации принятые во внимание при экспертизе 1. Электронная промышленность, 1977, К 2, с. 20-24. 2.Авторское свидетельство СССР М 771730, кл..Г, 11 С 29/00, 1973 (прототип). 3. Электроника, 1977, № 5, с. 71.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1032481A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1053164A1 |

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1070607A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1140179A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1053165A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1982 |

|

SU1051586A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

Авторы

Даты

1982-10-23—Публикация

1981-01-30—Подача