Изобретение относится к запоминающим устройствам и может быть применено для контроля блоков постоянной памяти.

Известно устройство для контроля блоков памяти, в котором при записи (считывании) информации в оперативное запоминающее устройство формируется контрольный разряд, равный сумме контрольных разрядов адреса и слова, что позволяет обнаружить чтение по неправильному адресу, а также искажение информации 1}.

Недостатком этого устройства является его сложность. Наие5олее близким техническим решением к изобретению является устройствсГ для контроля блоков памяти, содержащее формирователь сигналов регенерации, регистра адреса, блок управления, блок местного управления, триггер, формирователь сигналов записи и считывания, формирователь тестовых сигналов, схему сравнения, регистр числа, блок- останова, элементы И, элемент НЕ и коммутатор С2 J.

Недостатком этого устройства является -низкая точность контроля ад1ресной части постоянных запоминаю;Ших устройств.

Цель изобретения - повышение точ.ности контроля устройства.

Поставленная цель достигается тем, что в устройство для контроля блоков памяти, содержапюе генератор тактовых импульсов, выход которого подключен к первому входу первого элемента И, первый триггер, блок установки эталонов, выход которого сое10динен с первым входом схемы сравнения, и формирователи импульсов, выходы Которых являются управляющими выходами устройства, введены счетчики, второй триггер, блок контроля

15 четности, блоки свертки адреса, вто.рой и третий элементы И, причем вхо ды первого счетчика подключены к вы1ХОДУ первого элемента И и входам формирователей импульсов, выходы пер20вого счетчика подключены к входам первого блрка свертки адреса и являются адресными выходами устройства, информационными входами которого являются одни из входов блока контроля

25 четности, другой вход которого является контрольным входом устройства и соединен с одним из входов второго ;блока свертки адреса, другой вход которого подключен к выходу первого

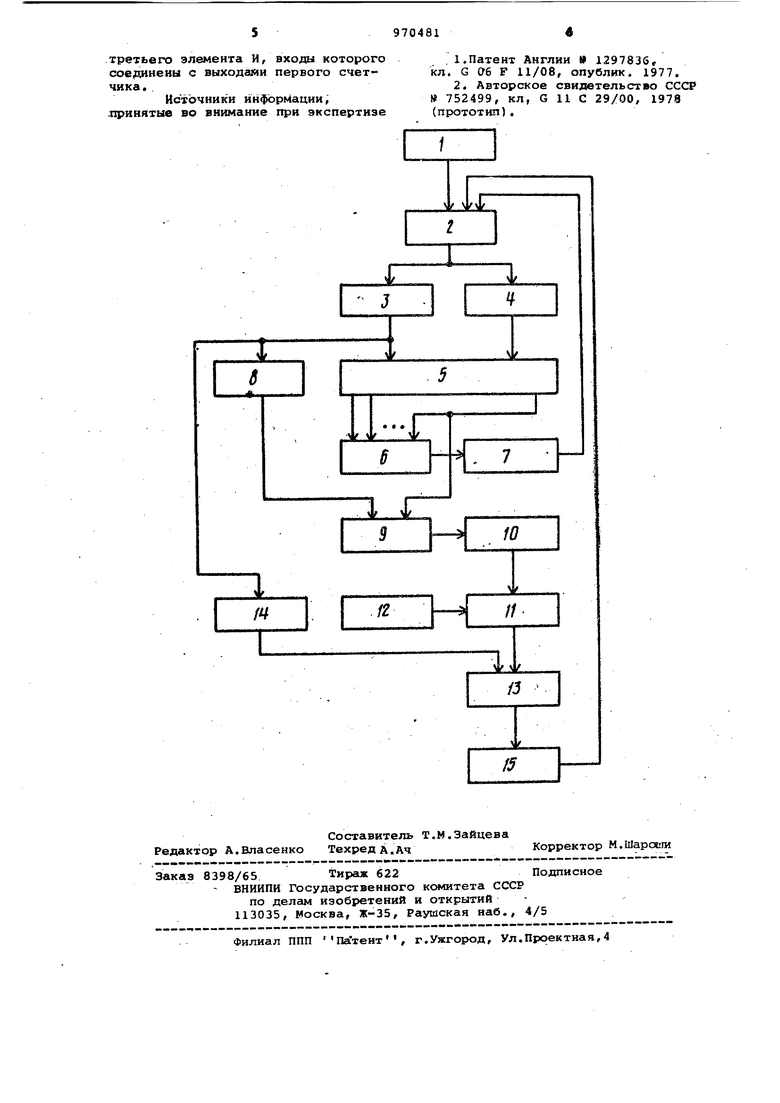

30 блока свертки адреса, а выход - к входу второго счетчика, выход которо го соединен с вторым входом схемы сравнения, выход блока контроля чет ности подключен к входу первого триг гера, нулевой выход которого соединен с вторым входом первого элемента И, третий вход которого подключен к нулевому выходу второго триггера, вход которого соединен с выходом вто рого элемента И, входы которого подключены соответственно к выходу схемы сравнения и к выходу третьего эле мента И, входы которого соединены с выходами первого счетчика. На чертеже представлена функцио(нальная схема предлагаемого устройст ва. Устройство содержит генератор так товых импульсов, первый элемент И 2, первый счетчик 3, формирователи 4 импульсов, проверяемый блок 5 памяти Устройство содержит также блок 6 контроля четности, первый триггер 7, первый 8 и второй 9 блоки свертки адреса, второй счетчик 10, схему 11 сравнения, .блок 12 установки эталонов, второй 13 и третий 14 элементы И и второй триггер 15. Устройство работает следующим об|разом. Производится пуск генератора 1 (цепи пуска и начального сброса условно непоказанн) ,и импульсчерез эле мент И 2 jiocTynaeT на входы счетчика Зи формирователей 4, которые формируют по амплитуде и длительности необходимые сигналы управления (обращение, чтение и т.п.) Считанная информация с проверяемого блока 5 контролируется на четность блоком 6, При нечетной информации триггер 7 устанавливается в , и О с нулевого выхода триггера 7 постуйает на второй вход элемента И 2, при этом происходит останов. Счетчик 3 указывает адрес сбоя. Контрольный разряд, т.е. раэряд, дополняющий до четности информацию в блоке 5, поступает на один из входов блока 9, на другой вход которого с выхода блока 8 поступает контрольный разряд адреса, и на выходе блока 9 формируется комбинированный контрольный разряд. Счетчик 10. ,подсчйтШаёт; число единиц комбинированного контрольного разря|да по всему массиву инфор лации блока 5 памяти. Это число сравнивается схе мой 11 сравнения с эталоном, установ ленным на блоке 12. Эталон для каждого блока 5 памяти определяется на этапе записи информации в него и представляет собой константу, которую и устанавливают вручную в блоке 12. При считывании информации по последнему адресу из блока 5 на выходе многовходового элемента И 14 появляется рая попадается на первый вход элемента И 13, Если значение счетчика 10 равно эталону, установленному в блоке 12, то на выходе схемы 11 сравнения будет сигнал О и триггер 15 не ,установится в , т.е. сбоя нет. В противном случае сигнал О с нулевого выхода триггера 15 поступает на третий вход элемента И 2 и проис ходит -ocjaHOB, .устройства по неисправности адресной части проверяемого блока. Таким образом, устройства выполняет контроль блока 5 памяти при считывании из него информации на его рабочей частоте в динамическом режиме, что повышает точность контроля. Устройство особо эффективно при контроле блоков постоянной пгьмяти, контроль адресной части которых в динамическом режиме на рабочей частоте проверяемого блока представляет значительные трудности. Формула изобретения Устройство для контроля блоков памяти, содержащее генератор тактовых импульсов, выход которого подключен к первому входу первого элемента И, первый триггер, блок установки эталонов, выход которого соединен с первым входом схемы сравнения, и формирователи импульсов, выходы которых являются управляющими выходами устройства, отличающееся тем, что, с целью повышения точности контроля, в него введены- счетчики, второй триггер, блок контроля четности, блоки свертки адраса, второй и третий элементы И, причем ВХОДЫпервого счетчика подключены к выходу первого элемента И и входам 5 формирователей импульсов, выходы первого счетчика подключены к входам первого блока свертки адреса и являются адресными выходами устройства, информационными входами которого являются одни из входов блока контроля четности, другой вход которого является контрольным входом устройства и соединен с одним из входов второго блока свертки адреса, другой вход которого подключен к выходу первого блока свертки адреса, а выход - к входу второго счетчика, выкод которого соединен с вторым входом схемы сравнения, выход блока контроля четности подключен к входу первого триггера, нулевой выход которого соединен с вторая входом первого элемента И, третий вход которого подключен к нулевому выходу второго триггера, вход которого соединен с выходом второго элемента И, входы которого подключены соответственно к .выходу схемы сравнения и к выходу

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1310904A1 |

| Устройство для контроля блоков памяти | 1984 |

|

SU1226533A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для контроля блоковОпЕРАТиВНОй пАМяТи | 1979 |

|

SU832603A1 |

| Устройство для разбраковки и контроля микросхем постоянной памяти | 1985 |

|

SU1336121A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

Авторы

Даты

1982-10-30—Публикация

1981-04-15—Подача