1

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных и многоканальных системах переработки информации и управления с общей память

Цель изобретения - повышение быстродействия устройства.

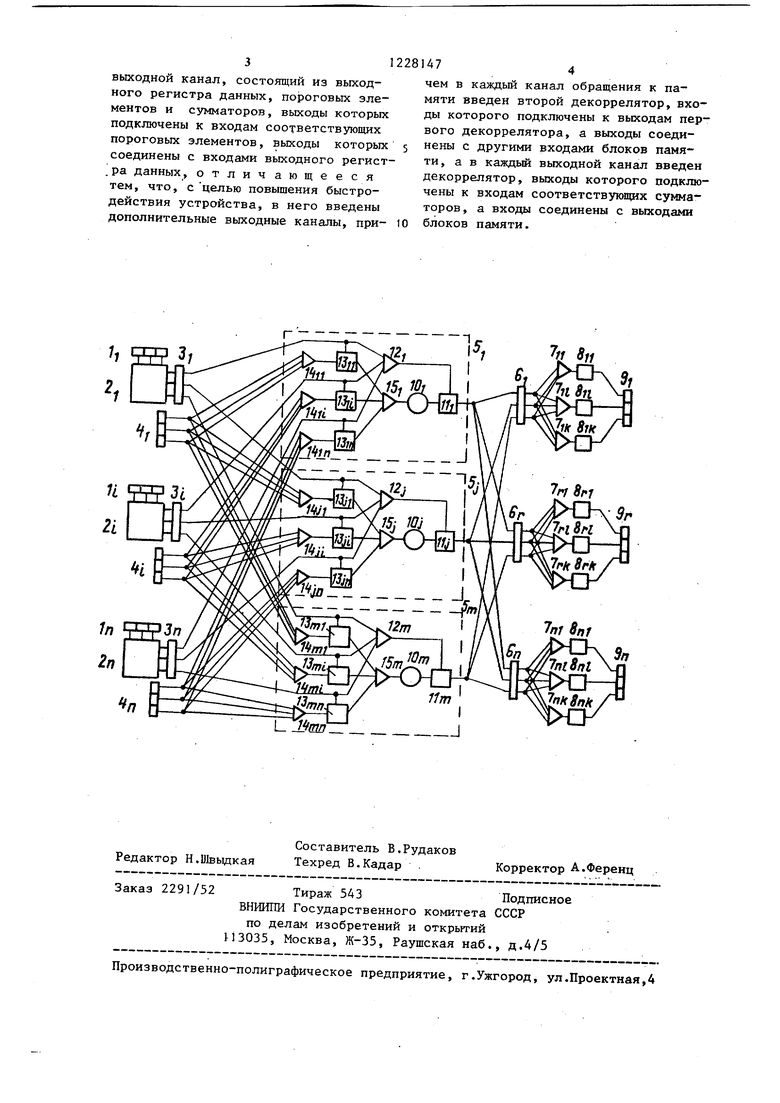

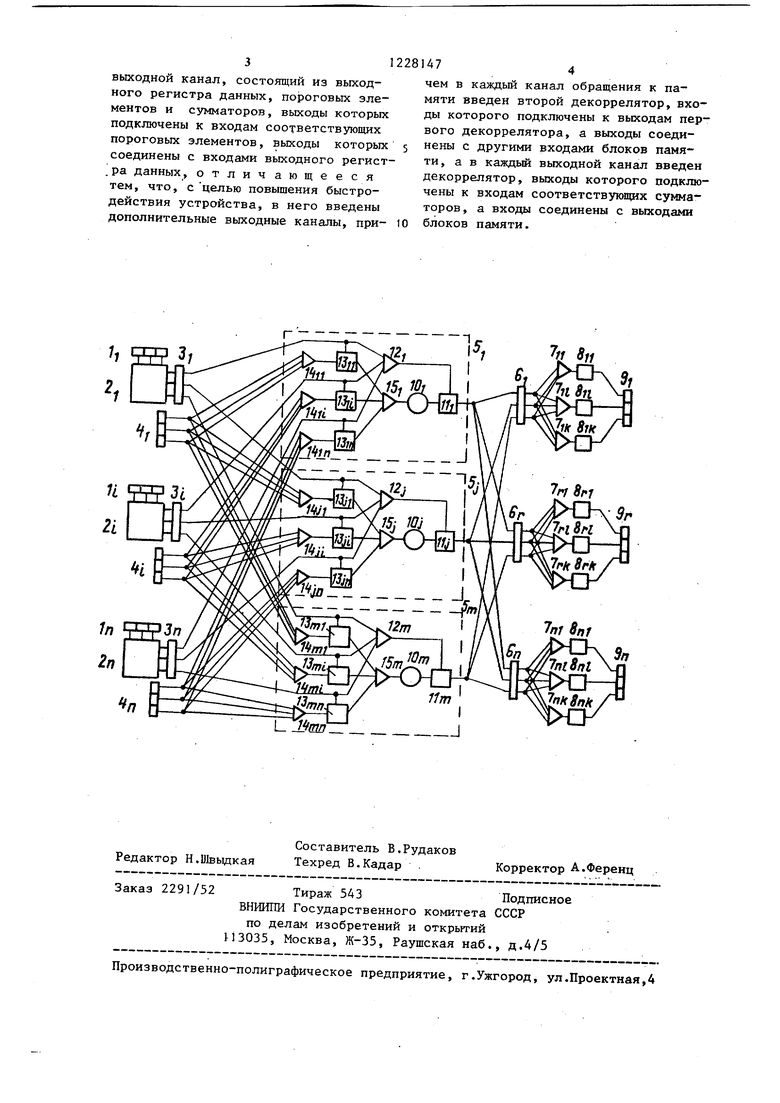

На чертеже изображена структурная схема многоканального запоминающего устройства.

Многоканальное запоминающее устройство содержит п каналов обращения к памяти, каждый из которых состоит из регистра, адреса, первого декор- релятора 2, рторого декоррелятора 3 (являющегося управляемым декоррёлято ром) и входного регистра 4 данных, m блоков памяти, и п выходных каналов, каждый из которых состоит из декоррелятора 6 (являющегося неуправ ляемым декоррелятором) ,К сумматоров (где К - разрядность запоминающих чисел), К пороговых элементов 8 и выходного регистра 9 данных.

Каждый из блоков 5 памяти содержи многоуровневый элемент 10 памяти, выходной умножитель 11, сумматор 12, п входных умножителей 13 и п сумматор 14, 15.

Устройство работает следующим образом.

При записи на все регистры 1 , где i 1, п, подаются адресные коды, а на регистры 4 - информационные коды. На декорреляторы 3 по- дают двоичные сигналы управления, под воздействием которых они приходят в одно из двух состояний Декор- реляционное преобразование включено

или Декорреляционное преобразова- ние выключено, т.е. в состояния Включено или Выключено. В состояние Включено декоррелятор 3; переводится в том случае, когда записью аемая информация предназначена для использования только в данном i-OM канале (процессы не показаны ) или только i-M процессом. В состояние Выключено декоррелятор 3, переводится в том случае, когда запи- сывается информация предназначена для обмена между каналами (или между процессорами).

Декоррелятор 3; в состоянии Включено псевдослучайно преобразо- вывает набор сигналов, поступающих с выходов декоррелятора 2{ в новый набор, так что оба набора являются

5

О

5 0

5

5

0

некоррелированными. Декорреляторы 3,, входящие в состав разных каналов, осуществляют независимые преобразования сигналов. Сумматоры , (где j 1,m) блоков 5 памяти формируют взвешенные суммы сигналов, поступающих с выходов регистров 4./. Во входных умножителях 13 .- эти суммы умножаются на ключевые сиг- налы, поступающие с выходов декорре- ляторов 3- (отдельно для каждого канала).

Выходные сигналы входных умножителей 13jj суммируются сумматорами 15j, и суммарные сигналы запоминаются в элементах 10: памяти.

4

При считывании на регистры Ij подают адресные коды. Декоррелятор 3-, устанавливают в состояние Выключено, если необходимо считьшать информацию, относящуюся только к данному каналу, и в состояние Включено, если необходимо считьгоать информацию, поступившую на запись из другого канала и предназначенную для обмена между каналами. Сигналы с выходов декорреляторов 3j через сумматоры 12 попадают на одни из входов выходных умножителей 1Ij, на другие входы которых поступают сигналы из элементов 10; памяти. Сигнал с выхода умножителя llj поступает на i-e входы всех декорреляторов 6р (где г 1,К). Преобразование, осуществляемое декоррелятором 6|,, является обратным по отнощению

к преобразованию, осуществляемому декоррелятором 3,, (т.е примененные последовательно, они переводят набор сигналов в исходный).

Сумматоры 7р формируют взвешенные суммы сигналов с выходов декорреляторов 6. После преобразования этих сигналов в пороговых элементах 8 в регистрах 9р образуются считанные коды. )

Формула изобретения

Многоканальное запоминающее устройство, содержащее блоки памяти, каналы обращения к памяти, каждый из которых состоит из первого декоррелятора, входного регистра данных, выходы которого подключены к одним из входов блоков памяти, и регистра адреса, выходы которого подключены к входам первого декоррелятора, и

31

выходной канал, состоящий из выходного регистра данных, пороговьпс элементов и сумматоров, выходы которых подключены к входам соответствующих пороговых элементов, выходы которых соединены с входами выходного регист- .ра данных, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены дополнительные выходные каналы, при1474

чем в каждый канал обращения к памяти введен второй декоррелятор, входы которого подключены к выходам первого декоррелятора, а выходы соеди- нены с другими входами блоков памяти, а в каждьй выходной канал введен декоррелятор, выходы которого подключены к входам соответствующих сумматоров, а входы соединены с выходами

блоков памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1981 |

|

SU972593A1 |

| Многоканальный демодулятор дискретных сигналов | 1986 |

|

SU1327317A1 |

| Преобразователь активной мощности в цифровой код | 1986 |

|

SU1366960A1 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

| МНОГОКАНАЛЬНОЕ АДАПТИВНОЕ РАДИОПРИЕМНОЕ УСТРОЙСТВО | 2011 |

|

RU2450422C1 |

| Устройство для формирования базисно-тригонометрических функций | 1990 |

|

SU1792542A3 |

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| Многоканальное устройство для ввода информации | 1989 |

|

SU1633383A1 |

| Устройство коммутации дискретных каналов с временным разделением | 1989 |

|

SU1663785A1 |

| Многоканальный систолический процессор для вычисления полиномиальных функций | 2020 |

|

RU2737236C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах переработки информации и системах управления технологическими процессами. Цель изобрете ния повышение быстродействия уст- ройства. Введение в каждый канал обращения к памяти второго декорреля- тора и подключение его к входам блоков памяти, а также введение. дополнительных выходных каналов, идентичных основному, и включение в каждый выходной канал третьего декоррелято- ра позволяет осуществлять.одновременную запись по нескольким каналам в одну и ту же область памяти и одновременное считывание по нескольким каналам из одной и той же области памяти в многоканальных и многопродес- сорных системах. 1 ил. € (Л ю Nd 00 4

/, ВДР 3,

«/7

Редактор Н.иЬыдкая

Составитель В.Рудаков Техред В.Кадар

Заказ 2291/52 Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открьргий И3035, Москва, Ж-35, Раущская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор А.Ференц

| Мультипроцессорные вычислительные системы,/ Под ред | |||

| Я.А.Хетагуро- ва | |||

| М.: Энергия, 1971, с. | |||

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| Запоминающее устройство | 1981 |

|

SU972593A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-04-30—Публикация

1984-04-02—Подача