(5) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с само-КОНТРОлЕМ | 1979 |

|

SU809362A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1164790A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1522292A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU879655A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1104588A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1108511A1 |

| Устройство для контроля записи информации в блоках памяти | 1976 |

|

SU723675A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875474A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

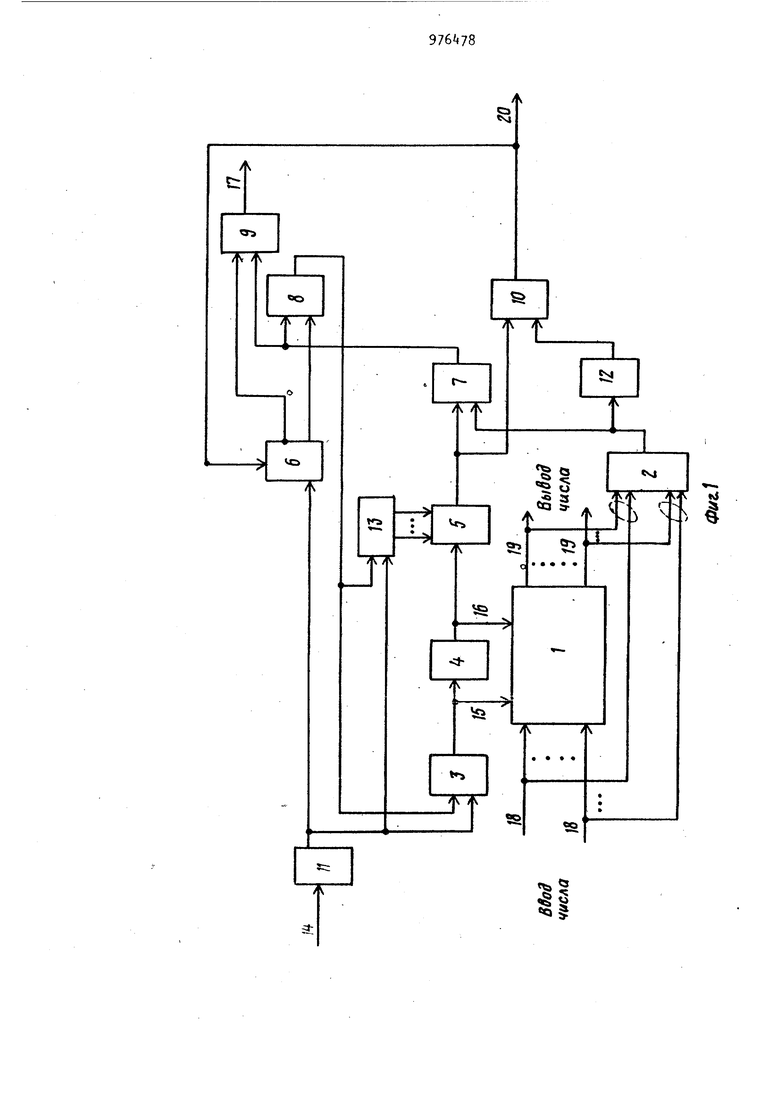

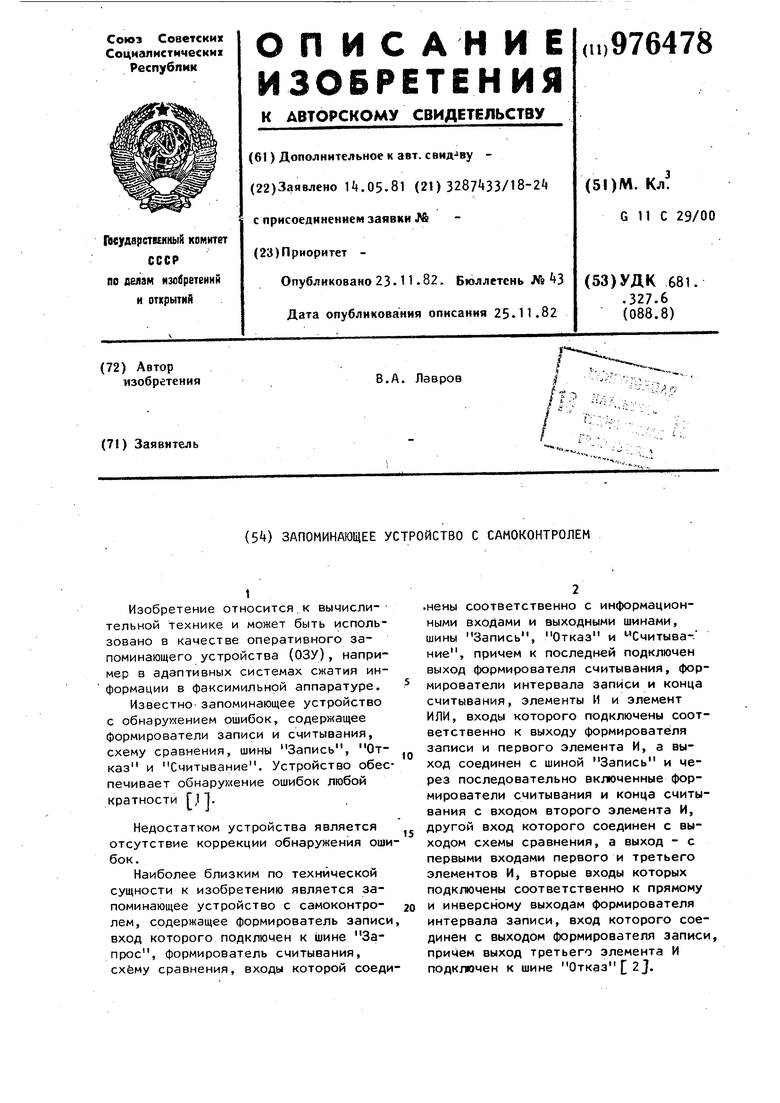

Изобретение относится.к вычислительной технике и может быть использовано в качестве оперативного запоминающего устройства (ОЗУ), например в адаптивных системах сжатия информации в факсимильной аппаратуре. Известно запоминающее устройство с обнару иением ошибок, содержащее формирователи записи и считывания, схему сравнения, шины Запись, Отказ и Считывание. Устройство обес печивает обнаружение ошибок любой кратности Г11. Недостатком устройства является отсутствие коррекции обнаружения оши бок. Наиболее близким по технической сущности к изобретению является запоминающее устройство с самоконтролем, содержащее формирователь записи вход которого подключен к Шине Запрос, формирователь считывания, схему сравнения, входы которой соеди .нены соответственно с информационными входами и выходными шинами, шины Запись, Отказ и -Считыва-. ние, причем к последней подключен выход формирователя считывания, формирователи интервала записи и конца считывания, элементы И и элемент ИЛИ, входы которого подключены соответственно к выходу формирователя записи и первого элемента И, а выход соединен с шиной Запись и через последовательно включенные формирователи считывания и конца считывания с входом второго элемента И, другой вход которого соединен с выходом схемы сравнения, а выход - с первыми входами первого и третьего элементов И, вторые входы которых подключены соответственно к прямому и инверсному выходам формирователя интервала записи, вход которого соединен с выходом формирователя записи, причем выход третьего элемента И подключен к шине Отказ 2 J. Недостатком данного устройства является его невысокое быстродействие, так как устройство при отсутствии ошибок записи не прекращает формирование интервала контроля записи числа, что увеличивает время записи числа. Кроме того, коррекция ошибок записи в процессе контроля недостаточно эффективна, так как она производится без изменения параметров импульсов записи. Цель изобретения - повышение быст родействия устройства. Поставленная цель достигается тем что в запоминающее устройство с самоконтролем, содержащее накопитель, информационные входы которого подключены к одним из входов схемы срав нения и являются информационными вхо дами устройства, выходы накопителя подключены к другим входам схемы сравнения и являются информационными выходами устройства, первый управляющий вход накопителя подключен к выходу элемента ИЛИ и к входу первог формирователя сигналов, выход которо го подключен к второму управляющему входу накопителя и к одному из входов второго формирователя сигналов, выход второго формирователя сигналов подключен к первому входу первого эл мента И, второй вход которого подклю чен к выходу схемы сравнения, первый вход элемента ИЛИ является управляющим входом устройства и подключен к первому входу третьего формирователя сигналов, первый и второй выходы которого подключены к первым входам соответственно второго и третьего элементов И, вторые входы второго и третьего элементов И подключены к выходу первого элемента И, дополнительно введены четвертый элемент И, элемент НЕ и счетчик импульсов, первый вход которого подключен к выходу второго элемента И, второй вход к первому входу элемента ИЛИ, выходы счетчика импульсов подключены к другим входам второго формирователя си| налов, первый и второй входы четвертого элемента И подключены соответственно к выходу второго формирователя сигналов и к выходу элемента НЕ вход которого подключен к выходу схе мы сравнения, выход четвертого элемента И, подключен ко второму входу третьего формирователя сигналов и является управляющим выходом устройства. На фиг, 1 изображена блок-схема запоминающего устройства с самоконтролем; на фиг. 2 - временная диаграмма работы устройства (а - при отсутствии сбоя; б - при двухкратном сбое в пределах интервала контроля записи; в - при многократном сбое, который появляется и после окончания интервала контроля записи, что приводит к формированию сигнала Отказ) Изобретение содержит накопитель 1, схему 2 сравнения, элемент 3 ИЛИ, формирователь k сигналов, формирователь 5 сигналов (в предложенном устройстве формирователь 5 выполнен с электронным управлением настройкой длительности формируемого сигнала), формирователь 6 сигналов,.элемент И. , формирователь 11 сигналов, элемент НЕ 12, счетчик 13, шины Запрос 1, Запись 15, Считывание 16, Отказ 17, Ввод числа 18, Вывод числа 19 и выход 20, Информация, подлежащая записи, поступает на шины Ввод числа 18, откуда она подается на вход оперативного накопителя и на первые входы схемы 2, Считанная информация с выходов накопителя 1 подается на шину Вывод числа 19 и на вторые входы схемы 2. При этом разрешение на запись чисел в накопитель 1 формируется по сигналам на шине Запрос 14, поступающим с рассчитанным на определенное количество сбоев максимально допустимым периодом следования. При уменьшении количества сбоев или их отсутствии период следования этих сигналов может уменьшаться до минимально допустимой величины, задаваемой быстродействием накопитеУстройство работает cлeдyюJмим образом. При подаче сигнала на шину Запрос 1А запускается формирователь 11, формирующий сигнал записи с его выхода по переднему фронту входного сигнала, сбрасывается счетчик 13 и запускается формирователь 6, длительность импульса которого определяет число возможных циклов записи и контроля (при условии постоянного появления сигнала Сбой на выходе схемы 2). Кроме того, импульс с фор5мирователя 11 поступает на первый вход элемента ИЛИ 3, на выходе которого формируется импульс Запись, который поступает на шину Запись 15, а также запускает формирователь Ц.I После записи числа, поступающего на вход накопителя 1 по шинам Ввод числа 18, на выходе формирователя после окончания импульса Запись формируется импульс Считывание, Этот импульс поступает на шину Считывание 16 и на вход формирователя 5 формирующего сигнал конца считывания. При этом на входах схемы 2 производится сравнение чисел с шины Ввод числа. 18 и Вывод числа 19 и информация поступает на выход схемы 2 сравнения. Если после первого и любого очередного цикла записи и сравнения на выходе схемы 2 не появится сигнал Сбой, то на входах элемента И 10 импульс Конец считывания, сформированный по заднему фронту импульса Считывание с выхода формирователя 5, совпадает с импульсом на выходе элемента НЕ 12 и на выходе 20 по явится сигнал Отсутствие сбоя (фиг. 2а). По этому сигналу формирователем 6 останавливается формирование интервала записи, а по выходу 20 сменяется число на шинах Ввод числа 18, на шину Запрос Н поступае второй сигнал Запрос и производитс запись и контроль записи нового числа. Таким образом, при отсутствии сиг нала Сбой уменьшается интервал меж ду импульсами Запрос, т.е. уменьша ется интервал контроля записи, что увеличивает быстродействие устройства. В случае несоответствия чисел на шинах Ввод числа 18 и Вывод числа 19 на выходе схемы 2 появится сигнал Сбой. Этот сигнал поступает на вто рой вход элемента И 7, на первый вхо которого поступит импульс Конец счи тывания. После совпадения на входах элемента И 7 импульс поступает на первые входы элементов И 8 и Э, на вторые входы которых подаются сигналы с прямого и инверсного выходов формирователя 6. С выхода элемента И 8 импульс поступает на второй вход элемента ИЛИ 3 и по шине 15 начина8этого же числа запись ется повторная в накопитель. Импульсы с элемента И 8, сформированные после каждого контрольного считывания при наличии сигнала Сбой на схеме 2 запускают также счетчик 13, сигналы с соответствующих выходов которого изменяют длительность импульса повторной записи и считывания путем управления формирователем 5Изменение длительности импульса контрольной записи дает возможность . повысить эффективность коррекции Сбой по отношению к минимально допустимым длительностям импульсов записи и считывания. Если сигнал Сбой возникнет при каждом контрольном считывании, то после окончания интервала контроля записи с формирователя 6 подается разрешающий потенциал на второй вход элемента И 9, на выходе которого сформируется сигнал Отказ. Предлагаемое запоминающее устройство выгодно отличается от известного тем, что имеет более высокое быстродействие за счет уменьшения, времени на формирование интервала контроля записи при отсутствии ошибок и позволяет повысить эффективность коррекции ошибок при контроле путем изменения параметров импуяь.сов записи. Формула изобретения Запоминающее устройство с самоконтролем, содержащее накопитель, информационные входы которого подключены к одним из входов схемы сравнения и являются информационными входами устройства, выходы накопителя подключены к другим входам схемы сравнения и являются информационными выодами устройства, первый управляюий вход накопителя подключен к выоду элемента ИЛИ и к входу первого формирователя сигналов, выход которого подключен к второму управляюему входу накопителя и к одному из ходов второго формирователя сигнаов, выход второго формирователя си1- алов подключен к первому входу перого элемента И, второй вход котороо подключен к выходу схемы сравнеия, первый вход элемента ИЛИ является управляющим входом устройства и подключен к первому входу третьего формирователя сигналов, первый и второй выходы которого подключены к первым входам соответственно второго и третьего элементов И,,вторые входы второго и третьего элементов И подключены к выходу первого элемента И,отличающееся тем, что, с целью повышения быстродейст-: ВИЯ устройства, оно содержит четвертый элемент И, элемент НЕ и счетчик импульсов, первый вход которого подключен к выходу второго элемента И, второй вход - к первому входу элемента ИЛИ, выходы счетчика импульсов подключены к другим входам второго формирователя сигналов, первый и второй входы четвертого элемента И подключены соответственно к выходу второго формирователя сигналов и к выходу элемента НЕ, вход которого подключен к выходу схемы сравнения, выход четвертого элемента И подключен ко второму входу третьего формирователя сигналов и является управляющим выходом устройства. Источники информации, принятые во внимание при экспертизе

N

Авторы

Даты

1982-11-23—Публикация

1981-05-14—Подача