(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННЫХ

1

Изобретение относится к контролю за- помвнаюших устройств.

По основному авт. св. № 6О7282 ;известно устройство для контроля постоянных блоков памяти, содержащее генвратор импульсов, счетчик, элементы 2ИИЛИ, эталонный блок памяти, блок сра& нения и блок индикации, причем выход генератора подключен к входу счетчика, выходы которого подключены к входам элементов 2И-ИЛИ, выходы которых подключены к входам эталонного блока памяти, и выходам устройства, входы блока сравнения, подключены соответственно к выходу эталонного блока памяти и к входам устройства, а выходы блока сравнения подключены к входу блока индикааии Г 1 1 Так как в этом устройстве эталонный блок памяти не обладает быстродействием, равным быстродействию пров&ряемого блока памяти, это не позволяет использовать устройство для опредеБЛОКОВ ПАМЯТИ

лания области устойчивой работы постоянных блоков памяти на повышенной чао тоге обращения, а также дли контроля постоянных блоков памяти, быстродействие которых выше быстродействия эталонного блока памяти, если в качестве эталонного блока памяти применяется, например, медленно действующее оперативное запоминающее устройство.

Цель изобретения - расширение функtoциональных возможностей устройства за счет определения области устойчивой работы постоянных блоков пам5гги на повышенной частоте обращения.

,15

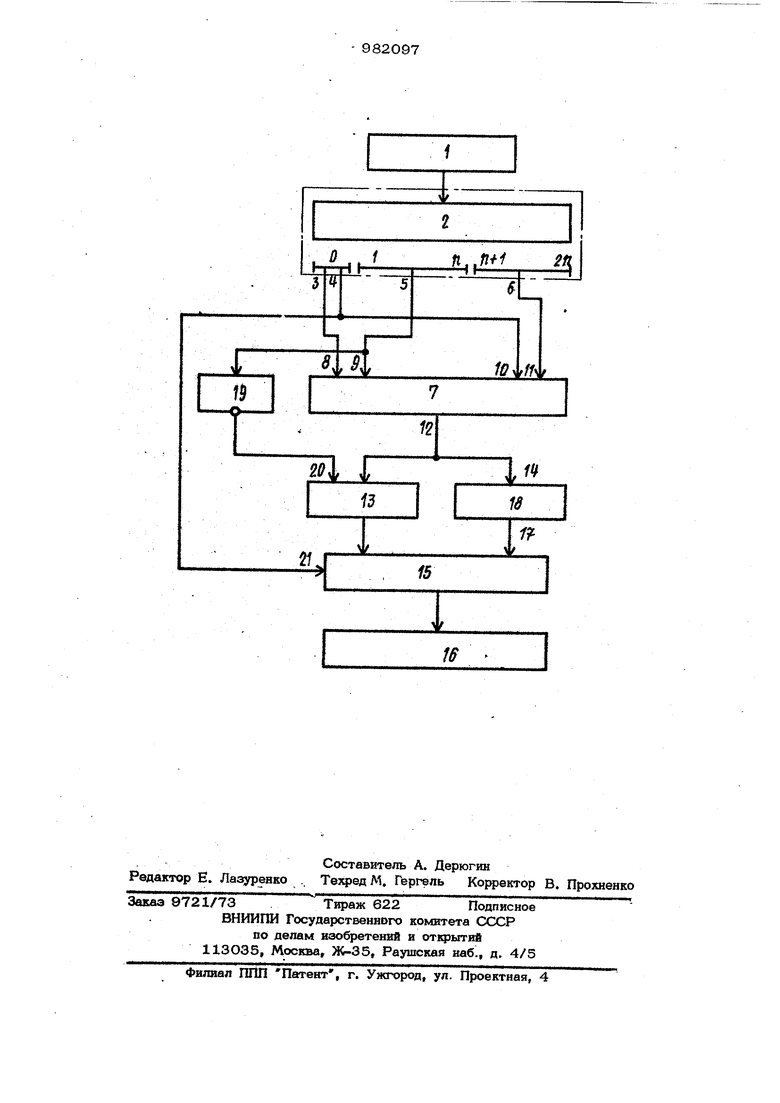

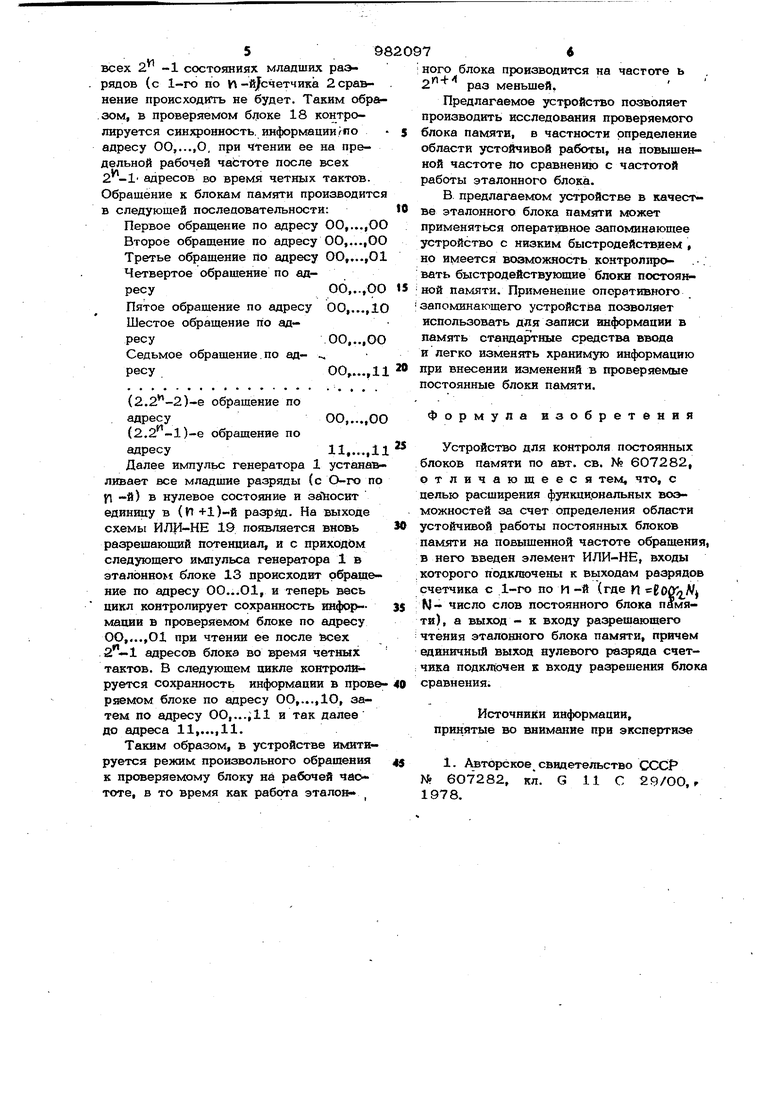

Поставленная цель достигается тем, что в устройство для контроля постоянных блоков памяти введен элемент ИЛИНЕ, входы которого подключены к выходам разрядов счетчика с 1-го по я -и

20 (где и , N .- число слов постоянного блока памяти), а выход - к входу разрешения чтения эталонного блока памяти, причем единичный выход нулевого разряда счетчика подключен к входу разрешения блока сравнения. На чертеже изображена схема предлагаемого устройства. Устройство содержит генератор 1 импульсов(2И -ь1)разрядный счетчик 2, имеющий нулевой выход 3 и единичный выход 4 нулевого разряда, выходы 5 младших разрядов (с 1-го по и -и разряд) и выходы 6 старших разрядов c(Vi+l)-ro по 2h-и разряд, элементы 2И-ИЛИ 7, имеющие входы 8-11, соединенные соответственно с выходами ,3, 5, 4 и 6 счетчика 2, и выходы 12, подключенные со®тветственно к входам эталонного блока 13 памяти и выходам 14устройства, блок 15 сравнения- и бло 16 индикации. Информационные входы блока 15 соединены с выходами блока 13 и входами 17 устройства, а его выход - с входом блока 16 индикации. К входам 17 и выходам 14; устройства подключается проверяемый блок 18 ла- мяти. Устройство содержит также схему ИЛИ-НЕ 19, И, входов которой подключены к выходам 5 счетчика 2, а выход к входу 20 разрешения чтения эталон- ного блока памяти, единичный выход 4 нулевого счетчика 2 подк/ючен к входу 21 разрешения сравнения блока 15сравнения. Устройство работает следующим обра зом. Перед началом контроля проверяемого блока. 18 производится запись информации, соответствующей проверяемому блоку, в эталонный блок 13, если в качест ве такого блока используется операт1Юное запоминающее устройство. Запись информации производится с помощью уп равляюшей ЭВМ. Она возмояша также с любого другого стандартного устройства ввода и, наконец, с аиапогупного проверяемому ПОСТОЯ1ШОГО блока памяти, пред варительно прошедшего проверку и приня того, таким образом, за эталонный. После окончания записи устройство .готово к конт5рл1о проверяемого постоян ного блока naMsiTH. Предположлм, что в рассматриваемы момейт времени счетчик 2 находится в нулевом состоянии. Тогда с выхода 3 .счётчика 2 разрешающий уровень поступает на вход 8 элементов 2И-ИЛИ 7 i а запрещающий уровень с выхода 4 счетчика 2 поступает на входы 1О элемента 2И-ИЛИ 7 и на вход 21 схемы 15 сравнения. Сигналы с выходов 5 счетчика 2. поступают на входы 9, а сигналы с выходов 6 поступают на входы 11 элементов 2И-ИЛИ 7. При этом на выходах 12 элементов 2И-ИЛИ 7 устанавливается код адреса, соответствующий выходам 5 счетчика 2, т.е. ОО,..., О. На вкопы схемы ИЛИ-НЕ 19 поступает также код 00,...,О, и с ее выхода разрешающий уровень поступает на вход 2О разрешения чтения эталонного блока. С обоих блоков 13 и 18 памяти производится считывание соответствующей этому адресу информации, которая с выхода каждого из них поступает на соответствующие входы- блока 15 сравнения. Но так как на вход 21 подается запрещающий уровень с выхода 4 счетчика 2, то сравнения в этом такге не происходит. Импульс генератора 1 меняет состояние счетчика 2 на единицу, т.е. на выходе 3 нулевого разряда счетчика 2 устанавливается запрещающий уровень, а на выходе 4 устанавливается разрешающий уровень. При этом на выходе 12 элементов 2ИИЛИ 7 устанавливается код адреса, соответствующий выходам 6 старщих разрядов счетчика 2, опять 00...,0, т.е. после обращения по нулевому адресу в первом такте. Во втором такте обращение производится опять по нулевому адресу. Вновь производится считывание с обоих блоков 13 и 18 памяти и так как на входе 21 схемы 15 сравнения разрешающий уровень, то в этом, такте происходит сравнение считанной информации. Следующий импульс генератора 1 увеличивает состояние счетчика 2 на единицу. В этом такте производится обращение по первому адресу блоков 13 -и 18. Считанная информация поступает на блок 15 сравнения, но как в первом случае сравнения не происходит, так как на выходе 21 блока 15 сравнения стоит запрещающий уровень. На входе 20 разрещения чтения с эталонного блока 13 также запрещающий уровень, который будет до тех пор, пока в младших разрядах счетчика не переберутся все возможные состояния, и они не обнулятся. В течение всего этого времени на вход блока 15 сравнения с выхода эталонного блока 13 поступает информация, соответствующая адресу ОО,...,0, и сравнение происходит только при CHitтывании из проверяемого блока памяти информации также по адресу ОО,...,0. Этот адрес определяется состоянием старших разрядов счетчика 2, т.е. при всех СОСТ05ШИЯХ младших раэ- радов (с 1-го по И-й/счетчика 2 сравнение происходить не будет. Таким обрааом в проверяемом 6jjoKe 18 контролируется син;фонность. информации ffio адресу 00,...,О, при чтении ее на предельной рабочей частоте после всех 2-1 адресов во время четных тактов. Обращение к блокам памяти производится в следующей последовательности: Первое обращение по адресу ОО,...,ОО Второе обращение по адресу ОО,...,ОО Третье обращение по адресу ОО,...,О1 Четвертое обращение по адресуОО,..,ОО Пятое обращение по адресу О0,...,10 Шестое обращение по ад- ОС,..,ОО Седьмое обращение.по адОО,....,11 ресу .... (2.)-е обращение по адресуОО,...,О (2.)-е обращение по адресу11,...,1 Далее импульс генератора 1 устанав ливает все младшие разряды (с О-го п П -и) в нулевое состояние и единшу в (П )-й разряд. На выходе схемы ИЛИ-НЕ 19 появляется вновь разрешающий потенциал, и с приходом следующего импульса генератора 1 в эталонном блоке 13 происходит обраще ние по адресу О0...01, и теперь весь цикл контролирует сохранность инфо1 мацни в проверяемом блоке по адресу ОС,...,01 при чтении ее после всех адресов блока во время четных тактов. В следующем цикле контролируется сохранность информации в пров ряемом блоке по адресу ОО,...,1О, затем по адресу ОО,...;11 и так далее до адреса 11,...,11. Таким образом, в устройстве имитируется режим произвольного обращения к проверяемому блоку на рабочей частоте, в то время как работа этало 987 ; ного блока производится на частоте ь раз меньщей. Предлагаемое устройство позволяет производить исследования проверяемого блока памяти, в частности определение области устойчивой работы, на повышенной частоте tto сравнению с частотой работы эталонного блока. В предлагаемом устройстве в качестве эталонного блока памяти может применяться оперативное запоминающее устройство с низким быстродействием , но имеется возможность контрол1ф{ вать быстродействующие блоки постоянной памяти. Применение оперативного запоминающего устройства позволяет использовать для записи информации в память стандартные средства ввода и легко изменять хранимую информацию при внесении изменений в проверяемые постоянные блоки памяти. Формула изобретения Устройство для контроля постоянных блоков памяти по авт. св. № 607282, отличающееся тем, что, с целью расширения функциональных возможностей за счет определения области устойчивой работы постоянных блоков памяти на повышенной частоте обращений в него введен элемент ИЛИ-НЕ, входы которого подключены к выходам разрядов счетчика с 1-го по И -и (где И BOO/j A/j М- число слов постоянного блока памяти), а выход - к входу ра ешающего чтения эталонного блока памяти, причем единичный выход нулевого разр$ша счетчика подключен к входу разрешения блока сравнения Источники информации, принятые во внимание при экспертизе 1. Авторское, свидетельство СССР N 6О7282, кл. G 11 С 29/ОО, г 1978.

-hi

411

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля постоянных блоков памяти | 1976 |

|

SU607282A1 |

| Устройство для контроля постоянной памяти | 1982 |

|

SU1083235A1 |

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1051585A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для сопряжения | 1983 |

|

SU1129603A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля памяти | 1989 |

|

SU1667159A2 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1325571A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

Яд

1

щ г

2f,

//

f

2

1«L

/(

/5

Авторы

Даты

1982-12-15—Публикация

1980-09-12—Подача