.1 .

Изобретение относится к aercwaтике и цифровой вычислительной технике и может быть использовано при разработке преобразователей в вычислительных устройствах.

Известен преобразователь прямого кода в дополнительный, содержащий (п-1) одноразрядных сумматоров, где п - разрядность входного кода, при.чем выход суммы i-ro сумматора является выходом 1-го разряда преобразователя и соединен с первым входе ()-го сумматора, второй вход которого является входом ()-ro разряда преобразователя, а вход переноса соединен с выходом переноса i-ro сумматора tl.

Недостаток данного преобразователя состоит в его относительной сложности.

Наиболее близким к предлагаемому является преобразователь прямого кода в дополнительный, содержащий (п-1) преобразукйций модуль, каждый

из которых содержит элементы И и ИЛЦ Кроме того каждый п{ еобразующий модуль этого преобразователя содержит. элементы И-ИЛИ 2.

Недостатки известного преобразователя состоят в относительно большом объеме аппаратуры и использовании парафазных входов.

Цель изобретения - упрощение преобразователя.

to

Поставленная цель достигается тем, что в преобразователе последовательного кода в параллельный, содержащем (п-1), где п - разрядность входного кода преобразующих модулей, каждый

15 из которых содержит элемент И и элемент ИЛИ, причем первый вход элемента ИЛИ 1-го (1 1-п-1) преобразующего модуля соединен с входом i-ro разряда преобразователя, второй вход

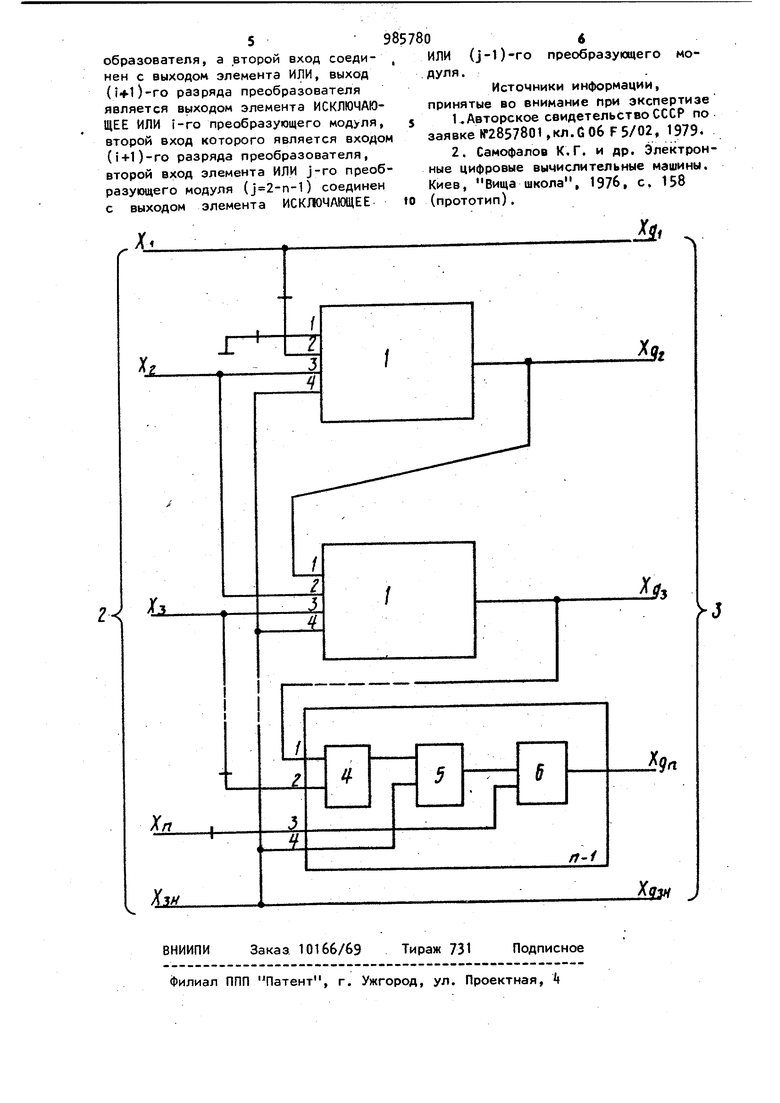

20 элемента ИЛИ первого преобразующего модуля соединен с входом логического нуля преобразователя, входы первого и знакового разрядов преобразователя являются соответственно выходами пер вого и знакового разрядов преобразователя, каждый преобразующий модул содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выхо дом элемента И, первый вход которого соединен с входом знакового разря да преобразователя, а второй вход со дйнен с выходом элемента ИЛИ, выход (i+1)-ro разряда преобразователя яаг ляется выходом эл.мента ИСКЛЮЧАЮЩЕЕ ИЛИ i-ro преобразующего модуля, второй вход которого является входом (i+1)-ro разряда преобразователя, второй вход элемента ИЛИ |-го преобразукхцего модуля (j 2-n-1) соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (j-l)-ro преобразующего модуля. На чертеже приведена функциональ ная схема предлагаемого устройства, Преобразователь содержит п-1 пре образующих модулей 1, где п - количество цифровых разрядов, входы 2, выходы 39 каждый преобразующий модуль содержит элементы ИЛИ t, И 5, ИСКЛЮЧАЮЩЕЕ ИЛИ 6. Преобразователь работает следующим образом. Младшим разрядом входной информа ции является разряд Х, старшим Xf, Хзп знаковый разряд. Младшим разрядом выходной информации является разряд Хоп старшим - , Х знаковый разряд. Связь между числом Х л и его представлением в дополнительном коде X определяется ра венством Гу-t X, если X 0 f Z+X, если X 0. Получение дополнительного кода производится в соответствии с равен ством -0, Х. ..Х, ,Х.... Если преобразуемое число отрицатель ное, то Хзц К Тогда на вторые входы элементов И 5 поступает сигнал 1 и разрешает прохождение сигнала с выхода элемента ИЛИ k на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6, на второй вход которого поступает i+1 разряд входной информации 2. Например, (для 4-х разрядного устройства на вход устройства поступает код 1,010 (крайний слева разряд - знаковый, крайний справа - младший). Знаковый и младший разряд транслиру ются на выход устройства без изме,нения. На входы первого преобразующего модуля поступают соответствен О, О, 1. Тогда но уровни на выходе первого модуля будет уро вень 1. На входы второго модуля поступают соответственно 1, 1, О, 1. На выходе второго модуля будет уровень 1. Таким образо-и, на выходе устройства установится код 1, 110, т.е. дополнительный код числа 1 ,010. Если преобразуемое- число положительное, то на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 поступает уровень О и число с входов 2 транслирует выход 3 без изменения. Применение предлагаемого устройства позволяет сократить количество связей в 1,7 раза. Так для пятиразрядного устройства у прототипа будет 10 входов, 5 выходов и П связей внутри каждого модуля. Общее количество связей при этом будет 59. У предлагаемого устройства при пятиразрядной структуре будет 5 входов, 5 выходов и 6 связей внутри каждого модуля. Общее количество связей будет 3 (в 1,7 раза меньше), что повышает надежность устройства. Применение предлагаемого устройства позволяет повысить надежность преобразователя прямого кода в дополнительный на 19%. Формула изобретения Преобразователь прямого кода в дополнительный, содержащий (п-1), где п - разрядность входного кода, преобразующих модулей, каждый из которых содержит элемент И и элемент ИЛИ, причем первый вход элемента ИЛИ i-ro (i 1-n-l) преобразующего модуля соединен с входом i-ro разряда преобразователя, второй вход элемента ИЛИ первого преобразующего модуля соединен с входом логического нуля преобразователя, входы первого и знакового разрядов преобразователя являются соответственно выходами первого и знакового разрядов преобразователя, отличающийся тем, что, с целью упрощения преобразователя, в нем каждый преобразующий модуль содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход , которого соединен с выходом элемента И, первый вход которого соединен с входом знаковопо разряда преобразователя, а второй вход соединен с выходок элемента ИЛИ, выход ()-ro разряда преобразователя является выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ i-ro преобразующего модуля, второй вход которого является входом (i+l)-ro разряда преобразователя, второй вход элемента ИЛИ j-ro преобразующего модуля (j 2-n-1) соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ

X.

или (j-l)-ro преобразующего модуля.

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР по заявке N 2857801,кл.С 06 F 5/02, 1979.

2.Самофалов К.Г. и др. Электронные цифровые вычислительные машины. Киев, Вища школа, 1976, с. 158 (прототип).

111

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1985 |

|

SU1315971A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1569825A1 |

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

| Устройство для вычисления порядковых статистик последовательностей из @ - @ -разрядных чисел | 1987 |

|

SU1434424A1 |

| Устройство для формирования интегральных характеристик модулярного кода | 1986 |

|

SU1464293A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Цифровой вычислитель функций | 1986 |

|

SU1354187A1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1608652A1 |

| Вычислительное устройство | 1985 |

|

SU1278840A1 |

| Устройство для вычисления разности двух чисел | 1987 |

|

SU1444753A1 |

L

J.

г

JL

J

Авторы

Даты

1982-12-30—Публикация

1981-01-09—Подача