1

Изобретение относится к технике связи, а именно к радиолокации и может быть использовано в системах передачи информации по каналам, подверженным воздействию, помех, в частности, в бортовых радионави гационкых устройствах.

Известны дешифраторы, выполненные .на основе преобразователей время-код 1 J.

Такие дешифраторы эффективны лишь при небольшой плотности помехи на входе. При повышении плотности пбмех вес, габариты и стоимость таких устройств недопустимо возрастают.

Наиболее близкими к предлагаемому являются дешифраторы, построенные на сдвиговых регистрах. Достоинствами таких дешифраторов являются: высокая стабильность работы, отсутствие подавления полезных сигналов при предельных плотностях помех | 2.

Однако при большой временной базе и высокой разрешающей способности,

требуются сдвиговые регистры с очень большим количеством разрядов, что снижает надежность устройства и усложняет его.

Цель изобретения - повышение надежности устройства. Кроме того, достигается упрощение устройства за счет исключения сдвигового регистра.

Поставленная цель достигается тем,

10 что в устройство, содержа цее генератор тактовых импульсов, выходной элемент И, один из входов которого подключен к входу устройства, а выход к выходу устройства, введены счет чик, элемент НЕ и адресное запоминающее устройство, содержащее дешифратор адреса, элемент ИЛИ и п-ячеек, состоящих из статического триггера, входного и выходного элемента И и

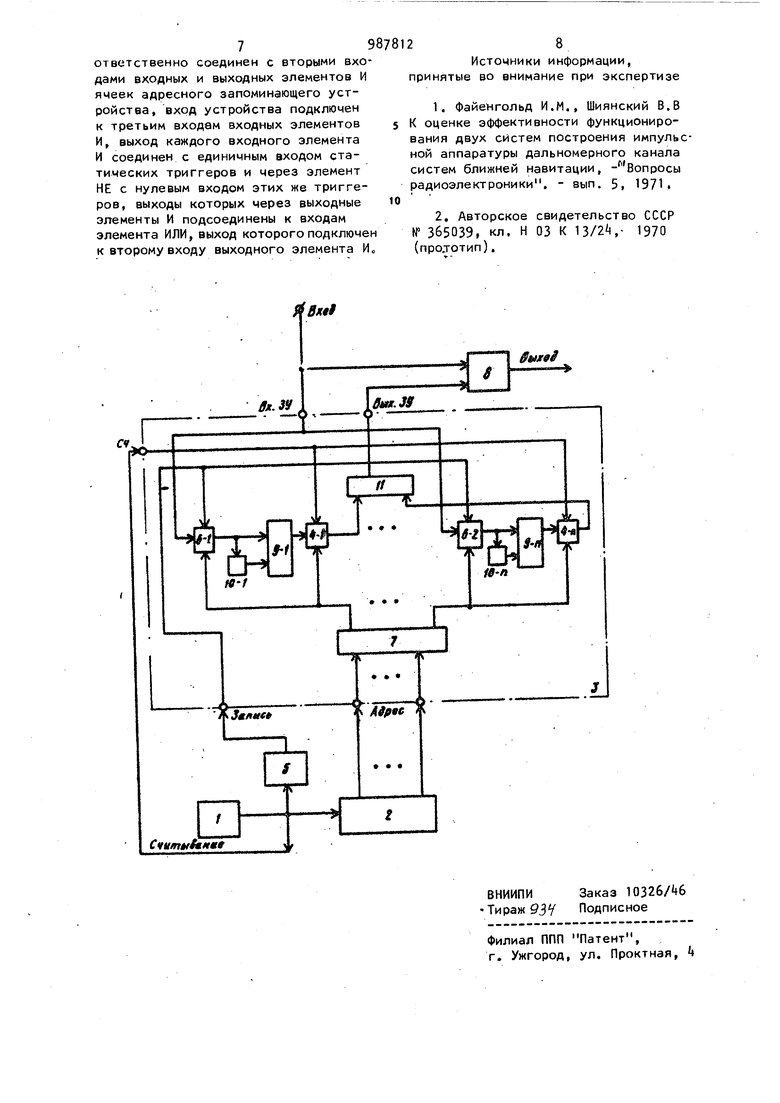

20 элемента НЕ, причем выход генератора тактовых импульсов подключен к входусчетчика, к первым входам выходных элементов И ячеек адресного запоминающего устройства, через элемент НЕ к первым входам входных элемен-тов И ячеек адресного запоминающего устройства,выходы счетчика поразряд но соединены с входами дешифратора адреса адресного запоминающего устройства, каждый выход которого соответственно соединен с вторыми входами входных и выходных элементов И ячеек адресного запоминающего устройства, вход устройства подключен к третьим входам входных элементов И, выход статических триггеров и через элемент НЕ - с нулевым входом этих же триггеров выходы каждого из которых через выходные элементы И подсоединены к входам элемента ИЛИ выход которого подключен к второму входу выходного элемента И. Сущность изобретения заключается в том, что цифровой сдвиговый регист используемый в прототипе, заменяется адресным ЗУ в комбинации со счетчиком и элементом НЕ. Необходимый поло жительный эффект в виде повышения н дежности достигается за счет введения новых элементов и соответствующ связей в устройстве. Значительно большая удельная емкость ЗУ по сравнению со сдвиговым регистром также обеспечивает дополнительный положительный эффек Р. На чертеже изображена функционал ная схема устройства. Выход генератора 1 тактовых импульсов подключен к входу счетчика 2, к входу считывания адресного запоминающего устройства 3 и далее к первым входом выходных элементов И И (-п) также выход генератора 1 через элемент НЕ 5 подключен к вх ду записи запоминающего устройства 3 и далее - к первым входам входных элементов И 6-1-(6-п). Выходы счетч ка 2 поразрядно соединены с адресными входами запоминающего устройст 3 и далее - с входами дешифратора адреса 7, каждый выход которого соответственно соединен с вторыми вхо ми входных и выходных элементов И 6(6-п) и A-l-(-n). Вход устройства подключен к входу элемента И 8, к входу запоминающего устройства 3 и далее - к третьим входам входных элементов И 6-1-(6-п), выход каждого из которых соединен с единичными входами статических триггеров (Э-п) и через элемент НЕ lO-l-(lO-n с нулевым входом этих же триггеров 98 .4 (9-п). Выходы статических триггеров ) через выходные элементы И if-l-Ct-n) подключены к входам элемента ИЛИ 11, выход которого является выходом запоминающего устройства 3 и подсоединен к второму входу элемента И 8. Выход элемента И 8 является выходом устройства. Дешифратор время-импульсных кодов работает следующим образом. Генератор 1 тактовых импульсов неnpepbiBHo генерирует последовательность импульсов типа меандр, поступающих на счетчик 2, на элемент НЕ 5 и на вход считывания запоминающего устройства 3, т.е. на элементы И -1(-п). Инвертированная тактовая последовательность с выхода элемента НЕ 5 поступает на вход записи запоминающего устройства 3, т..е. на элементы И 6-1-(6-п). Частота генератора и емкость счетчика выбраны таким образом, чтобы период заполнения счетчика точно соответствовал временной базе кода. Счетчик 2 через дешифратор 7 поочередно подает разрешающий потенциал на различные ячейки запоминающего устройства 3 ( вторые входы элементов И 6-1-(6-п) и -l-Ct-n) , т.е. меняется адрес на адресном входе запоминающего устройства. В течение времени существования каждого адреса на запоминающем устройстве 3 приходят последовательно два импульса; импульс считывания на вход считывания (на элемент И (-л) , затем импульс записи на вход записи запоминающего устройства 3 (на элемент И 6-1-(6-п). В случае, если на входе устройства имеется импульс, то он попадает на информационный вход запоминающего устройства 3 и далее на вход элементов И 6-1-(6-п) и, совпадая с импульсом записи, через элемент И 6-1-6-п зафиксируется триггером 9-1(). Если импульс на входе отсутствует, то с помощью элемента НЕ lO-l-(lO-n) итриггер 9-1-(9-п) будет установлен в нулевое положение. Как указано выше, перед импульсом записи на данном адресе появляется импульс считывания. В случае, если триггер () в предыдущем цикле работы счетчика 2, т.е. на временном расстоянии равным базе кода, был установлен в положение 1, на выходе элемента и ) появится импульс, который через элемент ИЛИ 11 поступит на вход элемента И 8, где совпадает с входным импульсом, если он в этот момент присутствует, и пройдет на выход устройства. Таким -образом про изойдет декодирование. Адресное запоминающее устройство 3 может быть любой структуры, важно лишь, чтобы оно имело необходимые входы и выходы - вход записи, вход считывания, входы адреса, информационный вход и выход информации. Положительный эффект в виде повы шения надежности обеспечивается вве дением запоминающего устройства и счетчика с соответствующими связями Выход из строя одной ячейки памяти прототипа приводит к полному прекращению его работы. В предлагаемом устройстве отказ одной из ячеек запоминающего устройства лишь несколько снижает эффективность работы устройства (обратно пропорционально общему количеству ячеек памяти). Например, дешифратор предназначен для декодирования время-импульсного кода с базой .00 мкс и разрешающей способностью ,1 МКС. Количество ячеек памяти п 1000. Если дешифратор выполнен на сдвиговом регистре, то выход из строя лю бого элемента сдвигового регистра приводит к выходу из строя всего уст ройства, т.е. суммарная вероятность отказа , А -Ли 1000Л, где . X - вероятность отказа ячейки памяти сдвигового регистра. Дешифратор на запоминающем устройстве будет содержать ячеек памяти и . 1000Si-IO ячеек счетчика, а также некоторое число управляющих схем, эквивалентное а нашем случае fli 100 ячейкам сдвигового регистра, В этом дешифраторе полный отказ произойдет только в случае выхода из строя одной из управляющих схем или триггеров счетчика (выходом из строя одной из ячеек памяти можно пренебречь). Полагая, что вероятность отказа ячейки .счетчика предлагаемого уст2«роиства равна Х, получим суммарную вероятность отказа , т.е. надежность предлагаемого д«1мф ратора выше, чем у прототипа в рассматриваемом случае в -к 9 раэ. Дополнительно следуе учесть , что положительный эффект обеспечивается использованием s дешифраторе распространенных в настоящее время адресных запоминакедих устройств, плотность упаковки информации в которых в несколько раз больше, чем в сдвиговых регистрах. При практической реализации устройства-прототипа 1«1спользовать микросхемы с большой степенью интеграции, даже в случае появления таких мик-. росхем в дальнейшем, принципиально не представляется возможным, так как при переключении кодов необходимо изменять длину сдвигового регистра, т.е. иметь отводы от него, что заставляет набирать сдвиговый регистр из значительного числа коротких кусков. Предлагаемый дешифратор включает единый элемент памяти, реа/«13ующий на одной микросхеме, тем более, что емкость последних достигает нескольких кБит на корпус. Формула изобретения Дешифратор время-импульсных кодов, содержащий генератор тактовых импульсов, выходной элемент И, один из входов которого подключен-к входу устройства, а выход - к выходу устройства, отличающийся тем, что, с целью повышения надежности, в него введены счетчик, элемент НЕ и адресное запоминающее устройство, содержащее дешифратор адреса, элемент ИЛИ и п ячеек, состоящих каждая из статического триггера, входного и выходного элементов И и элемента НЕ, причем выход генератора тактовых импульсов подключенк входу счетчика, к первым входам выходных элементов И ячеек адресного запоминающего устройства, через элемент НЕ к первым входам входных элементов И ячеек адресного запоминающего устройства, выходы счетчика поразрядно соединены с входами дешифратора ад- . реса адресного запоминающего устройства, каждый выход которого со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для выбора заданного числа повторений двоичных чисел | 1984 |

|

SU1267402A1 |

| Запоминающее устройство на сдвиго-ВыХ РЕгиСТРАХ | 1979 |

|

SU841052A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1361615A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

Авторы

Даты

1983-01-07—Публикация

1981-07-30—Подача