Изобретение относится к тике и цифровой вычислительной технике и может быть использовано при построении преобразователей в устройствах поразрядного уравновешивания, устройств записи и считывания информации на кассетной магнитной ленте, аналого-цифровых преобразователей.

Известен преобразователь, содерхЦ щий блок приема, преобразователь последовательного кода в параллельный и преобразователь параллельного. кода в число-импульсный код L.

Однако устройство характеризуется увеличенным временем преобразования из-за необходимости последовательного осуществления таких операций, как прием последовательного кода, передача параллельного кода из одного преобразователя в другой и преобразование параллельного кода в число импульсов.

Наиболее близким к предлагаемому по технической сущности является преобразователь кода в число импульсов, содержащий основной и вспомогательный счетчики, TpHrrei it запрета и переключения, логические элементы. Преобразователь выполняет функции

как приема последовательного кода,, так и собственно преобразования 2. Недостаток устройства заключается

f в относительно низком быстродействии, связанНс с тем, что вьшеуказанные две функции не могут быть совмещены во времени, так как преобразованию должен подвергаться весь пpинимae шй

fQ код, что ограничивает скорость рабо ты данного преобразователя. При использовании этого преобразователя дпя обработки непрерывно поступающих кодовык последовательностей необходимо либо прерывать прием на

5 время преобразования параллельного двоичного кода в число импульсов, что в ряде случаев является недопустимым, либо устанавливать дополни.| тельные регистры памяти, что услож няет аппаратуру и снижает надежность.

Цель изобретения - повышение быстродействия.

Указанная цель достигается тем, что в преобразователь последователь25 ного двоичиого кода в число-импульсный код, содержащий двоичный счетчик, генератор импульсов, введен сдвиговый регистр, управляющий вход которого соединен с тактовым входом

0 преобразователя, установочным входом

двоичного счетчика и первым входом запуска генератора импульсов, второй вход запуска которого соединен . с информационным входом преобразователя, выход которого соединен со счетным входом двоичного счетчика и выходом генератора импульсов, вход сброса которого соединён с выходом переполнения двоичного счетчика информационные входы которого с первого по (п-1)-й разряды, где п число разрядов преобразуемо1-о кода, соединены соответственно с выходами с п-го по второй разряды сдвигового регистра, информационный вход которого соединен с входом логической единихц преобразователя.

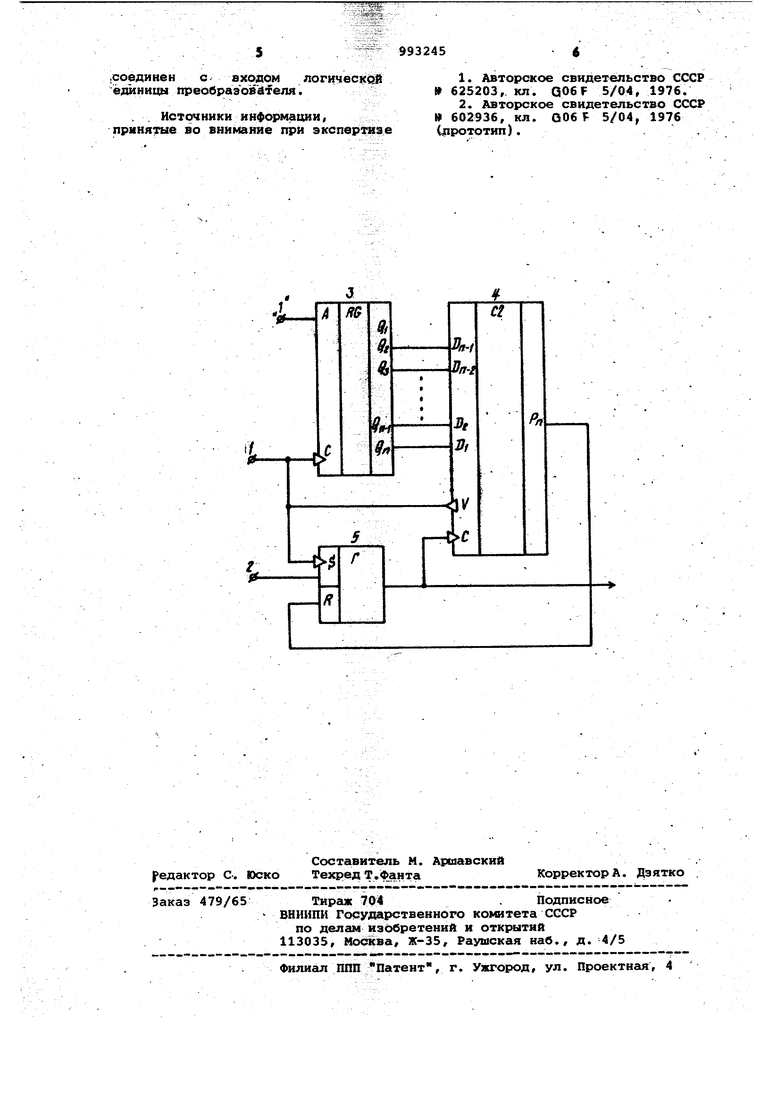

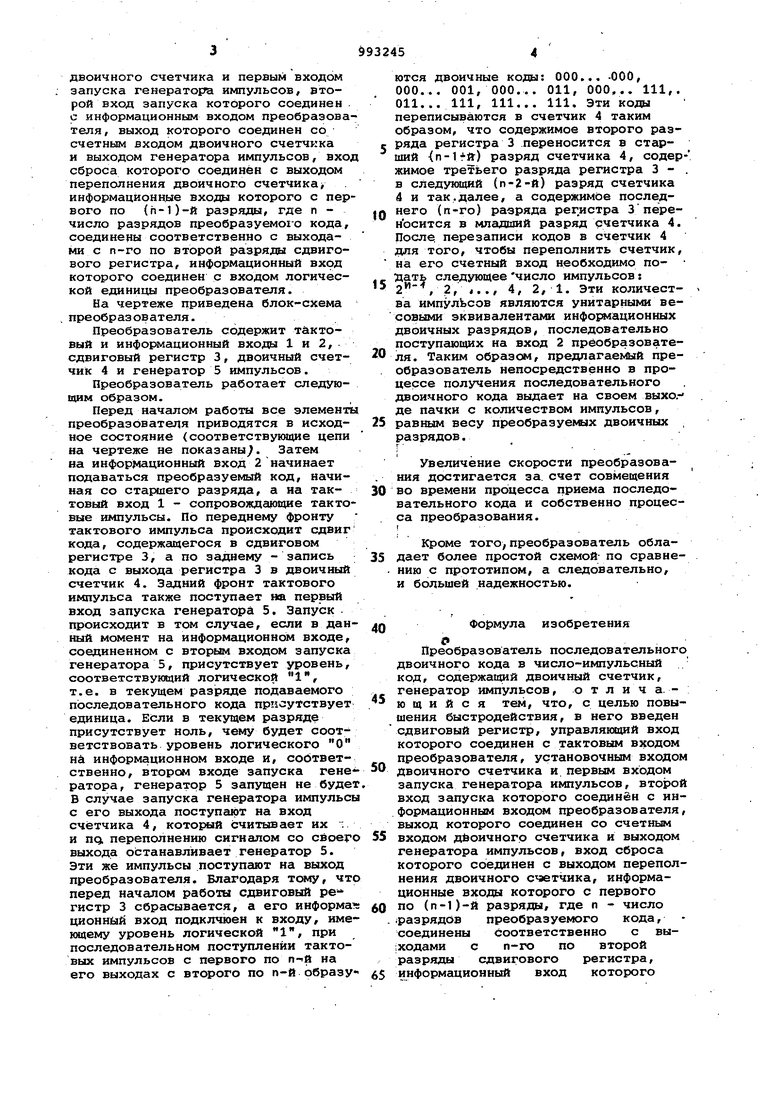

На чертеже приведена блок-схема преобразователя.

Преобразователь содержит тактовый и информационный входы 1 и 2, сдвиговый регистр 3, двоичный счетчик 4 и генератор 5 импульсов.

Преобразователь работает следующим образом.

Перед началом работы все элемент преобразователя приводятся в исходное состояние (соответствующие цепи на чертеже не показаны. Затем на инфор:мационный вход 2 начинает подаваться преобразуемый код, начиная со старшего разряда, а на тактовый вход 1 - сопровождающие тактовые импульсы. По переднему фронту тактового импульса происходит сдвиг кода, содержащегося в сдвиговом регистре 3, а по заднему - запись кода с выхода регистра 3 в двоичный счетчик 4. Задний фронт тактового импульса также поступает Hia первый вход запуска генератора 5, Запуск . происходит в том случае, если в данный момент на информационном входе, соединенном с вторым входом запуска генератора 5, присутствует уровень, соответствующий логической 1, т.е. в текущем разряде подаваемого последовательного кода присутствует единица. Если в текущем разряде присутствует ноль, чему будет соответствовать уровень логического О н информационном входе и, соответственно, втором входе запуска генератора, генератор 5 запущен не будет В случае запуска генератора импульсы с его выхода поступают на вход счётчика 4, ко-юрал считывает их и nq. переполнению сигналом со своего выхода останавливает генератор 5. Эти же импульсы поступают на выход преобразователя. Благодаря тому, что перед началом работы сдвиговый ре гистр 3 сбрасывается, а его информате ционный вход подклчюен к входу, имеющему уровень логической 1, при последовательном поступлении тактовых импульсов с первого по n-ifl на его выходах с второго по п-й образу

ются двоичные коды: 000.., -000, 000... 001, 000... 011, 000... 111,. 011... 111, 111... 111. Эти коды переписываются в счетчик 4 таким образом, что содержимое второго разряда регистра 3 переносится в старший ) разряд счетчика 4, содержимое третьего разряда регистра 3 - . в следующий {n-2-й) разряд счетчика 4 и так.далее, а содержимое последнего (п-го) разряда рег.истра 3 переносится в младший разряд рчетчика 4. После, перезаписи кодов в счетчик 4 для того, чтобы переполнить счетчик, на его счетный вход необходимо подать следующее число импульсов:

, 2, J.., 4, 2, 1. Эти количества импульсов являются унитарными весовыми эквивалентами информационных двоичных разрядов, последовательно поступающих на вход 2 прёобразователя. Таким образе, предлагаемый преобразователь непосредственно в процессе получения последовательного двоичного кода выдает на своем выхо.де пачки с количеством импульсов,

равным весу преобразуемых двоичных , разрядов.

Увеличение скорости преобразования достигается за. счет совмещения во времени процесса приема последовательного кода и собственно процесса преобразования.

Кроме того,преобразователь обладает более простой схемой по сравнению с прототипом, а следовательно, и большей надежностью.

Формула изобретения г

Преобразователь последовательного двоичного кода в число-импульсный код, содержащий двоичный счетчик, генератор импульсов, о т л и ч а. ю щ и и с я тем, что, с целью повышения быстродействия, в него введен сдвиговый регистр, управлянвдий вход которого соединен с тактовым входом преобразователя, установочным входом двоичного счетчика и первым входом

запуска генератора импульсов, второй вход запуска которого соединён с информационным входом преобразователя, выход которого соединен со счетным

5 входом двоичного счетчика и выходом генератора импульсов, вход сброса которого соединен с выходом переполнения двоичного с эетчика, информационные входы которого с nepBoto

0 по (п-1)-й разряды, где п - число . (разрядов преобразуемого кода, соединены соответственно с выходами с п-го по второй разряды сдвигового регистра,

$ информационный вход которого

.соединен е входом логичес сй единицы преобраэО зателя.

. . Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 625203, кл. Q06F 5/04, 1976.

2.Авторское свидетельство СССР 602936, кл. Q06f 5/04, 1976 (лрототип).. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Преобразователь последовательного кода в параллельный | 1979 |

|

SU783789A1 |

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1159165A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Преобразователь кода | 1989 |

|

SU1619401A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771660A1 |

Авторы

Даты

1983-01-30—Публикация

1981-08-10—Подача