(54) ПРЕОБРАЗОВАТЕЛЬ ОТРАЖЕННОГО ДВОИЧНОГО КОДА В ПОЗИЦИОННЫЙ ДВОИЧНЫЙ КОД Н ОБРАТНО

1

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении измерительных систем и управляющих систем.

Известно устройство для преобразования отраженного двоичного кода в позиционный двоичный код, содержащее элементы задержки, элементы И, ИЛИ, И-НЕ триггеры и формирователи в разряде 1.

Недостаток известного устройства состоит в низком быстродействии и невозможности обратного преобразования.

Наиболее близким решением данной задачи по технической сущности и схемному построению является преобразователь двоичного кода в код Грея и обратно, со.цержа1иий регистр из триггеров со счетными входами группы, формирователей, элементов И и элементов задержки 2,

. Недостаток известного устройства состоит в низком быстродействии, так как преобразование в (п-1) этап, каждый из которых включает в себя сумму времен срабатывания триггера, формирователя, элемента И и времени задержк.и сигнала элементом задержки-.

Целью изобретения является увеличение быстродейс вия.

Поставленная цель достигается тем, что в преобразователь отраженного двоичного кода в позиционный двоичный код и обратно, содержащий регистр и первую группу элементов И, первые входы которых соединены с управляющим входом преобразователя, выходы кото10рого являются выходами регистра, единичный вход п-го разряда которого соединен с входом старшего разряда преобразователя, где п - число разрядов преобразуемого кода введены вторая и

15 третья группы из п-1)-го элемента И группа из (п-2) полусумматоров, причем i-й полусумматор (i l-r n-1) имеет (i+1) входов и элемент НЕ, вход которого является стробирующим входом

20 преобразователя и соединен с первыми входами элементов И второй группы, вторые входы которых соедин ены с входами соответствующих разрядов преобразователя, а выходы i-ro элемента И

25 второй и третьей групп соответственно-с единичными и счетными входам соответствующих разрядов регистра, первые входы элементов И третьей группы соединены с выходом элемента НЕ,

30 второй вход j -го ( j 1 п -2J злеента И третьей группы соединен с выодом j -го полусумматора группы, первый вход которого соединен с вхоом ( j +1)-го разряда преобразователя, второй вход j -го элемента И первой группы соединен с входом (j +2)-го5 разряда .преобразователя, второй вход (n-l)-ro элемента И третьей группы соединен с входом п-го разряда преобазователя и вторым входом (п-2)-го элемента И первой группы, выход- j 10 элемента И первой группы соединен +1)-ми входами с первого по) -ый полусумматоров группы.

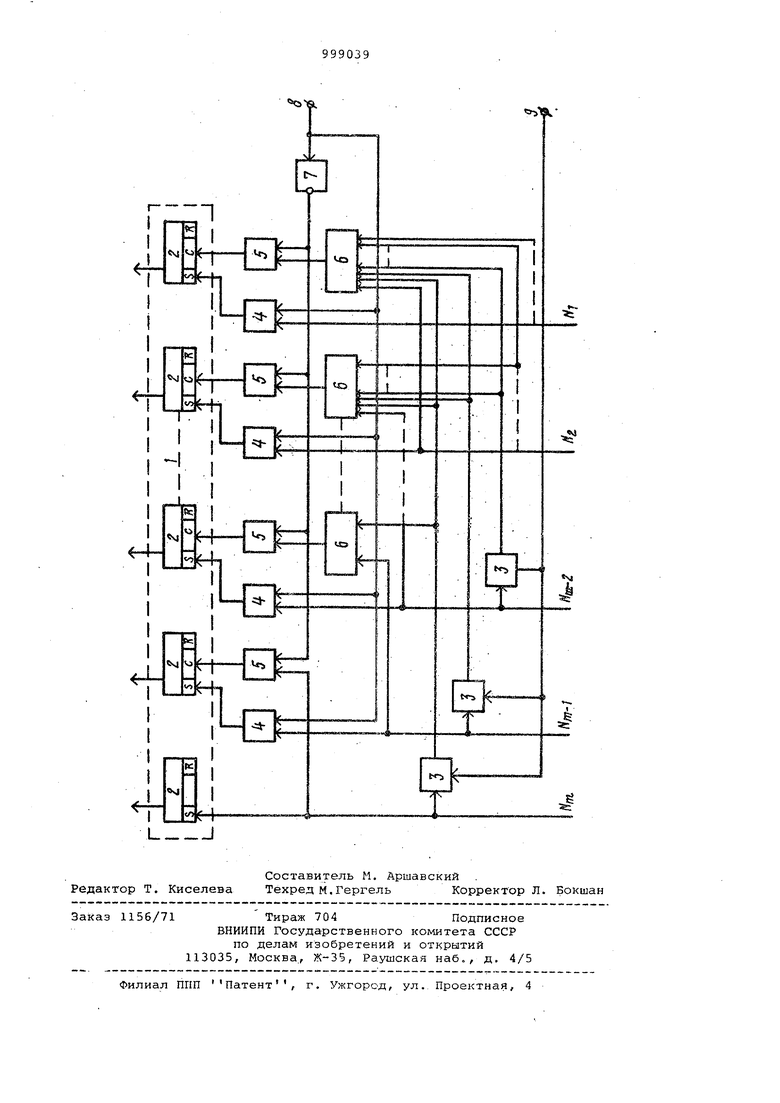

Па чертеже приведена блок-схема предлагаемого отраженного двоичного 15 кода в позиционный двоичный код и обратно.

Преобразователь содержит регистр 1, включающий в себя.триггеры 2, -пец вую 3, вторую 4 и третью 5 группы «п элементов И, группу б полусумматоров, инвертор 7, стробируюций входов, управляющий вход 9 и входы Nf.

Преобразователь отраженного двоичного кода в позиционный двоичный код 25 и обратно работает следующим образом.

В исходном состоянии все триггеры 2 )егистра 1 находятся в нулевом состоянии, на информационных входах N(N( низкие потенциалы, на стробирую- ,. щемвходе 8 высокий потенциал, на вы- ходах элементов И 4,И 5 и полусумматоЕ/ов б низкий потенциал. Подлежащий преобразованию код записывается в триггеры 2 регистра 1, в старший разряд непорредственно, а в остальные 35 разряды через элементы И 4, открытые по первым входам единичным потенциалом со стробирующего входа 8. Состояние триггеров 2 изменяется в разрядах, в которых код равен единице. 40 При наличии на входах полусумматоров нечетного числа единиц, на их вько-дах появляются единичные .потенциалы. Для преобразования отраженного двоичного кода в позиционный двоичный код45 на управлякядий вход 9 необходимо подать единичный потенциал на все время. преобразования. При этом состояние триггеров 2 в регистре 1 изменяется на противоположное в тех разрядах, ел по отношению к которым в старших разрядах имеется нечетное количество единиц в исходном коде. Для преобразования позиционного двоичного кода в отраженный двоичный код на управляющий вход 9 необходимо подать нулевой потенциал на все время преобразования, В результате чего на выходах элементов И 3 устанавливаются нулевые потенциалы. При этом состояние триггеров 2 в регистре 1 изменяется на про-60 тивоположное в тех разрядах, по от- ношению к кот:орым в соседнем старшем разряде имеется единица в исходном коде. Для получения максимального быстЕ одействия п е6бразователя в слу-бб

чае, если время t срабатывания полусумматора б младшего разряда больше времени t-j срабатывания триггера 2, время t, от момента подачи исходного кода до момента подачи стробируквдего потенциала определяется выражением t + t,, где tya- время срабатывания элемен- та И 3.

Бремя преобразования Тпр для этого случая определится выражением

Тпр t +tng +tv,s +t, где время срабатывания инвертора 7 ; tyc - время срабатывания элемента

И 5.

Для получения максимального быстродействия преобразователя в случае, если время t t.,, время t определяется

- тгПредположим необходимо преобразовать Четырехразрядный отраженный -дво ичный код 1010 (что соответствует в десятичной системе числу двенадцати) в позиционный двоичный код. При поступлении.исхфдного кода 1010 в старшем и во втором разрядах регистра 1. триггеры 2 установятся в единичное состояние, и в регистре будет записа исходный вал. Единичный потенциал, поступивший на вход старшего разряда вызовет появление на выходе элемента И 3 единичного потенциала, который, поступив на другой вход полусумматора б второго разряда, приведет к ее срабатыванйю так как на первом ее входе присутствует нулевой потенциал со входа N. Полусуг/пиатор 6 первого разряда не срабатывает, так ка н его входах присутствует четное число единиц. Через время t,после подачи исходного кода на стробируюадий вход 8 подается нулевой поетнциал, закрывающий .1И 4 по первому входу Единичный потенциал с выхода инвертора 7, поступая на первые в-ходы элементов И 5, приведет к срабатыванию тех из них, на вторых входах которых присутствует единичный потенциал. В данном случае единичный потенциал с выхода элемейтов И 5 во втором и третьем разрядах установит триггеры 2 в противоположное состояние, в результате чего в регистре оказывается позиционный двоичный код 1100 (в Эдесятичной сис.те.меТ - 12).

Следовательно, при преобразовании отраженного двоичного кода в позиционный двоичный код состояние триггеров в регистре изменяется на противоположное в тех разрядах, в которых срабатывает полусумматор при наличии нечетного количества единиц во всех старших по отношению к данному разрядов исходного кода;

Таким образом, при наличии единичного потенциала на управляющем входе в преобразователе устанавливается режим преобразования отраженного двоичного кода в позиционный двоичный код который предусматривает один этап пре образования, включаняций в себя состоя ние триггеров тех разрядов, по отношению к которым в старших разрядах исходного кода имеется нечетное количество единиц. Быстродействие преобразователя ограничено лишь временем распространения .сигнала на двух элементах И, -полусумматоре, инверторе и времени переключения триггера. Предположим необходимо преобразовать четырехразрядный позиционный код 1101 (тринадцать) в отраженный двоичный код. Так как на первый вход полусумматора 6 второго разряда посту пает единичный сигнал информационного входа Nj , а на другом его вхсэде нулевой потенциал, то нд выходе полусумматора б появляется единичный потенциал. На выходе полусумматора 6 первого разряда продолжает оставаться нулевой потенциал, вследствие наличия нулевых потенциалов на его вхо-. дах. Через.время t после подачи исходного кода на стробирующий вход 8 подается нулевой потенциал, закрывающий элементы И 4 по первому входу. Единичный потенциал с выхода инвертора 7 приведет к срабатыванию тех элементов И 5, на вторых входах которых присутствует единичный потенциал. В данном случае единичный потенциал с выхода элементЬв И 5 во. втором и третьем разрядах установит триггеры в противоположное состояние, в резуль тате чего в регистре оказывается отраженный двоичный код 1011 {в десятич ной системе -13). Следовательно, при преобразовании позиционного двоичного кода в отраже вый двоичный код состояние триггеров в регистре изменяется в тех разрядах в которых полусумматор срабатывает при наличии единицы в соседнем старвдам разряде исходного кода. . Таким образом, при наличии нулевого потенциала на управляющем входе в преобразователе устанавливается режим преобразования позиционного двоичного кода в отраженный двоичный код, который предусматривает один этап преобра зования.. Конструктивные особенности предлагаемого технического решения позволяют.повысить быстродействие преобразователя, так как преобразование отраженного двоичного кода в позиционный ДВОИЧНЫЙ код происходит в один этап, включающий в себя запись в регистр исходного кода и изменения на противоположное состояние триггеров тех разрядов, по отношению к которым в старших разрядах исходного кода имеет ся нечетное количество единиц. Время преобразования, в общем случае, определяется как сумма двух времен срабатывания элементов И, времени срабатытвания полусугФ(атора в младшем , времени срабатывания инвертора и времени переключения триггера. Предлагаемый преобразователь может быть построен в виде чисто комбина- ционного устройства, для чего разрядные входы преобразователя должны быть заведены на дополнительные входы полусумматоров . В этом случае необходимость в триггерах и элементах И 5 отпадает, а быстродействие преобразователя увеличивается. Формула изобретения Преобразователь отраженного двоичного кода в позиционный двоичный код и обратно, содержащий регистр и первую группу элементов И, первые входы которых соединены с управляющим входом преобразователя, выходы которого являются выходами регистра, единичный вход п-го разряда которого соединен с входом старшего разряда преобразователя , где п - число разрядов преобразуемого кода, отличающийс я тем, что, с целью повышения быстродействия, в него введены вторая и треть группы из {п-1)-го элемента И, группа из- {п-2) полусумматоров, причем i-ый полусумматор (1 1 т п-1) -имеет (i+1) входов .и элемент НЕ, вход которого является стробирующим входом преобразователя соединен с первыми входами элементов И второй группы, вторые входы {соторых соединены с входами соответствующих разрядов преобразователя, а выходы i-ro элемента И второй и третьей групп соответственно - с единичными и счетными входами соответсТвукхцйх разрядов регистра, первые входы элементов И третьей группы соединены с выходом элемента ЦБ, второй вход -го ( j 1 -г п -2)- элемента И третьей группы соединен с выходом j -го полусумматора группы, . первый вход которого соединен с входом ( i -И)-го разряда преобразователя, второй вход j -го элемента И первой группы соединен с входом ( +2)-го разряда преобразователя, второй вход (п-1)-го элемента И третьей группы соединен с входом п-го разряда преоб- , разователя и вторым входом (п-2)-го элемента И первой группы, выход j -го элемента И первой группы соедине н с (j -И)-ми входами с первого по j -ый. полусумматоров группы. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР . №369706, кл. Н 03; К 13/24,. 08.11.73. 2.Авторское свидетельство СССР № 560222, кл. G 06 F 5/02, 30.05.77 , (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Преобразователь двоичного однопеременного кода в позиционный двоичный код | 1980 |

|

SU955023A1 |

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Преобразователь унитарного кода в двоичный позиционный код | 1986 |

|

SU1325709A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1023334A2 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

| Преобразователь двоичного кода вдОпОлНиТЕльНый | 1979 |

|

SU851395A1 |

Авторы

Даты

1983-02-23—Публикация

1981-02-17—Подача