Изобретение относится к вычислительной технике, в частности к средствам автоматического контроля микропроцессорных устройств, и может быть использовано в радиоэлектронной промышленности и промышленности средств связи в процессе разработки, производства и эксплуатации микропроцессорных систем.

Цель изобретения - повышение быстродействия формирователя.

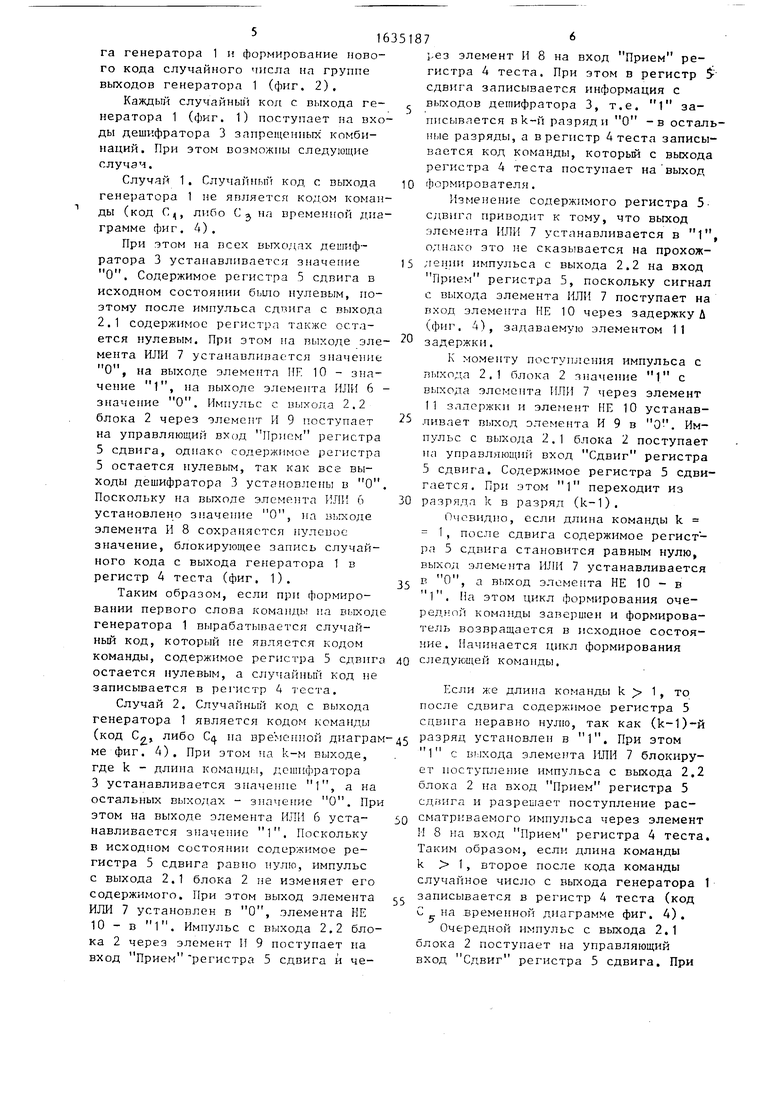

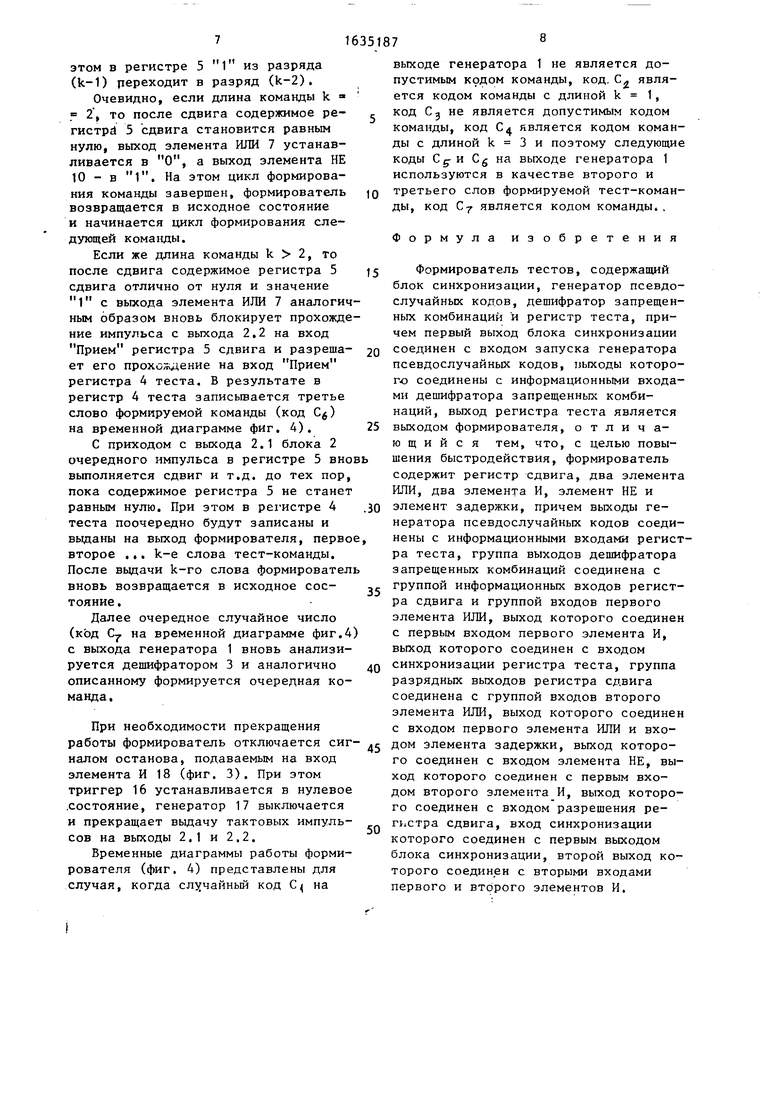

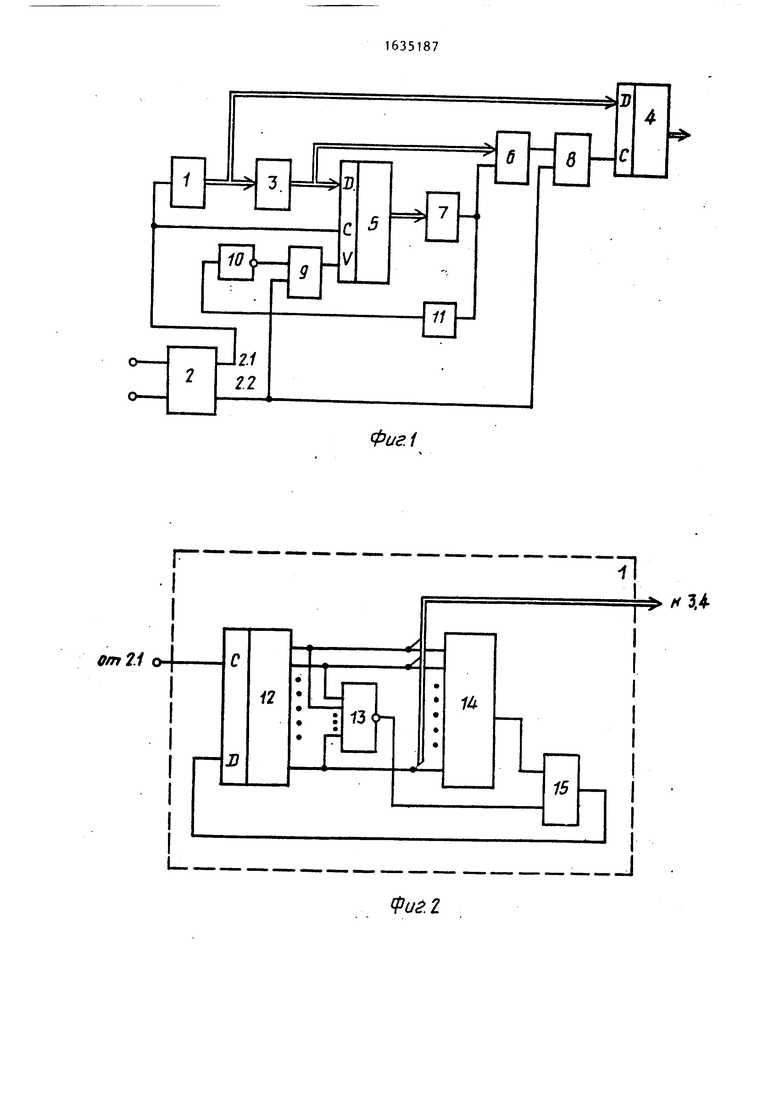

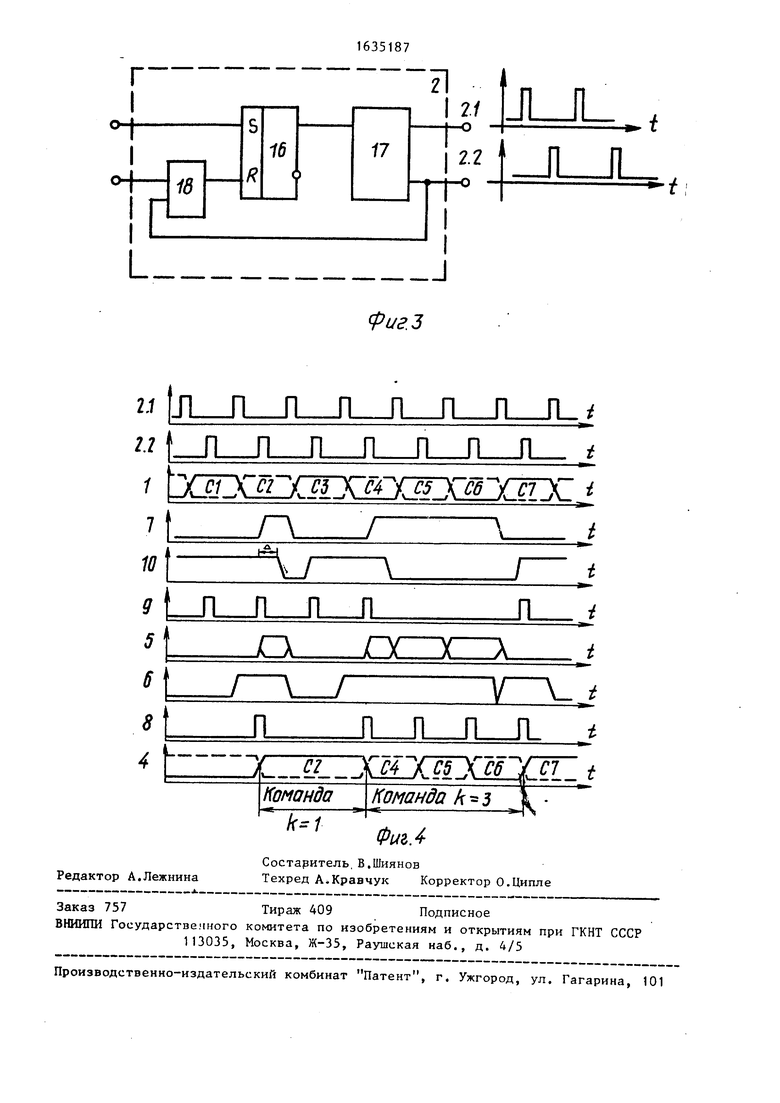

На фиг. 1 представлена структурная схема предлагаемого формирователя тестов, на фиг. 2 - схема генератора псевдослучайных кодов; на фиг. 3 - схема блока синхронизации; на фиг.4 - временные диаграммы функционирования формирователя.

Формирователь тестов содержит ге- нератор 1 псевдослучайных кодов, блок 2 синхронизации с выходами 2.1

и 2.2, дешифратор 3 запрещенных комбинаций, регистр 4 теста, регистр 5 сдвига, первый элемент ИЛИ 6, второй элемент ИЛИ 7, первый элемент И 8, второй элемент И 9, элемент НЕ 10 и элемент 11 задержки.

Генератор 1 псевдослучайных кодов предназначен для формирования случайных чисел. В простейшем случае он может быть реализован на сдвиговых регистрах с обратными связями. Генератор, показанный на фиг. 2 содержит регистр 12 сдвига, элемент И-НЕ 13, сумматор 14 по модулю два и элемент ИЛИ 15. Очередное случайное число получается в регистре 12 сдвига при поступлении на его управляющий вход Сдвиг импульса с выхода 2.1 блока 2 синхронизации. Сумматор 14 по модулю два и элемент ИЛИ 15 образуют цепь обратной связи генератора. Элемент

оэ оо ел

00

1

И-НЕ 13 предназначен для обеспечения правильной работы генератора в случае, если в регистре 12 сдвига будет записан нулевой код..

Блок 2 синхронизации (фиг. 3) предназначен для формирования двух последовательностей сдвинутых один относительно другого тактовых импульсов на выходах 2.1 и 2.2 соответствен но. Блок 2 синхронизации содержит триггер 16, генератор 17 тактовых импульсов и элемент И 18.

Дешифратор 3 (фиг. 1) предназначен для выбора из случайной последователь ности кодов с выхода генератора 1 тех чисел, которые являются допустимыми кодами команд микропроцессора, а также для определения длины команды. Дешифратор имеет 1 выходов, где 1 - максимально возможная длина команды контролируемого микропроцессора. Если случайное число на входе дешифратора 3 не является допустимым кодом команды, на всех его выходах устанавлива- ются значения О, Если же случайное число на входе дешифратора 3 является кодом некоторой команды, на k-м выходе,- где k - длина рассматриваемой команды, устанавливается значение 1 а на всех1 остальных выходах - значение О.

Регистр 4 теста служит для хранения очередного слова формируемой тест команды. Регистр имеет информационный

вход, по которому поступают соответствующие слова, и управляющий вход При ем1 .

Регистр 5 сдвига предназначен для подсчета числа слов формируемой команды. Регистр 5 сдвига имеет информационные входы для параллельного приема информации, управляющий вход Прием и управляющий вход Сдвиг. Сдвиг в регистре осуществляется в сторону младших разрядов.

Первый элемент ИЛИ 6 предназначен для выработки сигнала 1 в случае, если на вход дешифратора 3 подается допустимый код ком шды или если содержимое регистра 5 сдвига отлично от нуля.

Второй элемент ИЛИ 7 предназначен для выработки сигнала 1 в случае, если содержимое регистра 5 сдвига отлично от нуля.

Первый элемент И 8 предназначен для формирования управляющего сигнала Прием в регистр 4 теста. Сигнал

Прием вырабатывается импульсом с выхода 2.2. блока 2 синхронизации при условии, что на выходе первого элемента ИЛИ 6 установлено значение 1м Второй элемент И 9, элемент НЕ 10 и элемент 11 задержки предназначены для формирования управляющего сигнала Прием в регистре 5 сдвига. Сигнал Прием формируется импульсом с выхода 2.2 блока 2 синхронизации при условии, что содержимое регистра 5 сдвига равно нулю. Элемент 11 задержки устраняет возможные состязания по контуру регистр 5 сдвига - элемент ИЛИ 7 - элемент НЕ 10 - элемент И 9. Величина задержки элемента 11 должна быть больше, чём время приема информации в регистр 5 сдвига. На практике функции элемента 11 могут выполнять паразитные задержки второго элемента ИЛИ 7 и элемента НЕ 10.

фиг. 4 обозначены: С, коды на выходе генератора

С

i

1

псевдослучайных кодов в тактах 1, 2, ..., 7 соответственно; Д - величина задержки элемента 11 задержки; k - длина команды.

Для пояснения работы формирователя тестов воспользуемся следующей структурой команд микропроцессора. Команды микропроцессора имеют переменную длину и могут состоять из 1, 2, 3 и т.д. слов. Например, микропроцессоры типа INTEL 8080, К580 имеют одно-, двух-, грехсловные команды, где длина одного слова составляет 8 бит (один байт). Независимо от типа команды код выполняемой операции, длина самой команды и режимы адресации операндов задаются в ее первом слове. Следующие слова команды содержат данные, участвующие в операциях, либо их адреса. Назовем первое слово команды кодом команды.

Формирователь работает следующим образом,

В исходном состоянии все элементы памяти установлены в нулевое состояние (цепи начальной установки не показаны) . По сигналу пуска триггер 16 блока 2 (фиг. 3) устанавливается в единичное состояние и включает генератор 17, который начинает формирование тактовых импульсов на выходах 2.1 и 2.2.

По каждому тактовому импульсу с выхода 2.1 блока 2 осуществляется сдвиг информации в регистре 12 сдвига генератора 1 и формирование нового кода случайного числа на группе выходов генератора 1 (фиг. 2).

Каждый случайный код с выхода генератора 1 (фиг. 1) поступает на входы дешифратора 3 запрещенных комбинаций. При этом возможны следующие случаи.

Случай 1. Случайный код с выхода генератора 1 не является кодом коман- ды (код С,,, либо С j на временной диаграмме фиг. 4).

При этом на всех выходах дешифратора 3 устанавливается значение О. Содержимое регистра 5 сдвига в исходном состоянии было нулевым, поэтому после импульса сдвига с выхода 2.1 содержимое регистра также остается нулевым. При этом на выходе элемента ИЛИ 7 устанавливается значение О, на выходе элемента НГ 10 - значение 1, на выходе элемента ИЛИ 6 - значение О. Импульс с выхода 2.2 блока 2 через элемент И 9 поступает на управляющий вход Прием регистра 5 сдвига, однако содержимое регистра 5 остается нулевым, так как все выходы дешифратора 3 установлены в О. Поскольку на выходе элемента ИЛИ ( установлено значение О, на выходе элемента И 8 сохраняется нулевое значение, блокирующее запись случайного кода с выхода генератора 1 в регистр 4 теста (фиг. 1).

Таким образом, если при формировании первого слова команды на выходе генератора 1 вырабатывается случайный код, который не является кодом

;,ез элемент И 8 на вход Прием регистра 4 теста. При этом в регистр $ сдвига записывается информация с выходов дешифратора 3, т.е. Г1 записывается вк-й разряди О -в остальные разряды, а в регистр 4 теста записывается код команды, который с выхода регистра 4 теста поступает на выход

формирователя.

Изменение содержимого регистра 5 сдвига приводит к тому, что выход элемента ИЛИ 7 устанавливается в 1, однако это не сказывается на прохож5 денни импульса с выхода 2.2 на вход Прием регистра 5, поскольку сигнал с выхода элемента ИЛИ 7 поступает на вход элемента НЕ 10 через задержкуД

(фиг. 4). задаваемую элементом 11

задержки.

К моменту поступления импульса с выхода 2.1 блока 2 значение 1 с выхода элемента ИЛИ 7 через элемент 11 задержки и элемент НЕ 10 устанавпинает выход элемента И 9 в О. Импульс с выхода 2.1 блока 2 поступает на управляющий вход Сдвиг регистра 5 сдвига. Содержимое регистра 5 сдвигается. При этом 1 переходит из

разряда k в разряд (k-1).

Очевидно, если длина команды k 1 , после сдвига содержимое регистра 5 сдвига становится равным нулю, выход элемента ИЛИ 7 устанавливается

О1

а выход элемента НЕ 10 - в

П -. И

На этом цикл формирования очередной команды завершен и формирователь возвращается в исходное состояние. Начинается цикл формирования

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь тестов | 1985 |

|

SU1291986A1 |

| Формирователь тестов | 1987 |

|

SU1552185A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1555705A1 |

| Формирователь тестов | 1989 |

|

SU1661769A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1334139A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2010316C1 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

Изобретение относится к вычислительной технике, в частности к средствам автоматического контроля микропроцессорных устройств. Целью изобретения является повышение быстродействия формирователя. Это достигается введением в формирователь, содержащий блок синхронизации, генератор псевдослучайных кодов, дешифратор запрещенных комбинаций и регистр теста, регистра сдвига, двух элементов ИЛИ и элемента задержки. Очеред- йая команда формируется пословно путем выделения из случайных чисел, вырабатываемых генератором псевдослучайных кодов, допустимых команд. В качестве следующих слов команды используются любые случайные числа. Выявление допустимых кодов команд и дешифрация длины команды позволяют исключить этап анализа форматов команд. 4 ил. с S (Л

команды, содержимое регистра 5 сдвига 40 следующей команды. остается нулевым, а случайный код не записывается в регистр 4 теста.

Случай 2. Случайный код с выхода генератора 1 является кодом команды

Если же длина к после сдвига содер сдвига неравно нул

(код С, либо Cq. на временной диаграм-45 РазРяД установлен в 1 . При этом ме фиг. 4). При этом на k-м выходе, 1 вчхода элемента ИЛИ 7 блокируме

где k - длина команды, дешифратора 3 устанавливается значение 1, а на остальных выходах - значение О. При этом на выходе элемента ИЛИ 6 устанавливается значение 1. Поскольку в исходном состоянии содержимое регистра 5 сдвига равно нулю, импульс с выхода 2.1 блока 2 не изменяет его содержимого. При этом выход элемента ИЛИ 7 установлен в О, элемента НЕ 10 - в 1. Импульс с выхода 2.2 блока 2 через элемент И 9 поступает на вход Прием регистра 5 сдвига и че50

55

от поступление импульса с выхода 2.2 блока 2 на вход Прием регистра 5 сдвига и разрешает поступление рассматриваемого импульса через элемент И 8 на вход Прием регистра 4 теста. Таким образом, если длина команды k 1, второе после кода команды случайное число с выхода генератора 1 записывается в регистр 4 теста (код С на временной диаграмме фиг. 4).

Очередной импульс с выхода 2.1 блока 2 поступает на управляющий вход Сдвиг регистра 5 сдвига. При

следующей команды.

Если же длина команды k ; 1, то после сдвига содержимое регистра 5 сдвига неравно нулю, так как (k-D-й

РазРяД установлен в 1 . При этом 1 вчхода элемента ИЛИ 7 блокиру

от поступление импульса с выхода 2.2 блока 2 на вход Прием регистра 5 сдвига и разрешает поступление рассматриваемого импульса через элемент И 8 на вход Прием регистра 4 теста. Таким образом, если длина команды k 1, второе после кода команды случайное число с выхода генератора 1 записывается в регистр 4 теста (код С на временной диаграмме фиг. 4).

Очередной импульс с выхода 2.1 блока 2 поступает на управляющий вход Сдвиг регистра 5 сдвига. При

этом в регистре 5 1 из разряда (k-1) переходит в разряд (k-2).

Очевидно, если длина команды k . 2, то после сдвига содержимое ре- гистрй 5 сдвига становится равным нулю, выход элемента ИЛИ 7 устанавливается в О, а выход элемента НЕ 10 - в 1. На этом цикл формирования команды завершен, формирователь возвращается в исходное состояние и начинается цикл формирования следующей команды.

Если же длина команды k 2, то после сдвига содержимое регистра 5 сдвига отлично от нуля и значение 1 с выхода элемента ИЛИ 7 аналогичным образом вновь блокирует прохождение импульса с выхода 2.2 на вход Прием регистра 5 сдвига и разреша- ет его прохождение на вход Прием регистра 4 теста. В результате в регистр 4 теста записывается третье слово формируемой команды (код С$) на временной диаграмме фиг. 4).

С приходом с выхода 2.1 блока 2 очередного импульса в регистре 5 вно выполняется сдвиг и т.д. до тех пор, пока содержимое регистра 5 не станет равным нулю. При этом в регистре 4 теста поочередно будут записаны и выданы на выход формирователя, перво второе ... k-e слова тест-команды. После выдачи k-ro слова формировател вновь возвращается в исходное сое- тояние.

Далее очередное случайное число (код С7 на временной диаграмме фиг.4 с выхода генератора 1 вновь анализируется дешифратором 3 и аналогично описанному формируется очередная команда.

При необходимости прекращения работы формирователь отключается сиг налом останова, подаваемым на вход элемента И 18 (фиг. 3). При этом триггер 16 устанавливается в нулевое .состояние, генератор 17 выключается и прекращает выдачу тактовых импуль- сов на выходы 2.1 и 2.2.

Временные диаграммы работы формирователя (фиг. 4) представлены для случая, когда случайный код C на

выходе генератора 1 не является допустимым крдом команды, код, С является кодом команды с длиной k 1, код Cj не является допустимым кодом команды, код С является кодом команды с длиной k 3 и поэтому следующие коды С g- и Cg на выходе генератора 1 используются в качестве второго и третьего слов формируемой тест-команды, код С7 является кодом команды,.

Формула изобретения

Формирователь тестов, содержащий блок синхронизации, генератор псевдослучайных кодов, дешифратор запрещенных комбинаций и регистр теста, причем первый выход блока синхронизации соединен с входом запуска генератора псевдослучайных кодов, пыходы которого соединены с информационными входами дешифратора запрещенных комбинаций, выход регистра теста является выходом формирователя, отличающийся тем, что, с целью повышения быстродействия, формирователь содержит регистр сдвига, два элемента ИЛИ, два элемента И, элемент НЕ и элемент задержки, причем выходы генератора псевдослучайных кодов соединены с информационными входами регистра теста, группа выходов дешифратора запрещенных комбинаций соединена с группой информационных входов регистра сдвига и группой входов первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, выход которого соединен с входом синхронизации регистра теста, группа разрядных выходов регистра сдвига соединена с группой входов второго элемента ИЛИ, выход которого соединен с входом первого элемента ИЛИ и входом элемента задержки, выход которого соединен с входом элемента НЕ, выход которого соединен с первым входом второго элемента И, выход которого соединен с входом разрешения регистра сдвига, вход синхронизации которого соединен с первым выходом блока синхронизации, второй выход которого соединен с вторыми входами первого и второго элементов И.

Д

10

Ь

ш

в

Фае.1

Фиё.1

| Устройство для статистического контроля логических блоков | 1974 |

|

SU527707A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-03-15—Публикация

1988-10-10—Подача