Изобретение относится к вычислительной технике и может быть использовано автономно или в составе многопроцессорных вычислительных комплексов для обработки информации в реальном времени.

Известна управляющая вычислительная система, содержащая два процессора, оперативное запоминающее устройство, постоянное запоминающее устройство, мультиплексор, блок управления доступом и блок управления, причем первый управляющий вход-выход блока управления доступом соединен с управляющими входами-выходами первого процессора, оперативного запоминающего устройства и блока управления, а адресный вход-выход блока управления доступом соединен с первым управляющим входом-выходом второго процессора и адресными входами выходами постоянного запоминающего устройства.

Недостатком такой системы является низкое быстродействие вследствие того, что во время цикла шины - обращения процессоров к оперативному запоминающему устройству, который делится довольно долго - около 2-8 мкс, вычисления не выполняются и система фактически простаивает.

Наиболее близкой по технической сущности к предлагаемой является вычислительная система, построенная на основе микропроцессорного комплекта К1810, содержащая генератор тактовых импульсов,

N

1с РЬ

|0

центральный процессор, сопроцессор, контроллер шины, регистр-защелку, приемопередатчик и процессор ввода-вывода, причем выход мультиплексной шины центрального процессора соединен с информа- ционными входами сопроцессора, процессора ввода-вывода, регистр-защелки и приемопередатчика, выход шины состояния центрального процессора подключен к соответствующим входам сопроцессора, процессора ввода-вывода и контроллера шины, входы синхронизации центрального процессора, сопроцессора, контроллера шины и процессора ввода-вывода объединены и подсоединены к выходу генератора импульсов, выходы готовности и сброса которого подключены к входам готовности и сброса центрального процессора, сопроцессора и процессора ввода-вывода, два двунаправленных вывода запрос/разрешение доступа к магистрали высшего и низшего приоритетов подсоединены к соответствующим входам процессора ввода- вывода и сопроцессора соответственно, вход Проверка соединен с соответствующим выходом сопроцессора, вход настройки центрального процессора на максимальный режим и вход разрешения вывода регистра-защелки соединены с нулевой шиной системы, а вход стробирова- ния адреса контроллера шины подключен к входу стробирования регистра-защелки, к входу старшего разряда которого подсоединен выход разрешения старшего байта центрального процессора. .

Недостатком такой вычислительной системы является низкое быстродействие, обусловленное тем, что в цикле шины, т.е. при считывании информации из оперативного запоминающего устройства в центральный процессор или сопроцессор, длительность которого составляет 800 не с момента подачи адреса на шину, в вычислительной системе не выполняются никакие арифметические и логические операции.

Цель изобретения - увеличение быстродействия вычислительной системы за счет организации параллельной обработки данных в цикле шины центрального процессора и сокращение объема памяти для хранения сервисных программ.

Указанная цель достигается тем, что в устройство, содержащее центральный процессор, сопроцессор, процессор ввода-вывода, контроллер шины, регистр-защелку, генератор тактовых импульсов, приемопередатчик и блок оперативной памяти, причем информационные входы-выходы центрального процессора подключены через мультиплексорную магистраль к информационным входам-выходам сопроцессора, процессора ввода-вывода, к информационным входам-выходам первой группы приемопередатчика и к информационным

входам первой группы регистра-защелки, первый выход состояния центрального процессора подключен к первому управляющему входу сопроцессора, к управляющим входам процессора ввода-вывода и контроллера ши0 ны, второй выход состояния центрального процессора подключен к второму управляющему входу сопроцессора, первый выход генератора тактовых импульсов подключен к входам синхронизации центрального про5 цессора , сопроцессора, процессора ввода- вывода и контроллера шины, выход признака готовности и выход признака установки в О генератора тактовых импульсов подключены соответственно к входам

0 признака готовности и к входам сброса центрального процессора, сопроцессора и процессора ввода-вывода, первый и второй входы-выходы запроса/разрешения доступа к магистрали центрального процессора

5 подключены соответственно к входам-выходам запроса/разрешения доступа к магистрали сопроцессора и процессора ввода-вывода, выход признака обращения к центральному процессору сопроцессора

0 подключен к входу проверки признака ожидания центрального процессора, первый и второй управляющие входы системы подключены соответственно к первому и второму входам режима генератора тактовых

5 импульсов, вход нулевого потенциала системы подключен к входу режима центрального процессора и к входу признака разрешения вывода регистра-защелки, первый выход контроллера шины подключен к

0 входу стробирования регистра-защелки, второй информационный вход которого подключен к выходу признака разрешения старшего байта центрального процессора, выходы регистра-защелки через адресную

5 магистраль подключены к адресным входам блока оперативной памяти, информационные входы-выходы второй группы приемопередатчика через магистраль данных подключены к информационным входам-вы0 ходам блока оперативной памяти, первый и второй выходы контроллера шины через магистраль управления подключены к входам записи и чтения блока оперативной памяти, дополнительно введены блок управления,

5 блок постоянной памяти, блок регистров, блок вычисления квадратного корня и группа элементов И, причем выходы регистра через адресную магистраль подключены к адресным входам блока постоянной памяти, к входам выборки первой группы блока регистров и к входам группы режима блока управления, информационные входы-выходы второй группы приемопередатчика через магистраль данных подключены к выходам блока постоянной памяти, к информационным вхо- дам блока регистров и к информационным входам блока вычисления квадратного корня, выходы которого подключены соответственно к первым входам элементов 1/1 группы, выходы которых через мультиплексорную магистраль подключены к информационным входам-выходам центрального процессора, сопроцессора, процессора ввода-вывода, к информационным входам- выходам первой группы приемопередатчика и к информационным входам первой группы регистра-защелки, с третьего по пятый выходы контроллера шины через магистраль управления подключены соответственно к входу чтения блока постоянной памяти, к входу записи и чтения блока регистров, шестой и седьмой выходы контроллера шины подключены соответственно к первому и второму входам режима блока управления, выходы с первого по девятый которого под- ключены соответственно к первому и второму управляющим входам приемопередатчика, к вторым входам элементов И группы, к первому и второму входам выборки второй группы блока регистров, к первому и второму вхо- дам выборки блока оперативной памяти, к первому и второму входам выборки блока постоянной памяти, вход нулевого потенциала устройства подключен к входу нулевого потенциала блока вычисления квадратного корня, причем блок управления содержит дешифратор, четыре элемента ИЛИ, шесть элементов И и два элемента НЕ, причем первый и второй входы режима группы блока подключены к входам дешифратора, тре- тий вход режима группы блока подключен к первым входам первого, второго и третьего элементов И, четвертый вход режима группы блока подключен к первым входам четвертого, пятого и шестого элемента И, первый вход режима блока подключен к первому входу первого элемента ИЛИ, выход которого подключен к первому выходу блока, второй вход режима которого подключен к входу первого элемента НЕ, выход которого подключен к первым входам второго и третьего элементов ИЛ И, выходы которых подключены соответственно к второму и к третьему выходам блока, первый выход дешифратора подключен к вто- рым входам третьего и шестого элементов И, второй выход дешифратора подключен к первому входу четвертого элемента ИЛИ, к вторым входам первого и второго элементов И и входу второго элемента НЕ, выход

которого подключен к второму входу третьего элемента ИЛИ, выход четвертого элемента ИЛИ подключен к вторым входам первого и четвертого элементов И, выходы которых подключены соответственно к пятому и четвертому выходам блока, третий выход дешифратора подключен к второму входу четвертого элемента ИЛИ, четвертый выход дешифратора подключен к вторым входам второго и пятого элементов И, выходы которых подключены соответственно к седьмому и шестому выходам блока, выходы шестого и третьего элементов И подключены соответственно к восьмому и девятому выходам блока.

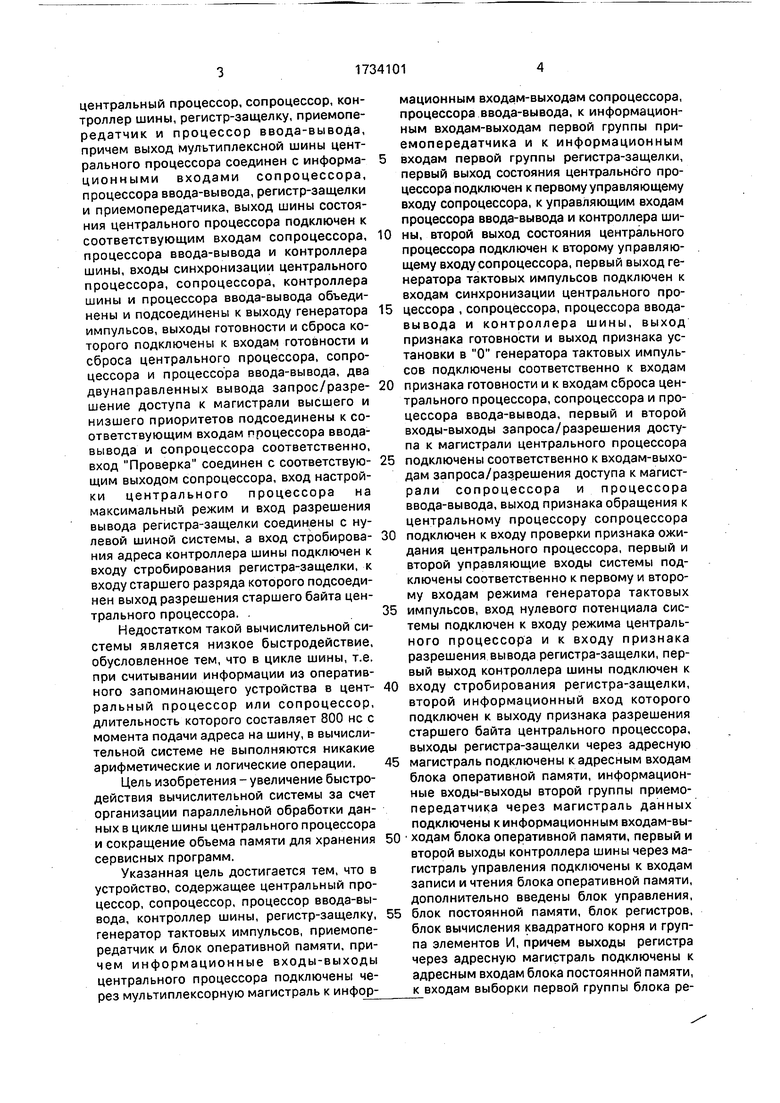

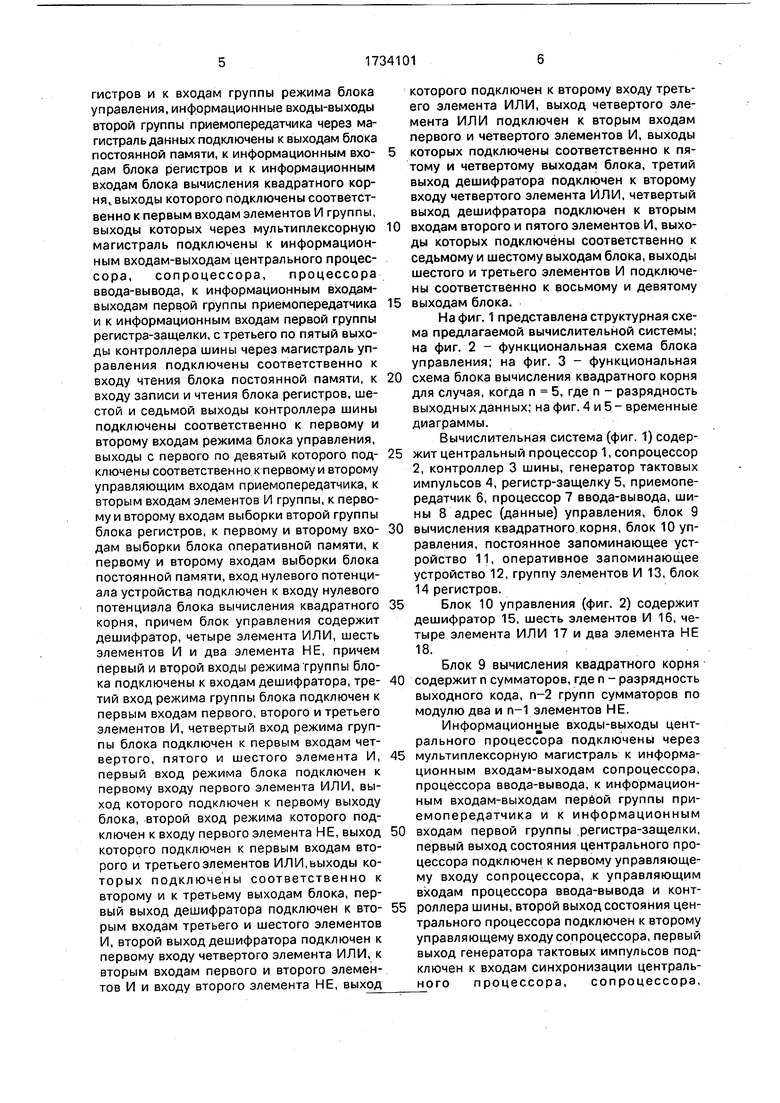

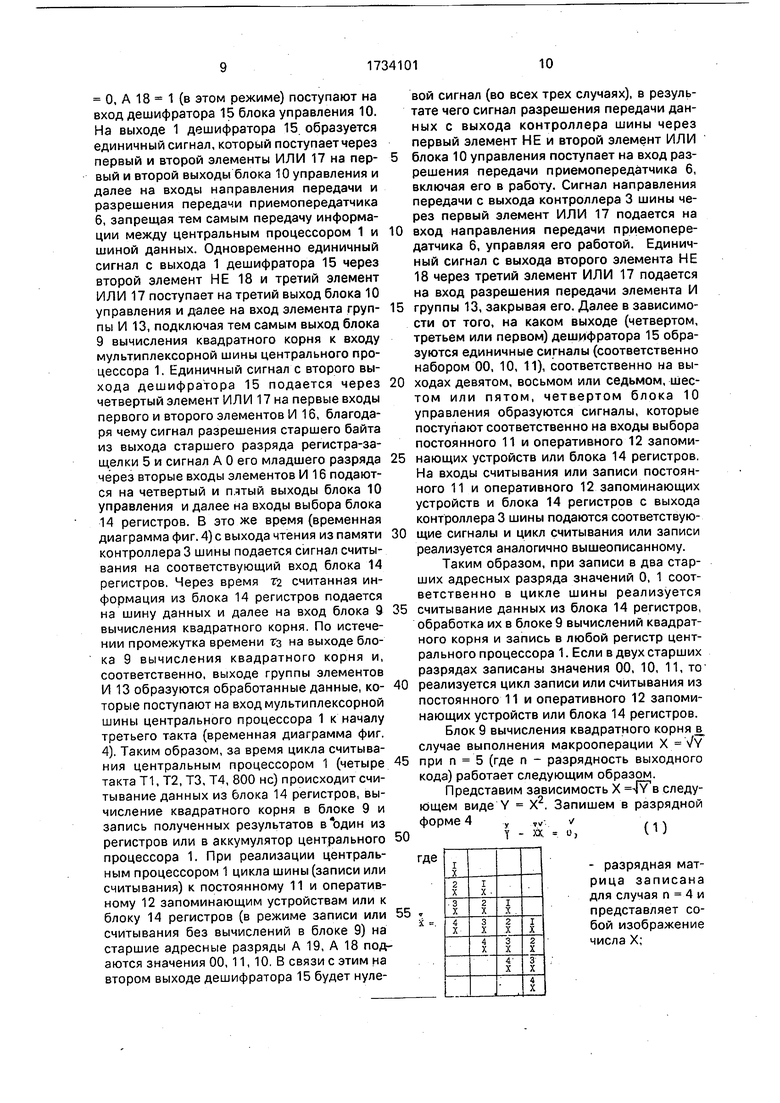

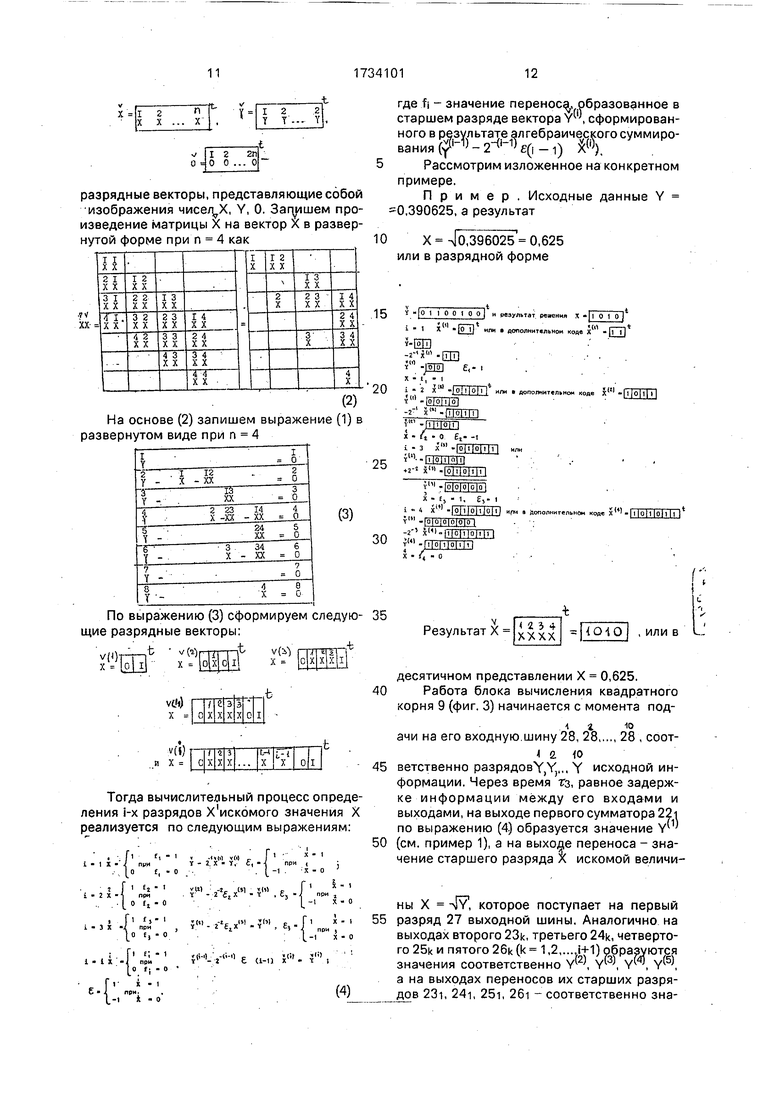

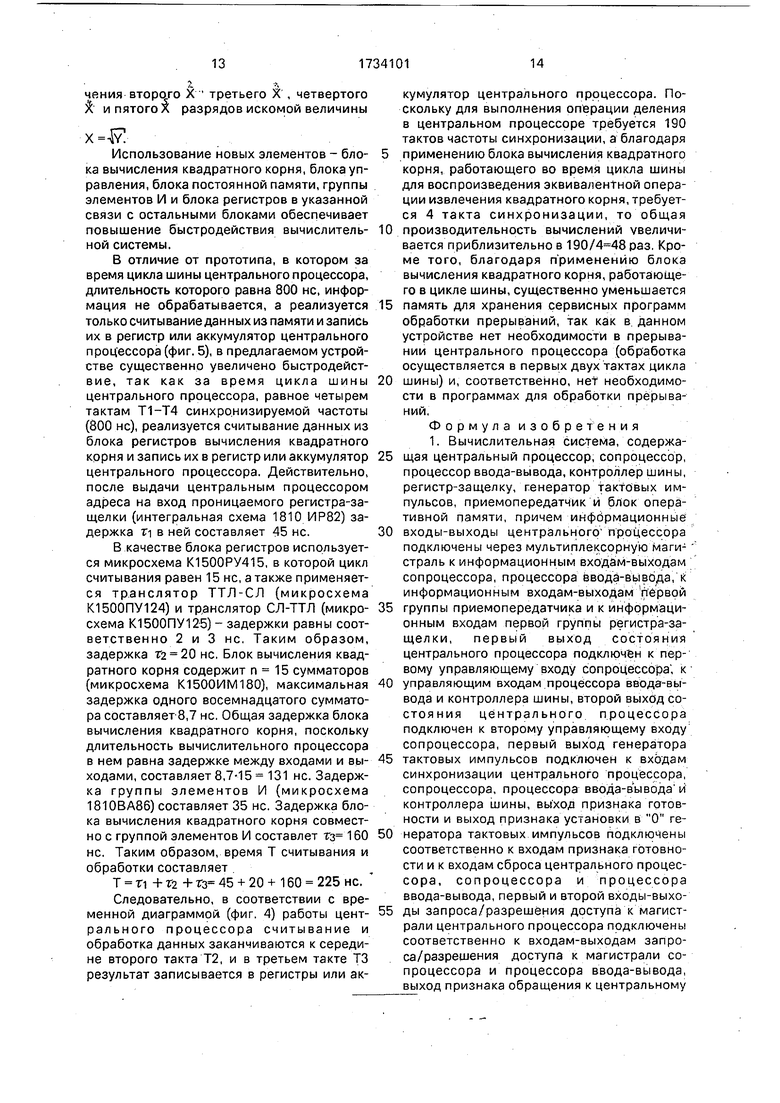

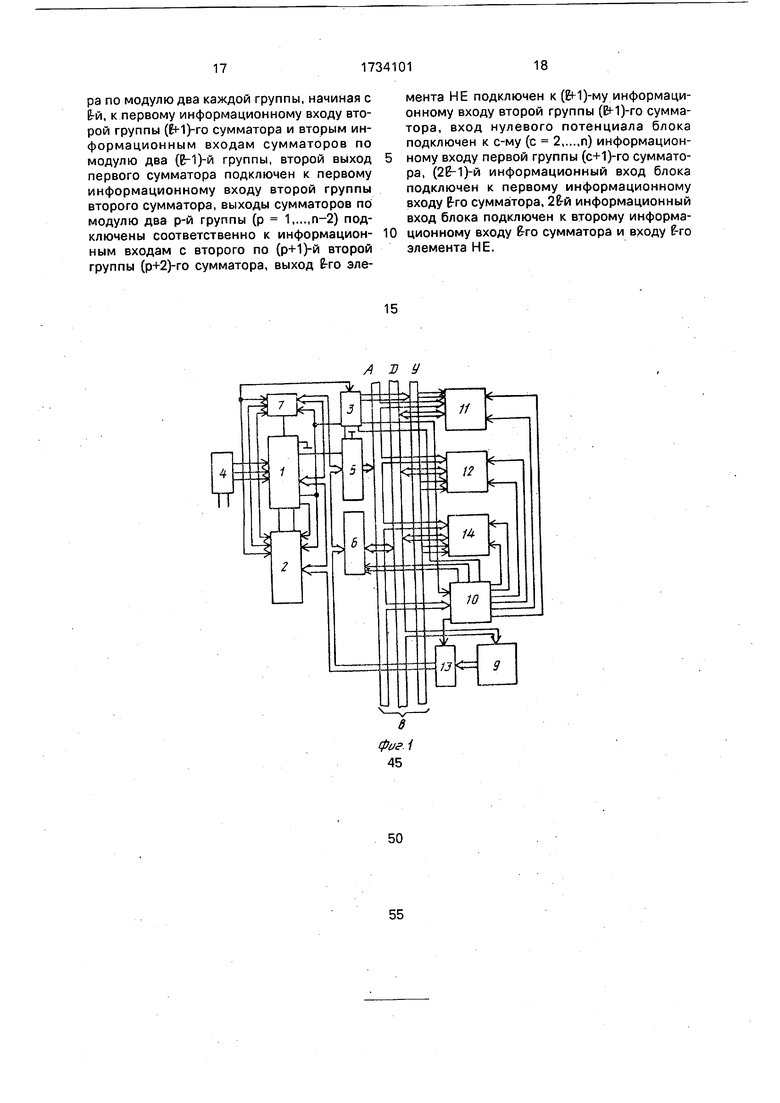

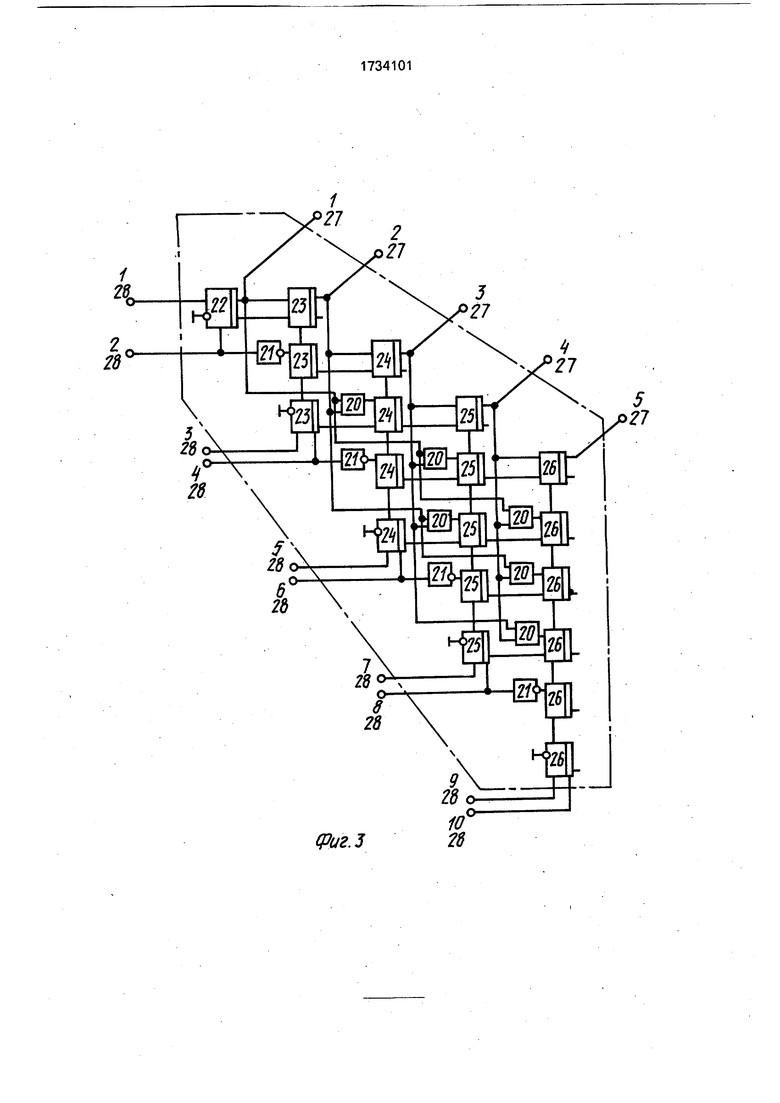

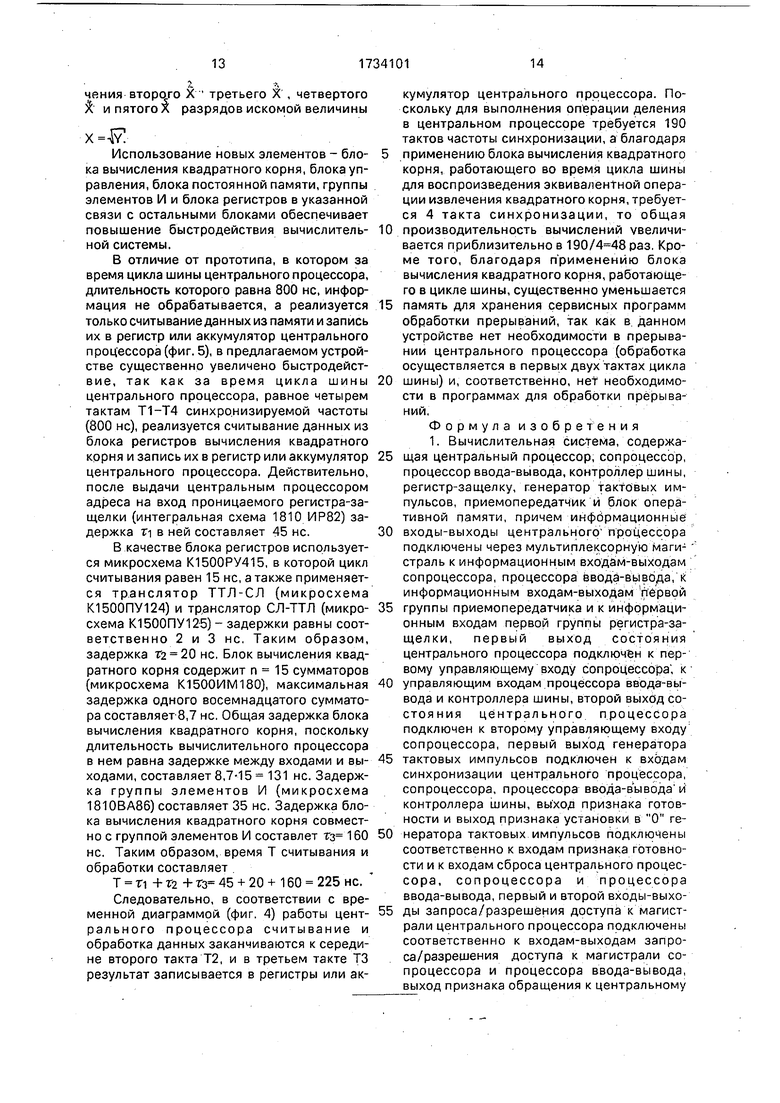

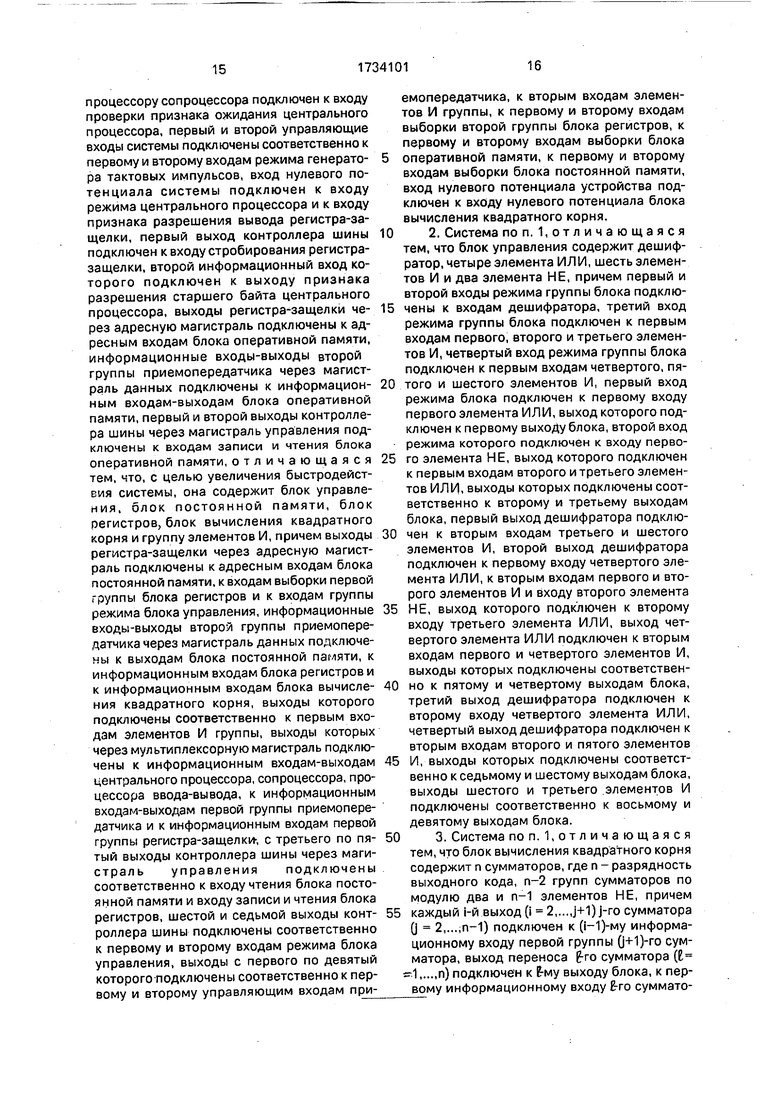

На фиг. 1 представлена структурная схема предлагаемой вычислительной системы; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - функциональная схема блока вычисления квадратного корня для случая, когда п 5, где п - разрядность выходных данных; на фиг. 4 и 5 - временные диаграммы.

Вычислительная система (фиг. 1) содержит центральный процессор 1, сопроцессор 2, контроллер 3 шины, генератор тактовых импульсов 4, регистр-защелку 5, приемопередатчик 6, процессор 7 ввода-вывода, шины 8 адрес (данные) управления, блок 9 вычисления квадратного корня, блок 10 управления, постоянное запоминающее устройство 11, оперативное запоминающее устройство 12, группу элементов И 13, блок 14 регистров.

Блок 10 управления (фиг. 2) содержит дешифратор 15, шесть элементов И 16, четыре элемента ИЛИ 17 и два элемента НЕ 18.

Блок 9 вычисления квадратного корня содержит п сумматоров, где п - разрядность выходного кода, п-2 групп сумматоров по модулю два и п-1 элементов НЕ.

Информационные входы-выходы центрального процессора подключены через мультиплексорную магистраль к информационным входам-выходам сопроцессора, процессора ввода-вывода, к информационным входам-выходам первой группы приемопередатчика и к информационным входам первой группы регистра-защелки, первый выход состояния центрального процессора подключен к первому управляющему входу сопроцессора, к управляющим входам процессора ввода-вывода и контроллера шины, второй выход состояния центрального процессора подключен к второму управляющему входу сопроцессора, первый выход генератора тактовых импульсов подключен к входам синхронизации центрального процессора, сопроцессора,

процессора ввода-вывода и контроллера шины, выход признака готовности и выход признака установки в О генератора тактовых импульсов подключены соответственно к входам признака готовности и к входам сброса центрального процессора, сопроцессора и процессора ввода-вывода, первый и второй входы-выходы запроса/разрешения доступа к магистрали центрального процессора подключены соответственно к входам-выходам запроса/разрешения доступа к магист- рали сопроцессора и процессора ввода-вывода, выход признака обращения к центральному процессору сопроцессора подключен к входу проверки признака ожидания центрального процессора, первый и второй управляющие входы системы подключены соответственно к первому и второму входам режима генератора тактовых импульсов, вход нулевого потенциала системы подключен к входу режима центрального процессора и входу признака разрешения вывода регистра-защелки, первый выход контроллера шины подключен к входу стробирования регистра-защелки, второй информационный вход которого подключен к выходу признака разрешения старшего байта центрального процессора, выходы регистра-защелки через адресную магистраль подключены к адресным входам блока оперативной памяти, информационные входы- выходы второй группы приемопередатчика через магистраль данных подключены к информационным входам-выходам блока оперативной памяти, первый и второй выход контроллера шины через магистраль управления подключены к входам записи и чтения блока оперативной памяти. Выходы регистра-защелки через адресную магистраль подключены к адресным входам блока постоянной памяти, к входам выборки первой группы блока регистров и к входам группы режима блока управления, информационные входы-выходы второй группы приемопередатчика через магистраль данных подключены к выходам блока постоянной памяти, к информационным входам блока регистров и к информационным входам блока вычисления квадратного корня, выходы которого подключены соответственно к первым входам элементов И группы, выходы которых через мультиплексорную магистраль подключены к информационным входам-выходам центрального процессора, сопроцессора, процессора ввода-вывода, к информационным входам-выходам первой группы приемопередатчика и к информационным входам первой группы регистра-защелки, с третьего по пятый выходы контроллера шины через магистраль управления подключены соответственно к входу чтения блока постоянной памяти, к входу записи и чтения блока регистров, шестой и седьмой выходы контроллера шины подключены соответственно к первому и второму входам режима блока управления, выходы с первого по девятый которого подключены соответственно к первому и второму управляющим входам приемопередатчика, к вторым

входам элементов 1/1 группы, к первому и второму входам выборки второй группы блока регистров, к первому и второму входам выборки блока оперативной памяти, к первому и второму входам выборки блока постоянной

памяти, вход нулевого потенциала устройства подключен к входу нулевого потенциала блока вычисления квадратного корня.

Каждый i-й выход (i 2j+1)j-ro сумматора ( 2,...,п-1) подключен к(Ы)-муинформационному входу первой группы (j+1)-ro сумматора, выход переноса Е-ro сумматора

(I- 1п) подключен к 5-му выходу блока, к

первому информационному входу -го сумматора по модулю два каждой группы, начиная с Е-й, к первому информационному входу второй группы (Е+1)-го сумматора и к вторым информационным входам сумматоров по модулю два (М)-й группы, второй выход первого сумматора подключен к первому

информационному входу второй группы второго сумматора, выходы сумматоров по модулю два р-й группы(р 1п-2) подключены соответственно к информационным входам с второго по (р+1)-й второй группы

(р+2)-го сумматора, выход Е-го элемента НЕ подключен к (Е+1)-му информационному входу второй группы (ЕИ)-го сумматора, вход нулевого потенциала блока подключен к с- му (с 2,...,п) информационному входу второй

группы (с+1)-го сумматора, ()-й информационный вход блока подключен к первому информационному входу Е-ro сумматора, 2 t-й информационный вход блока подключен к второму информационному входу Е-го сумматора и к входу Е-го элемента НЕ.

Вычислительная система (фиг. 1) работает следующим образом.

В режиме работы блока 9 вычисления квадратного корня во время цикла считывания центрального процессора 1 в соответствии с временной диаграммой (фиг. 4) реализуется выдача адреса с выхода муль- типлексорной шины процессора 1 на вход проницаемого регистра-защелки 5. Через

время TI, равное задержке сигнала в регистре-защелке 5, с его выхода значение адреса поступает на шину адреса и далее на адресный вход блока 14 регистров. Кроме того, значения двух старших разрядов А 19

О, А 18 1 (в этом режиме) поступают на вход дешифратора 15 блока управления 10. На выходе 1 дешифратора 15 образуется единичный сигнал, который поступает через первый и второй элементы ИЛИ 17 на первый и второй выходы блока 10 управления и далее на входы направления передачи и разрешения передачи приемопередатчика б, запрещая тем самым передачу информации между центральным процессором 1 и шиной данных. Одновременно единичный сигнал с выхода 1 дешифратора 15 через второй элемент НЕ 18 и третий элемент ИЛИ 17 поступает на третий выход блока 10 управления и далее на вход элемента группы И 13, подключая тем самым выход блока 9 вычисления квадратного корня к входу мультиплексорной шины центрального процессора 1. Единичный сигнал с второго выхода дешифратора 15 подается через четвертый элемент ИЛИ 17 на первые входы первого и второго элементов И 16, благодаря чему сигнал разрешения старшего байта из выхода старшего разряда регистра-защелки 5 и сигнал А 0 его младшего разряда через вторые входы элементов И 16 подаются на четвертый и пятый выходы блока 10 управления и далее на входы выбора блока 14 регистров. В это же время (временная диаграмма фиг. 4) с выхода чтения из памяти контроллера 3 шины подается сигнал считывания на соответствующий вход блока 14 регистров. Через время Т2 считанная информация из блока 14 регистров подается на шину данных и далее на вход блока 9 вычисления квадратного корня. По истечении промежутка времени Тз на выходе блока 9 вычисления квадратного корня и, соответственно, выходе группы элементов И 13 образуются обработанные данные, ко- торые поступают на вход мультиплексорной шины центрального процессора 1 к началу третьего такта (временная диаграмма фиг. 4). Таким образом, за время цикла считывания центральным процессором 1 (четыре такта Т1, Т2, ТЗ, Т4, 800 не) происходит считывание данных из блока 14 регистров, вычисление квадратного корня в блоке 9 и запись полученных результатов из регистров или в аккумулятор центрального процессора 1. При реализации центральным процессором 1 цикла шины (записи или считывания) к постоянному 11 и оперативному 12 запоминающим устройствам или к блоку 14 регистров (в режиме записи или считывания без вычислений в блоке 9) на старшие адресные разряды А 19, А 18 подаются значения 00, 11, 10. В связи с этим на втором выходе дешифратора 15 будет нуле

0

5

0

5

0 0 5 5

5

0

вой сигнал (во всех трех случаях), в результате чего сигнал разрешения передачи данных с выхода контроллера шины через первый элемент НЕ и второй элемент ИЛИ блока 10 управления поступает на вход разрешения передачи приемопередатчика 6, включая его в работу. Сигнал направления передачи с выхода контроллера 3 шины через первый элемент ИЛИ 17 подается на вход направления передачи приемопередатчика б, управляя его работой. Единичный сигнал с выхода второго элемента НЕ 18 через третий элемент ИЛИ 17 подается на вход разрешения передачи элемента И группы 13, закрывая его. Далее в зависимости от того, на каком выходе (четвертом, третьем или первом) дешифратора 15 образуются единичные сигналы (соответственно набором 00, 10, 11), соответственно на выходах девятом, восьмом или седьмом, шестом или пятом, четвертом блока 10 управления образуются сигналы, которые поступают соответственно на входы выбора постоянного 11 и оперативного 12 запоминающих устройств или блока 14 регистров. На входы считывания или записи постоянного 11 и оперативного 12 запоминающих устройств и блока 14 регистров с выхода контроллера 3 шины подаются соответствующие сигналы и цикл считывания или записи реализуется аналогично вышеописанному.

Таким образом, при записи в два старших адресных разряда значений 0, 1 соответственно в цикле шины реализуется считывание данных из блока 14 регистров, обработка их в блоке 9 вычислений квадратного корня и запись в любой регистр центрального процессора 1. Если в двух старших разрядах записаны значения 00, 10, 11, то реализуется цикл записи или считывания из постоянного 11 и оперативного 12 запоминающих устройств или блока 14 регистров.

Блок 9 вычисления квадратного корня случае выполнения макрооперации X /Y при п 5 (где п - разрядность выходного кода) работает следующим образом.

Представим зависимость X следующем виде Y X . Запишем в разрядной форме 4 у vv v Т - хх о,

О)

- разрядная матрица записана для случая п 4 и представляет собой изображение числа X;

о

разрядные векторы, представляющие собой изображения чисел Х, Y, 0. Запишем произведение матрицы X на вектор X в развернутой форме при п 4 как

где fj - значение переносу, образованное в старшем разряде вектора Y, сформированного в результате алгебраического суммиро- вания (f-Ч 2-HJ Ј(,) Х«).

Рассмотрим изложенное на конкретном примере.

Пример. Исходные данные Y -0,390625, а результат

Ю ,396025 0,625 или в разрядной форме

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1989 |

|

SU1725224A1 |

| Процессор для обработки массивов данных | 1985 |

|

SU1293737A1 |

| Устройство для сопряжения двух процессоров | 1990 |

|

SU1762309A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1269151A1 |

| Устройство для вычисления квадратного корня | 1986 |

|

SU1359778A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

Изобретение может быть использовано для повышения производительности вычислений как автономно, так и в составе многомашинных комплексов. Цель изобретения увеличение быстродействия вычислительной системы за счет организации параллельной обработки данных в цикле шины центрального процессора. Поставленная цель достигается тем, что система содержит центральный процессор 1, сопроцессор 2, контроллер шины 3, генератор тактовых импульсов 4, регистр-защелку 5, приемопередатчик 6, процессор 7 ввода-вывода, шины 8 адрес (данные) управления, блок 9 вычисления квадратного корня, блок 10 управления, блок 11 постоянной памяти, блок 12 оперативной памяти, группу элементов И 13 и блок 14 регистров. Блок вычисления квадратного корня выполнен в виде однородной параллельной структуры, обеспечивающей извлечение квадратного корня во время обращения центрального процессора к оперативному запоминающему устройству. 2 з.п. ф-лы, 5 ил. Ё

(2)

На основе (2) запишем выражение (1) в развернутом виде при п 4

Тогда вычислительный процесс определения 1-х разрядов Х искомого значения X реализуется по следующим выражениям:

. f i f, -1 , .„„, « . Г -

I - 1 I 1 пвиT-2X-Y, С, -Ч при ,:

о f, - о( -1 х - о

i-.x-f1 .Р.е,.

о ft-оL-IX-O

.,4 -( при5 1 , ; -2- Јlx -;.Ј,. f, - О -1X-0

I Г fi 1v(i-0 -O-il «(,

i -| лриГ - 2( Ј (1-1) х1. и i

L° fi -°

I:,

i 1 X

Y -|0 1 I О О I 0 о| и результат ишемия X -|| О 1 QJ i 1 X |0 || или дополнительной коде XW -|l ||

v-HED

-г хш .ТТЛ .

i -JUS E,- i

X - I, - I i-2 х -lojlloll I или , допопнительнон коде X(t| -|. 1°М |

-;- х - -ДЖШ,

I -ШЖШ х - 4 . оег- -1

i - 3 X1 -|0|Ч°| М | или

iu --nio|i|oli|

2-« х « .ртттоттт

ипи дополнительном коде X 11 |р|1 lOJHl

Результат X

, или в

десятичном представлении X 0,625. Работа блока вычисления квадратного корня 9 (фиг. 3) начинается с момента под4 410

ачи на его входную шину 28, 2828 , соот а о

ветственно разрядовУУ.,, Y исходной информации. Через время тз, равное задержке информации между его входами и выходами, на выходе первого сумматора 22i по выражению (4.) образуется значение

(см. пример 1), а на выходе переноса - значение старшего разряда X искомой величины X -47, которое поступает на первый разряд 27 выходной шины. Аналогично на выходах второго 23k, третьего 24k, четвертого 25k и пятого 26k (k 1,2,...,i+1) образуются значения соответственно , Y®, Y, Y®, а на выходах переносов их старших разрядов 23i, 24i, 25ч, 26i - соответственно знагчения второго X третьего X , четвертого

%. и пятого л разрядов искомой величины

Использование новых элементов - блока вычисления квадратного корня, блока управления, блока постоянной памяти, группы элементов И и блока регистров в указанной связи с остальными блоками обеспечивает повышение быстродействия вычислительной системы.

В отличие от прототипа, в котором за время цикла шины центрального процессора, длительность которого равна 800 не, информация не обрабатывается, а реализуется только считывание данных из памяти и запись их в регистр или аккумулятор центрального процессора (фиг. 5), в предлагаемом устройстве существенно увеличено быстродействие, так как за время цикла шины центрального процессора, равное четырем тактам Т1-Т4 синхронизируемой частоты (800 не), реализуется считывание данных из блока регистров вычисления квадратного корня и запись их в регистр или аккумулятор центрального процессора. Действительно, после выдачи центральным процессором адреса на вход проницаемого регистра-защелки (интегральная схема 1810 I/1P82) задержка т-| в ней составляет 45 не.

В качестве блока регистров используется микросхема К1500РУ415, в которой цикл считывания равен 15 не, а также применяется транслятор ТТЛ-СЛ (микросхема К1500ПУ124) и транслятор СЛ-ТТЛ (микросхема К1500ПУ125) - задержки равны соответственно 2 и 3 не. Таким образом, задержка Т2 20 не. Блок вычисления квадратного корня содержит п 15 сумматоров (микросхема К1500ИМ180), максимальная задержка одного восемнадцатого сумматора составляет 8,7 не. Общая задержка блока вычисления квадратного корня, поскольку длительность вычислительного процессора в нем равна задержке между входами и выходами, составляет 8,7-15 131 не. Задержка группы элементов И (микросхема 1810ВА86) составляет 35 не. Задержка блока вычисления квадратного корня совместно с группой элементов И составлет тз 160 не. Таким образом, время Т считывания и обработки составляет

Т п + Г2 + Тз 45 + 20 + 160 225 не.

Следовательно, в соответствии с временной диаграммой (фиг. 4) работы центрального процессора считывание и обработка данных заканчиваются к середине второго такта Т2, и в третьем такте ТЗ результат записывается в регистры или аккумулятор центрального процессора. Поскольку для выполнения операции деления в центральном процессоре требуется 190 тактов частоты синхронизации, а благодаря

применению блока вычисления квадратного корня, работающего во время цикла шины для воспроизведения эквивалентной операции извлечения квадратного корня, требуется 4 такта синхронизации, то общая

0 производительность вычислений увеличивается приблизительно в 190/4 48 раз. Кроме того, благодаря применению блока вычисления квадратного корня, работающего в цикле шины, существенно уменьшается

5 память для хранения сервисных программ обработки прерываний, так как в данном устройстве нет необходимости в прерывании центрального процессора (обработка осуществляется в первых двух тактах цикла

0 шины) и, соответственно, нет необходимости в программах для обработки прерываний,

Формула изобретения

0 входы-выходы центрального процессора подключены через мультиплексорную магистраль к информационным входам-выходам сопроцессора, процессора ввода-вывода, к информационным входам-выходам первой

5 группы приемопередатчика и к информационным входам первой группы регистра-защелки, первый выход состояния центрального процессора подключен к первому управляющему входу сопроцессора , к

0 управляющим входам процессора ввода-вывода и контроллера шины, второй выход со- стояния центрального процессора подключен к второму управляющему входу сопроцессора, первый выход генератора

5 тактовых импульсов подключен к входам синхронизации центрального процессора, сопроцессора, процессора ввода-вывода и контроллера шины, выход признака готовности и выход признака установки в О ге0 нератора тактовых импульсов подключены соответственно к входам признака готовности и к входам сброса центрального процессора, сопроцессора и процессора ввода-вывода, первый и второй входы-выхо5 ды запроса/разрешения доступа к магистрали центрального процессора подключены соответственно к входам-выходам запроса/разрешения доступа к магистрали сопроцессора и процессора ввода-вывода, выход признака обращения к центральному

процессору сопроцессора подключен к входу проверки признака ожидания центрального процессора, первый и второй управляющие входы системы подключены соответственно к первому и второму входам режима генератора тактовых импульсов, вход нулевого потенциала системы подключен к входу режима центрального процессора и к входу признака разрешения вывода регистра-защелки, первый выход контроллера шины подключен квходустробирования регистра- защелки, второй информационный вход которого подключен к выходу признака разрешения старшего байта центрального процессора, выходы регистра-защелки через адресную магистраль подключены к адресным входам блока оперативной памяти, информационные входы-выходы второй группы приемопередатчика через магистраль данных подключены к информационным входам-выходам блока оперативной памяти, первый и второй выходы контроллера шины через магистраль управления подключены к входам записи и чтения блока оперативной памяти, отличающаяся тем, что, с целью увеличения быстродействия системы, она содержит блок управления, блок постоянной памяти, блок оегистров, блок вычисления квадратного корня и группу элементов И, причем выходы регистра-защелки через адресную магистраль подключены к адресным входам блока постоянной памяти, к входам выборки первой группы блока регистров и к входам группы режима блока управления, информационные входы-выходы второй группы приемопередатчика через магистраль данных подключены к выходам блока постоянной памяти, к информационным входам блока регистров и к информационным входам блока вычисления квадратного корня, выходы которого подключены соответственно к первым входам элементов И группы, выходы которых через мультиплексорную магистраль подключены к информационным входам-выходам центрального процессора, сопроцессора, процессора ввода-вывода, к информационным входам-выходам первой группы приемопередатчика и к информационным входам первой группы регистра-защелки-, с третьего по пятый выходы контроллера шины через магистраль управления подключены соответственно к входу чтения блока постоянной памяти и входу записи и чтения блока регистров, шестой и седьмой выходы контроллера шины подключены соответственно к первому и второму входам режима блока управления, выходы с первого по девятый которого подключены соответственно к первому и второму управляющим входам приемопередатчика, к вторым входам элементов И группы, к первому и второму входам выборки второй группы блока регистров, к первому и второму входам выборки блока

оперативной памяти, к первому и второму входам выборки блока постоянной памяти, вход нулевого потенциала устройства подключен к входу нулевого потенциала блока вычисления квадратного корня.

0 2. Система по п, 1, от л и ч а ю ща я с я тем, что блок управления содержит дешифратор, четыре элемента ИЛИ, шесть элементов И и два элемента НЕ, причем первый и второй входы режима группы блока подклю5 чены к входам дешифратора, третий вход режима группы блока подключен к первым входам первого, второго и третьего элементов И, четвертый вход режима группы блока подключен к первым входам четвертого, пя0 того и шестого элементов И, первый вход режима блока подключен к первому входу первого элемента ИЛИ, выход которого подключен к первому выходу блока, второй вход режима которого подключен к входу перво5 го элемента НЕ, выход которого подключен к первым входам второго и третьего элементов ИЛИ, выходы которых подключены соответственно к второму и третьему выходам блока, первый выход дешифратора подклю0 чен к вторым входам третьего и шестого элементов И, второй выход дешифратора подключен к первому входу четвертого элемента ИЛИ, к вторым входам первого и второго элементов И и входу второго элемента

5 НЕ, выход которого подключен к второму входу третьего элемента ИЛИ, выход четвертого элемента ИЛИ подключен к вторым входам первого и четвертого элементов И, выходы которых подключены соответствен0 но к пятому и четвертому выходам блока, третий выход дешифратора подключен к второму входу четвертого элемента ИЛИ, четвертый выход дешифратора подключен к вторым входам второго и пятого элементов

5 И, выходы которых подключены соответственно к седьмому и шестому выходам блока, выходы шестого и третьего элементов И подключены соответственно к восьмому и девятому выходам блока.

0 3. Система по п. 1,отличающаяся тем, что блок вычисления квадратного корня содержит п сумматоров, где п - разрядность выходного кода, п-2 групп сумматоров по модулю два и п-1 элементов НЕ, причем

5 каждый i-й выход (i 2....J+1) j-ro сумматора (j 2,...,n-1) подключен к (-1)-му информационному входу первой группы 0+1)-го сумматора, выход переноса fro сумматора (1 s-1п) подключен к В-му выходу блока, к первому информационному входу Е-го сумматоpa no модулю два каждой группы, начиная с 6-й, к первому информационному входу второй группы (ЈМ)-го сумматора и вторым информационным входам сумматоров по модулю два ()-й группы, второй выход первого сумматора подключен к первому информационному входу второй группы второго сумматора, выходы сумматоров по модулю два р-й группы (р 1п-2) подключены соответственно к информационным входам с второго по (р+1)-й второй группы (р+2)-го сумматора, выход В-ro элемента НЕ подключен к (ЕН)-му информационному входу второй группы (БН)-го сумматора, вход нулевого потенциала блока подключен к с-му (с 2,...,п) информационному входу первой группы (с+1)-го сумматора, (2Ј-1)-й информационный вход блока подключен к первому информационному входу Ето сумматора, 2Е-й информационный вход блока подключен к второму информационному входу Кто сумматора и входу (то элемента НЕ,

А -27 У

Фиг. 2

Фиг.З

ак (

Цикл шины

Т1

72

А19+А16

-( Адрес д СостояниеVAuff+АДО

-{Адрес /

t Ц О О не

t

простоя

МП

Составитель А.Гегечкори Редактор Л.Веселовская Техред М.МоргенталКорректор С.Шевкун

Заказ 1671ТиражПодписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул.Гагарина, 101

/fb 1 1)

ГЗ

7

/Ъкооные. данные

PtJ2.5

| Управляющая вычислительная система | 1986 |

|

SU1451711A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Лю Ю-Чжен, Г.Гибсон | |||

| Вальцевой станок для смазки клеем фанер | 1927 |

|

SU8086A1 |

| Способ получения сульфокислот из нефтяных масел | 1911 |

|

SU428A1 |

Авторы

Даты

1992-05-15—Публикация

1989-12-14—Подача