Изобретение относится к вычислительной технике и предназначено для размножения часто используемых в вычислениях блоков данных путем реализации новых операций "запись при чтении" и "запись в параллель". Изобретение может быть, в частности, использовано для ускорения работы системного блокового ввода-вывода с буферизацией, суть работы которого заключается в том, что при поступлении запроса, например, на вывод данных последние копируются системой в область системного пула, где формируются в блоки, выводимые непосредственно на устройство записи. При этом выполнение программ пользователя задерживается только на время копирования выводимых данных в область системного пула. После этого выводимые данные поступают из системного пула в устройство вывода со скоростью, определяемой быстродействием устройства вывода и системными подпрограммами. Таким образом, для пользователя лимитирующим является процесс копирования данных.

Известно устройство копирования (Казаринов Ю.М. и др. Применение микропроцессоров и микроЭВМ в радиотехнических системах. М.: Высшая школа, 1988, с.50), содержащее процессор, в котором предусмотрена обработка строковых переменных, системную шину, шины адреса и данных, и микросхемы страниц памяти. Данное устройство обеспечивает копирование содержимого части оперативной памяти в другую ее часть путем инициализации счетчика циклов, загрузки адресов начала и конца копирования, а также направления последовательности копирования областей памяти оригинала и копии, загрузки собственно команды копирования типа цикла, адресации ячейки памяти области-оригинала, считывания содержимого ячейки области-оригинала в регистр процессора, адресации ячейки области-копии, записи содержимого регистра процессора в ячейку области-копии, модификации счетчика циклов, проверки на ноль счетчика циклов, модификации адресов ячеек областей памяти оригинала и копии (конец цикла, переход на цикл адресации ячейки памяти области-оригинала).

Недостатком известного устройства является медленность копирования данных.

Наиболее близким по технической сущности к заявляемому является устройство копирования областей оперативной памяти посредством прямого доступа к памяти через регистр, состоящее из системной шины, шины данных, шины адреса, контроллера прямого доступа к памяти и микросхем страниц памяти (Журавский А. А. и др. Организация управления расширенной памятью для процессора КР580ИК80А. Микропроцессорные средства и системы, 1988, N 4, с.87). Данное устройство предназначено для работы процессора с малым количеством адресных шин и большой памятью, и в нем в отличие от описанного выше устройства модификация счетчика циклов, проверка на ноль счетчика циклов, модификациях адресов ячеек области памяти оригинала и копии осуществляются аппаратно при помощи контроллера прямого доступа к памяти.

Недостатком известного устройства является низкое быстродействие операции копирования данных в оперативной памяти, связанное с наличием промежуточной среды (регистра процессора) между областью-оригиналом и областью-копией.

В идеальном случае данные, появившиеся на шине данных, должны быть непосредственно считаны в область-копию без использования промежуточной среды. Для этого необходимо подать в область-оригинал сигнал чтения и адрес оригинала, а в область-копию - сигнал записи и адрес копии.

Однако в системе обычно имеется одна адресная шина и, следовательно, на ней можно выставить лишь один адрес, в то же время управляющие линии чтения и записи доступны всем блокам и одновременная подача сигналов записи и чтения запрещена.

Изобретение позволяет располагать область-оригинал и область будущей копии в одном и том же месте адресного пространства, что делает возможным использование одного и того же адреса для адресации как оригинала, так и копии. Кроме того, устройство обеспечивает восприятие областью-копией сигнала чтения как сигнала записи, хотя возможна модификация устройства, в которой область-оригинал трактует сигнал записи как сигнал чтения. Оба варианта устройства эквивалентны с точки зрения достигаемой цели.

Целью изобретения является повышение быстродействия.

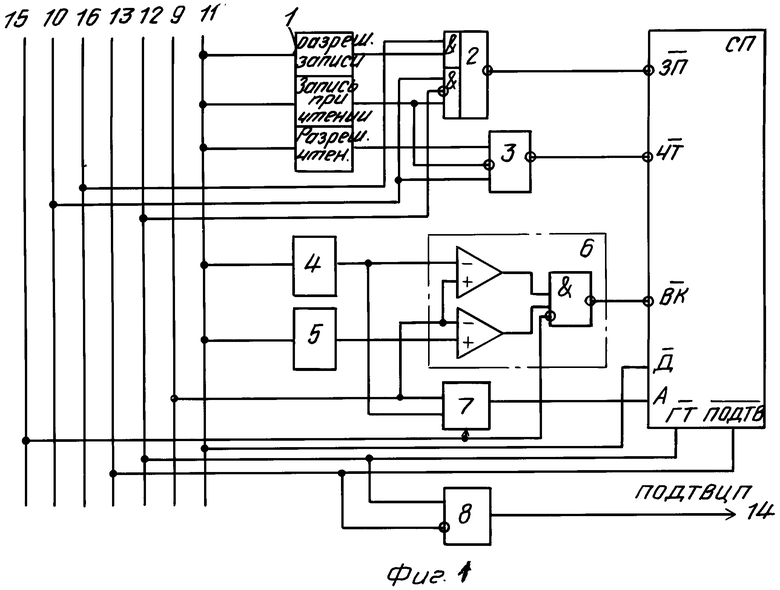

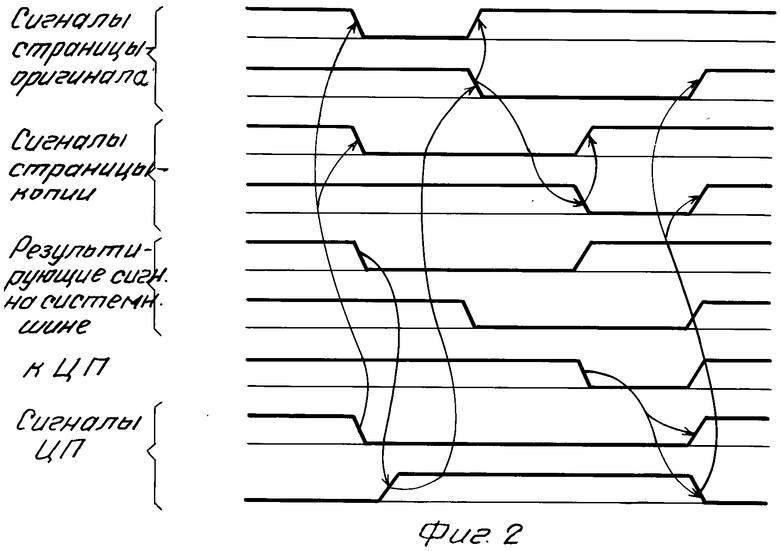

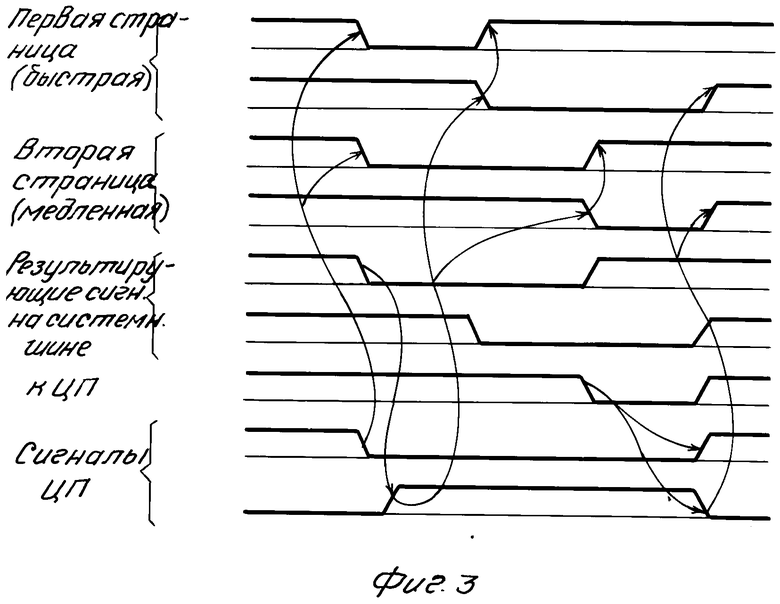

На фиг.1 приведена блок-схема устройства; на фиг.2 и 3 - временные диаграммы функционирования устройства в процессе записи при чтении и записи в параллель.

Изобретение позволяет осуществлять копирование при помощи новой операции "запись при чтении". При этом страница-копия перемещается в адресном пространстве посредством изменения содержимого программно доступных регистров адреса начала и конца страницы таким образом, чтобы начало области, подлежащей копированию, совместилось с началом области оперативной памяти, в которую производится копирование, а конец копируемой области совместился с концом области, в которую производится копирование, в результате совмещаются все адреса ячеек-оригиналов с соответствующими ячейками-копиями. После этого в странице-копии устанавливают режим "запись при чтении" путем изменения содержимого программно доступного регистра статуса страницы, в результате чего микросхемы страницы-копии воспринимают сигнал чтения как сигнал записи. Вслед за этим производят последовательное чтение ячеек-оригиналов в регистр процессора или в устройство ввода-вывода (может быть использовано и фиктивное устройство ввода-вывода с бесконечным быстродействием, т.е. лишь генерирующее сигнал подтверждения). Одновременно с чтением каждой ячейки-оригинала происходит аппаратная запись в ячейку-копию по тому же адресу, поскольку адреса их совмещены.

После чтения (и одновременного копирования) всех нужных ячеек памяти страницу-копию перемещают в требуемую область адресного пространства посредством изменения содержимого программно доступных регистров адреса начала и конца страницы. Соответствующим образом изменяют при необходимости режим работы страницы.

Устройство позволяет осуществлять в оперативной памяти быстрое размножение блоков информации, часто используемых в вычислениях, за счет реализации новой операции "запись в параллель".

Рассмотрим простейший вариант размножения блоков памяти, когда требуется записать m байтов информации в N непрерывных областей памяти, расположенных в N разных страницах. Для этого N-1 областей памяти, принадлежащих N-1 страницам, совмещают в адресном пространстве с первой областью первой страницы, после чего обычным способом осуществляют запись в эту область адресного пространства.

Возможна комбинация описанных выше операций, т.е. "запись в параллель при чтении".

Устройство (фиг.1) содержит входящий в блок запоминания информации регистр 1 статуса с ячейками, разрешающими или запрещающими работу страниц памяти в режимах чтения, записи и записи при чтении, логические элементы 2 и 3, обеспечивающие согласование и непротиворечивость сигналов чтения и записи, подаваемых непосредственно на микросхемы памяти, регистр 4 адреса начала страницы, входящий в блок запоминания информации, и регистр 5 адреса конца страницы, входящий в блок запоминания информации, определяющие местоположение и размер страницы памяти в адресном пространстве, схему 6 сравнения, определяющую принадлежность адреса, выставляемого на адресной шине: зона адресов данной страницы памяти, сумматор 7, осуществляющий преобразование адресов, поступающих с адресной шины, в адреса, подаваемые на микросхемы памяти, логический элемент 8, осуществляющий преобразование двух сигналов системного интерфейса "подтвеpждение" (ПОДТВ) и "готовность" (ГТ) в сигнал "Подтверждение к центральному процессору" (ПОДТВ ЦП). Логический элемент 8 может быть один на всю ЭВМ (однопроцессорную), все остальные элементы образуют собой логическую схему, принадлежащую каждой странице памяти.

Все описанные регистры устройства программно доступны, каждому из них соответствует свой адрес на шине ввода-вывода.

Устройство работает следующим образом.

Инициализация. Для того, чтобы инициализировать режим "запись при чтении", в адресные регистры 4 и 5 заносят такие адреса, чтобы область, подлежащая копированию, совместилась в адресном пространстве с областью, в которую будет производиться копирование. В регистр 1 статуса страницы - будущей копии - заносят биты, разрешающие режим "запись при чтении" и запрещающие чтение, при этом состояние ячейки разрешения записи не имеет значения и устанавливается по необходимости.

Если необходимо инициализировать режим работы "запись в параллель", в адресном пространстве совмещают области страниц, в которые будет осуществляться параллельная запись, путем занесения соответствующих адресов в программно доступные адресные регистры начала 4 и конца 5 страницы. Затем в регистр 1 статуса заносят бит, разрешающий запись, при этом состояние ячеек разрешения чтения и разрешения записи при чтении не имеет существенного значения и устанавливается по необходимости.

Режим "запись при чтении". После инициализации процессор или другое устройство, управляющее шиной (УУШ), осуществляет чтение области памяти, подлежащей копированию. При этом на шине 9 адреса (ША) (фиг.1) устанавливают адрес соответствующей ячейки памяти из требуемой области. По окончании переходных процессов в ША на линии 15 стробирования адреса 9АДР СТБ) устанавливают сигнал, подтверждающий достоверность адреса (фиг.2). После опознания адреса страницами копии и оригинала они вырабатывают сигналы подтверждения адресации ПОДТВ 1 и ПОДТВ 2 (фиг.2), а поскольку системная линия ПОДТВ выполнена в виде монтажного ИЛИ для отрицательных сигналов, то системный сигнал подтверждения ПОДТВ устанавливается по первому из фронтов ПОДТВ 1 или ПОДТВ 2, информируя процессор о том, что ячейка адресована. После получения подтверждения процессор или УУШ устанавливает сигнал чтения на линии 10 чтения (ЧТ). По получении этого сигнала страница-оригинал выставляет данные на шине 11 данных (ШД). После установления данных и окончания переходных процессов страница-оригинал снимает сигнал ПОДТВ 1 и устанавливает сигнал ГТ 1, который вследствие того, что системная линия 12 ГТ выполнена в виде монтажного ИЛИ для отрицательных сигналов, переводит системную линию ГТ в состояние низкого уровня, информируя страницу-копию о достоверности данных на ШД. При этом сигнал готовности к ЦП не поступает, так как эта линия непосредственно не подключена к процессору. Затем страница-копия производит запись данных с ШД. По окончании записи страница-копия снимает сигнал ПОДТВ 2 с системной линии 13 ПОДТВ и устанавливает сигнал ГТ 2. При этом срабатывает логический элемент 8 и вырабатывает сигнал ПОДТВ ЦП на линии 14 ПОДТВ ЦП, информирующий процессор о завершении копирования, после чего процессор или УУШ снимает сигналы с линий АДР СТБ (15) и ЧТ (10), а страницы копии и оригинала снимают сигналы ГТ 1 и ГТ 2, завершая цикл.

Режим "запись в параллель". В этом режиме на ША (9) устанавливают адрес требуемой ячейки и по окончании переходных процессов устанавливают сигнал стробирования адреса на линии 15 АДР СТБ, подтверждая достоверность адреса (фиг. 3). После опознания адреса страницами, например первой (быстрой) и второй (медленной), последние устанавливают сигналы ПОДТВ 1 и ПОДТВ 2. В результате на линии 13 ПОДТВ устанавливается сигнал, информирующий процессор или УУШ о приеме адреса страницами. После этого процессор или УУШ устанавливает сигнал записи на линии 16 ЗП, информирующий страницы памяти о достоверности данных на ШД 11 и инициирующий страницы на операцию записи. После завершения операции записи первой (быстрой) страницей она снимает сигнал ПОДТВ 1 и устанавливает сигнал ГТ 1. После завершения операции записи второй (медленной) страницей она снимает сигнал ПОДТВ 2 и устанавливает сигнал ГТ 2. Снятие сигнала с системой линии 13 ПОДТВ и установление сигнала на линии 13 ГТ вызывает срабатывание элемента 8 и установление сигнала на линии ПОДТВ ЦП, информирующего процессор или УУШ о завершении операции записи самой медленной из страниц. Затем цикл завершается аналогично режиму "запись при чтении".

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1988 |

|

SU1615803A1 |

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

| Устройство для обмена данными между процессорами | 1988 |

|

SU1566361A1 |

| Многопроцессорная система | 1987 |

|

SU1464168A1 |

| Устройство КЭШ-памяти | 1988 |

|

SU1675881A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для обмена данными между процессором и периферийными устройствами | 1983 |

|

SU1167615A1 |

Изобретение относится к вычислительной технике и предназначено для размножения часто используемых в вычислениях блоков данных путем реализации новых операций "запись при чтении" и "запись в параллель". Целью изобретения является повышение быстродействия. Цель достигается тем, что устройство содержит схему сравнения, блок запоминания информации, элемент 2И-ИЛИ-НЕ, элемент И-НЕ, элемент ИЛИ и сумматор. 1 з.п.ф-лы, 3 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство переадресации накопителяиНфОРМАции СиСТЕМы ОбРАбОТКи дАННыХ | 1979 |

|

SU845157A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-09-30—Публикация

1990-03-14—Подача