4i О9

Изобретение относигсся к запоминающим устройствам, в которых для повышения надежности используется кшко- ритарное резервирование на уровне микросхем памяти.

Целью .изобретения является увеличение инфop saциoннoй гмкости устройства.

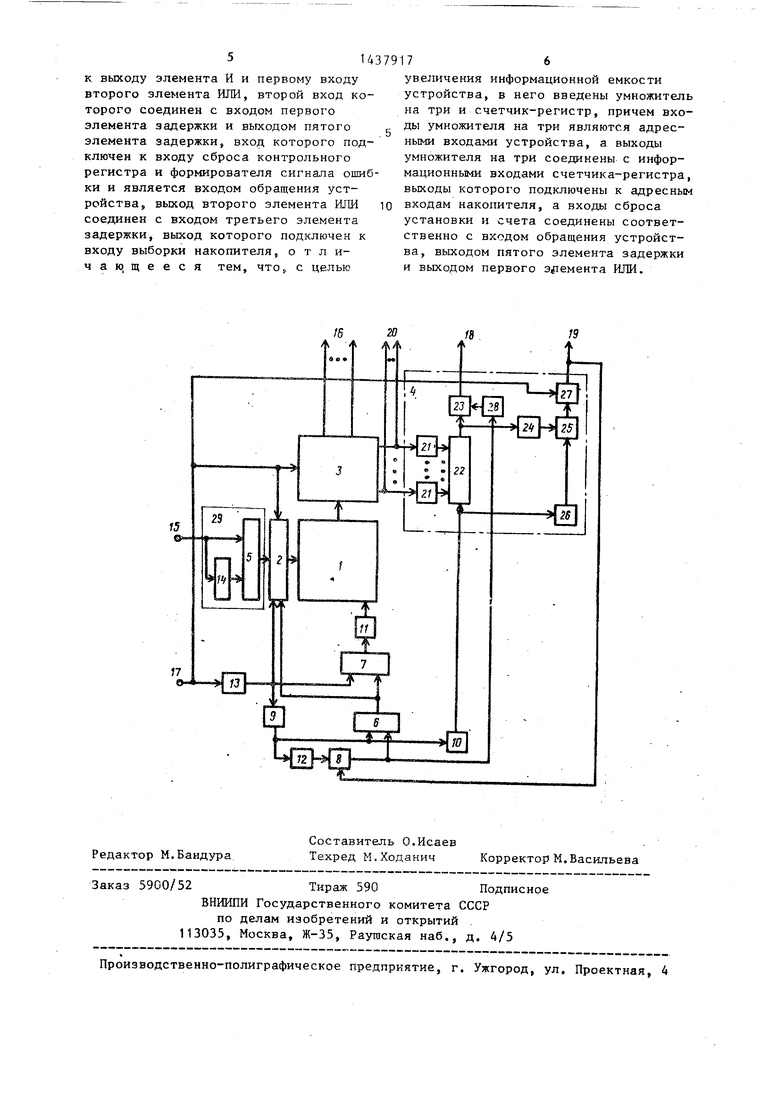

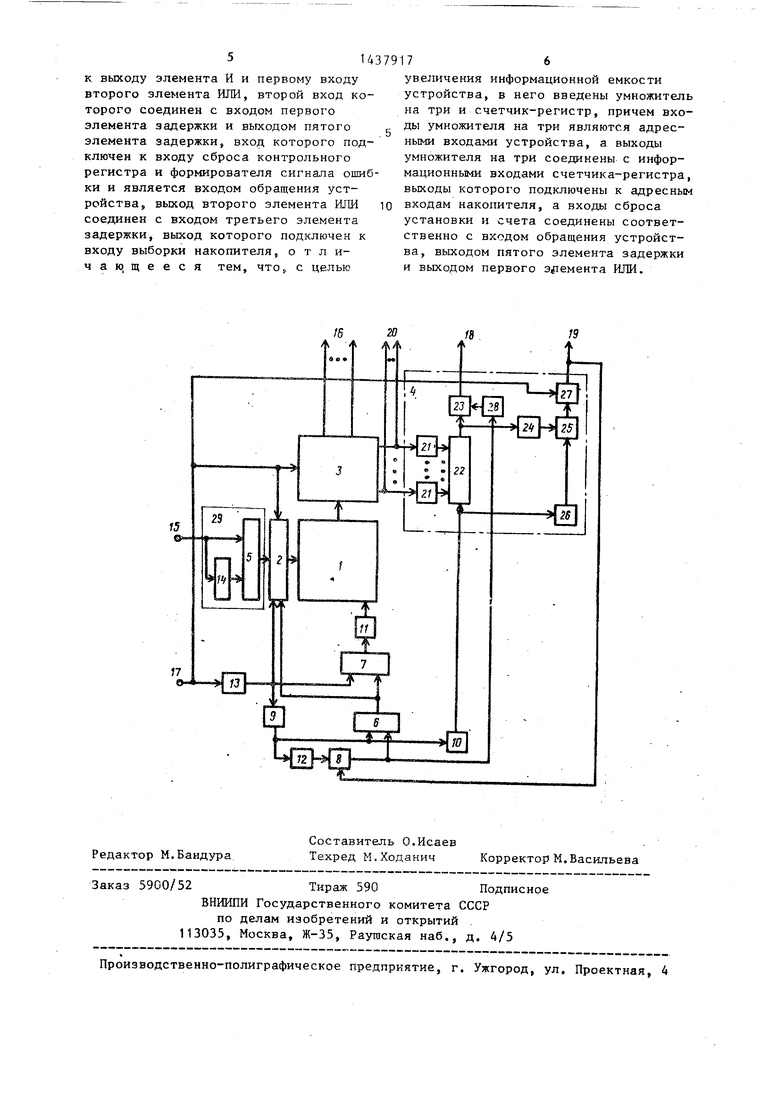

На чертеже кзображзнз. структурная схема предлагаемого зипоминающего устройства.

Запоминающеа устусйстзо с рез ер- вировйнием содержит накопитель 1 с. информационной емкость-О;, в три раза превышающей требуемую для решения задач системьи счетчик-регистр 2,, контрольньй регистр 3, формирователь 4 сигнала ошибки, сумматор 5, первьЕЙ: 6 и второй 7 элементы ИЛИ,, элемент И 8, первый 9, второй 10,, ,. ретий 11 четвертый 12„ пятый 13 з,яе1;4еыты за-- держки, умножитель 14, Устройстзс имеет адресные входы 15s инфорг.;ациочныв выходы 16д вход 1 7. обра1де;;:кя J выход 18 сигна,па Разрешение, считьша- ния 5, выход 19 сигнала зы-- ходы 20 сигналов Неисиравнь г разряды.

Формировсггель сигнала о,лнбки содержит группу инверторов 21s пзрвьш 22 элемент И, элемент I-ffili 23, инвар- ТОР 24, второй 25 элемент Hj П1естой 26 элемент задержки, триггер 27, седь мои 28 элемент задерж си. Блоки 5, i i представляют собой умножите,аь 29 на три,

Устройство работает следу. с1и,им об

разом,

В накопите,ль 1 состояшд,й из БИС оперативной или постоянной памяти,, количество -адресов Б которск в три раза превышает необходимое для работ вычислительного устройства любьш способом записана информацияj причем

, в каждых трех соседник адресах начк ная с адреса, кратного трем, инфор1ч;а ция одинакова. На а ресные зкоды 15 устройства поступает адрес обрав ения который увеличивает адрзс в два ра-- за, например, иутаы г;дзига ег и на один разряд в сторону старшего разря да, после удкоениьй адрес посту пает на второй вход су гматора 5 о Та КИМ образомS на выходе с;у7.даатора 5 получается адрес, в три pasa превышающий адрес обращения о Этот здуес сохраняется до записи его в счет кперегистр 2. Запрос, поданный на вход 17 устройства, стробирует блоки 2, Зо 4 и через пятый элемент 13 задержки подается на вход установки регистра счетчика-регистра 2, разрешая ему прием гщреса, и через второй 7 элемент I-fflH и третий 11 элемент задержки поступает на вход выборки накопи- те,лл 1 Производится считывание ра- иэе записанной информации по адресу, соответствующем у поданному на адрес- ныэ входы накопителя 1 коду адреса от счетчика-регистра 2. Считанная И1-1формац1:1Я записывается в контрольный регистр 3, каждый разряд которого представляет собой, например,двухразрядный счетчик, В зависимости от содержания считанной информации млад Б1ий разряд кахсдого двухразрядного счетч1п :а переключается или не пере- : j Tij4aeTCK.

П-эсла завершения первого цикла считывания из накопителя 1 происходит повторное обращение к нему через интервал времени задаваемый первым 9 э,лементом задержки. При этом задержанный сигнал запроса с выхода пятого 13 элемента задержки поступае через первый вход первого 6 элемента РШИ на вход счета счетчика-регистра 2,, увеличивая его содержимое на еди- ниду. Это обеспечивает переход к адресам второй трети накопителя 1. С выхода первого б эатемента ИЛИ сигнал ,псступает на второй вход второго 7 , ;леме:ата ИЛИ, с выхода которого чере третий 11 элемент задержки он подается на управляющий вход выборки накопителя 1.

При этом происходит считывание информации из адреса другой трети накопителя 1, в котором ранее была записана та же информация, что и в выданном в предьздущемтакте адреса. Считанная информация поступает на входы контрольного регистра 3. Далее возможны два варианта функционирования.

1 Информация при первом и втором обращении совпадает. В этом случае пос,ле второго обращения на каждом из младших разрядов двухразрядных счетчиков контрольного регистра З уста- .гавливается сигнал логического О. сигна.п от всех разрядов контрольного регистра 3 поступает на первые зходы формирователя 4 сигнала оашбкЧд дах;ее через группу инверторо 21 :;а входы элемента И 22, По исте-

чении времени, превышающего время выборки информации из накопителя, на второй вход формирователя 4 сигнала ошибки поступает сигнал от второго 10 элемента задержки, который вызывает срабатывание элемента И 22. Сигнал совпадения через элемент ИЛИ 23 выдает на выход 18 сигнал Разрешение считывания информации, которая устанавливается после второго обращения на старших разрядах двухразрядных счетчиков контрольного регистра 3, соединенных с информационными вь;хода- fOi 16. Поскольку эта информация, проверенная сравнением при считывании из двух третей накопителя 1, признается истинной, она может быть использована процессором.

обращении информация поступает на входы всех разрядов контрольного регистра 3 и вызывает срабатывание соответствуюЕцих двухразрядных счетчиков, в результате чего на их старших разрядах и информационных выходах 16 устройства устанавливается информация, соответствующая истинной по мажоритарному принципу. После задержки на время считывания при третьем обращении, определяемой элементом 28 задержки формирователя 4 сигнала оищбки, через элемент ИЛИ 23 на выходе 18 появляется сигнал Разрешение считывания. По этому сигналу установившаяся на информационных выходах 16 информация может быть использована процессором. Наличие

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1188784A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| Резервированное оперативное запоминающее устройство | 1987 |

|

SU1471225A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с исправлением ошибок | 1986 |

|

SU1363303A1 |

Изобретение относится к запоминающим устройствам, в которых для повьшения надежности используется мажоритарное резервирование на уровне микросхем памяти. Целью изобретения является увеличение информационной емкости устройства. Устройство содержит накопитель, адресные входы которого соединены с выходами счетчика-регистра, информационные входы которого подключены к выходам умножителя на три, входы которого являются адресными входами устройства, контрольный регистр, формирователь сигнала ошибки, элементы задержки ИЛИ, И. Достижение цели изобретения обеспечивается умножением на три адреса обращения к накопителю с последующим чтением идентичной информации из каждой трети накопителя путем инкремен- тирования счетчика-регистра. Если в результате чтения из двух частей накопителя получены одинаковые данные, то они передаются на вьрсод устройства, в противном случае осуществляется чтение из третьей части нако- пителя и истинные данные определяются мажоритарным методом. Накопитель в устройстве используется полностью в отличие от устройства-прототипа, использующего только 3/4 полярной ем- 2 кости. 1 ил. (Л

II. Информация при первом и втором 20 на выходе 19 сигнала Ошибка после

обращении не совпадает в одном или нескольких информационных разрядах, что является признаком неисправности накопителя 1. При этом после второго обращения на выходах младших разрядов соответствующих двухразрядных . счетчиков контрольного регистра-3 устанавливается логическая 1. После подачи сигнала от второго 10 элемента задержки элемент И 22 не срабатывает, а-на выходе 18 не появится сигнал Разрешение считывания, На первый вход элемента И 25 через инвертор 24 подается сигнал логической 1. После подачи на второй вход элемента И 25 задержанного на элементе 26 задержки сигнала от второго 10 элмента задержки элемент И 25 срабатывает и вызьшает переключение триггера 27. В результате этого на выходе 19 устанавливается сигнал Ошибка. Этот сигнал подается на первый вход элемента И 8 и разрешает третье обращение к накопителю, так как на второй вход элемента И 8 будет подан сигнал запроса от входа 17 управления через пятьй 13, первьй 9 и четвертый 12 элементы задержки. Через элемент И 8, первый 6, второй 7 элементы ИЛИ, третий 11 элемент задерж- ки этот сигнал подается на вход выборки накопителя 1. Этот же сигнал с выхода первого 6 элемента ИЛИ поступает на третий управляющий вход счетчика-регистра 2, увеличивая его содержимое на единицу. При этом формируется адрес ячейки, соответствующий обращению к последней трети накопителя 1. Считанная при третьем

второго обращения обеспечивает оператору информацию о наличии неисправности в одной из третей накопителя 1 а состояние информации на выходах 20

25 после второго обращения позволяет локализовать ошибку с точностью до разряда.

Таким образом, в предлагаемом устройстве в отличие от устройстваЗС прототипа накопитель 1 используется в полной мере.

Формулаизобретения

:35 Запоминающее устройство с резервированием, содержащее накопитель, выходы которого соединены со счетными входами контрольного регистра, выход первой группы которого являются ин- 40 формационными выходами устройства, а выходы второй группы - выходал ш неисправных разрядов устройства и подключены к информационным входам форг- Шрователя сигнала ошибки, первый 45 и второй выходы которого являются соответственно выходами разрешения счи- тьшания и ошибки устройства, первый и второй синхровходы формирователя сигнала ошибки соединены соответст- 50 венно с выходами второго элемента задержки и элемента И, первый и второй входы которого подключены соответственно к второму выходу формирователя сигнала ошибки и к выходу четвертого 55 элемента задержки, вход которого соединен с выходом первого элемента задержки и с первым входом первого .элемента ИЛИ, второй вход и выход которого подключены соответственно

к выходу элемента И и первому входу второго элемента ИЛИ, второй вход которого соединен с входом первого элемента задержки и выходом пятого элемента задержки, вход которого подключен к входу сброса контрольного регистра и формирователя сигнала ошибки и является входом обращения устройства, выход второго элемента ШМ соединен с входом третьего элемента задержки, выход которого подключен к входу выборки накопителя, отличающееся тем, что, с целью

/б 20

79176

увеличения информационной емкости устройства, в него введены умножитель на три и счетчик-регистр, причем входы умножителя на три являются адресными входами устройства, а выходы умножителя на три соединены с информационными входами счетчика-регистра, выходы которого подключены к адресным 10 входам накопителя, а входы сброса установки и счета соединены соответственно с входом обращения устройства, выходом пятого элемента задержки и выходом первого э гемента ИЛИ.

18

| Запоминающее устройство с самоконтролем | 1980 |

|

SU951406A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1188784A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-11-15—Публикация

1987-04-20—Подача