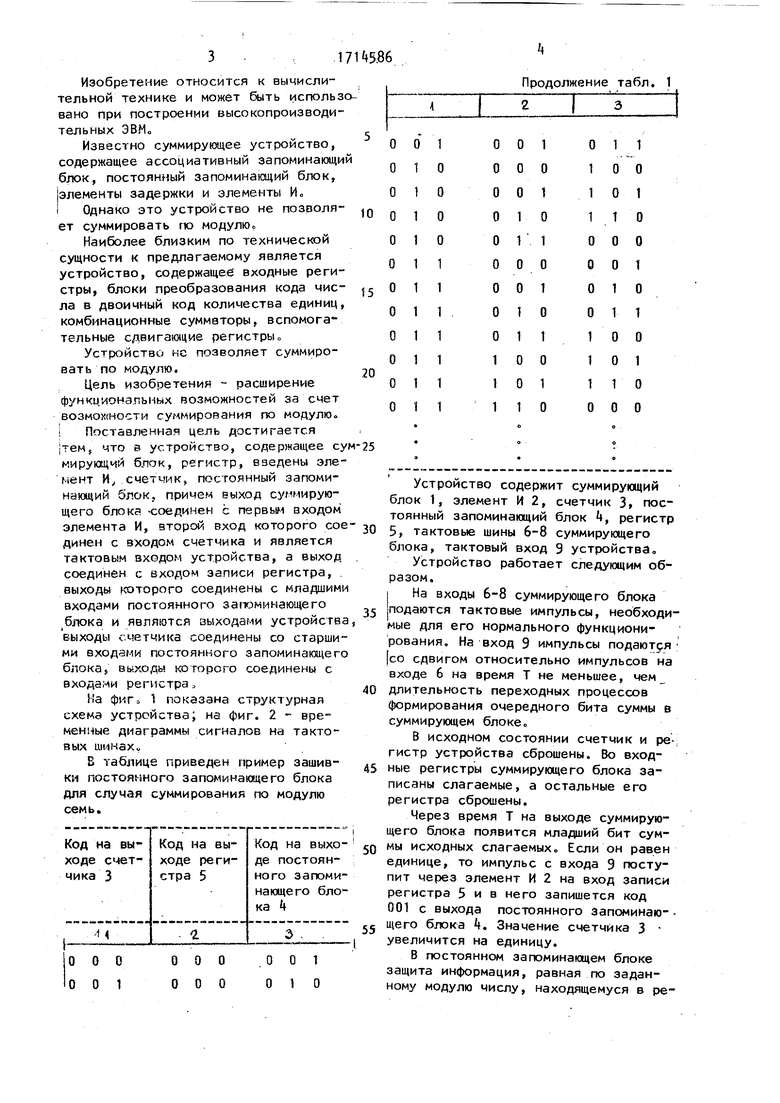

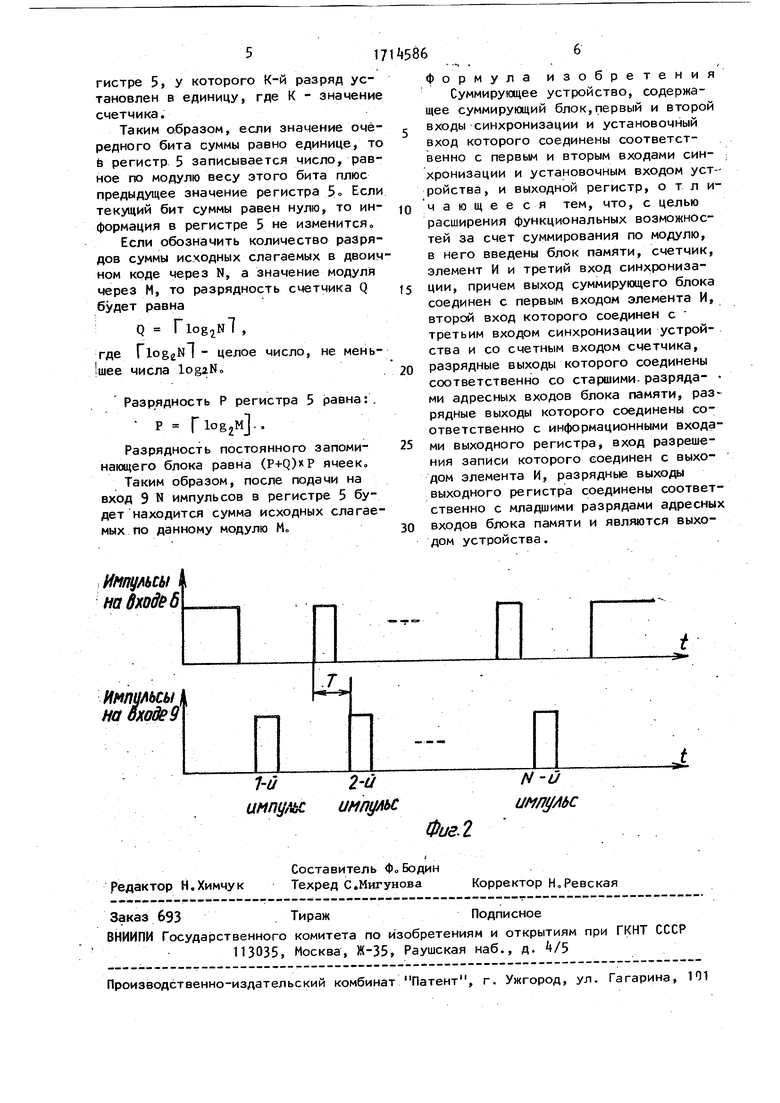

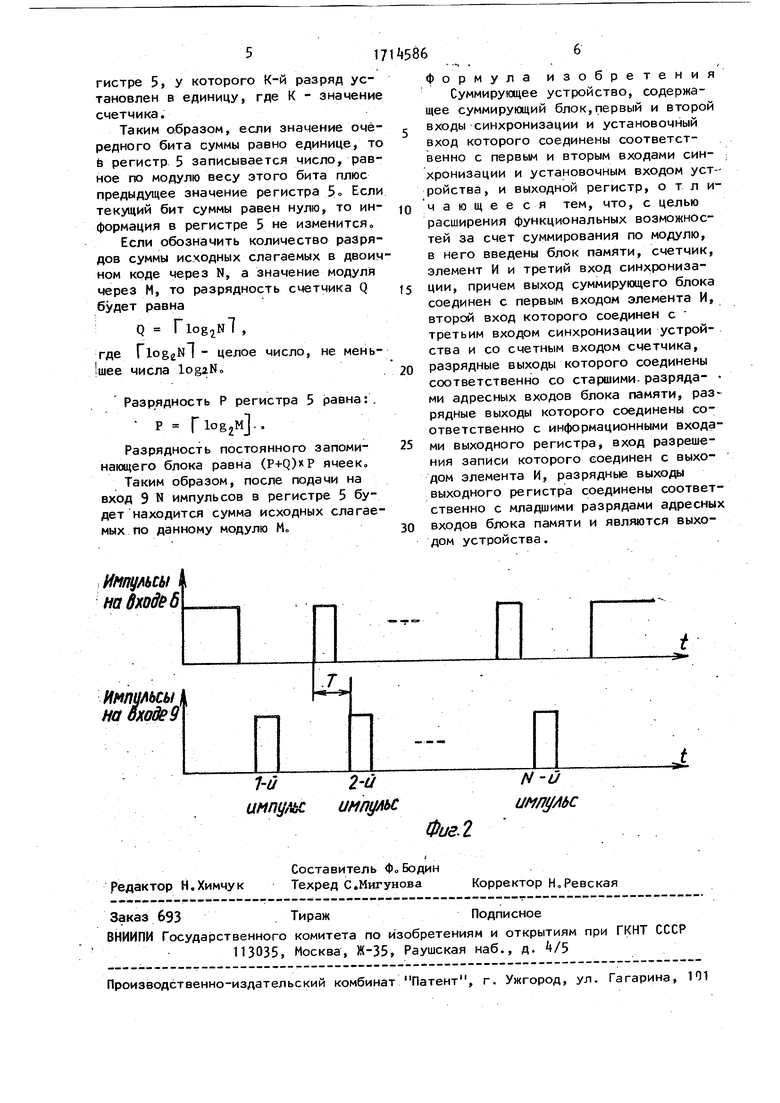

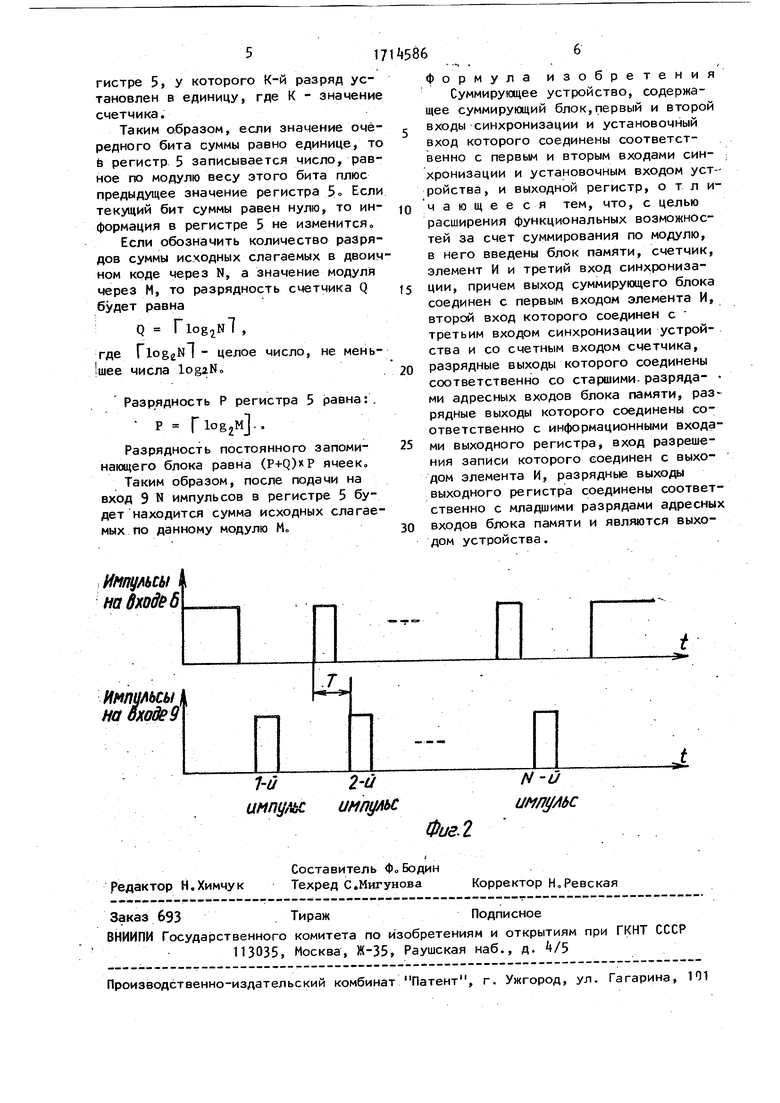

Фиг. 1 Изобретение относится к вычислительной технике и может быть использ вано при построении высокопроизводи тельных ЭВМо Известно суммирующее устройство, содержащее ассоциативный запоминающи блок, постоянный запоминающий блок, |элементы задержки и элементы И о i Однако это устройство не позволяет суммировать по модулю Наиболее близким по технической сущности к предлагаемому является устройство, содержащее входные регистры, блоки преобразования кода числа в двоичный код количества единиц, комбинационные сумматоры, вспомогательные сдвигающие регистры Устр4: йство НС позволяет суммировать по модулю. Цель изобретений - расширение функциональных возможностей за счет возмохсности суммирования по модулю. i Поставленная цель достигается jreMf что в устройство, содержащее су мируюций блок, регистр, введены элемент И счетчик, постоянный запоминающий блок, причем выход суммирующего блока -соединен с первьм входом элемента И, второй вход которого сое динен с входом счетчика и является тактовым входом устройства, а выход соединен с входом записи регистра, . выходы которого соединены с младшим входами постоянного запоминающего блока и являются выходами устройств выходы счетчика соединены со старшими входами постоянного запоминаквцего блока, выходы которого соединены с входами регистра. На фиг о 1 показана структурная схема устройства; на фиг. 2 - временные диаграммы сигналов на тактовых шинах В таблице приведен пример зашивкя постоянного запоминающего блока для случая суммирования по модулю семь. Устройство содержит суммирующий блок 1, элемент И 2, счетчик 3, постоянный запоминающий блок , регистр 5, тактовые шины 6-8 суммирующего блока, тактовый вход 9 устройства. Устройство работает следующим образом, I На входы 6-8 суммирующего блока подаются тактовые импульсы, необходимые для его нормального функционирования. На вход 9 импульсы подаются ; со сдвигом относительно импульсов на входе 6 на время Т не меньшее, чем длительность переходных процессов формирования очередного бита суммы в суммирующем блоке В исходном состоянии счетчик и регистр устройства сброшены. Во входные регистры суммирующего блока записаны слагаемые, а остальные его регистра сброшены. Через время Т на выходе суммирующего блока появится младший бит суммы исходных слагаемых Если он равен единице, то импульс с входа 9 поступит через элемент И 2 на вход записи регистра 5 и в него запишется код 001 с выхода постоянного Запоминаю-щего блока k. Значение счетчика 3 увеличится на единицу. В постоянном запоминающем блоке защита информация, равная по заданному модулю числу, находящемуся в ре

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММИРУЮЩЕЕ УСТРОЙСТВО ПО МОДУЛЮ | 1993 |

|

RU2034328C1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Суммирующее устройство | 1991 |

|

SU1803912A1 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| Устройство для кодирования и декодирования цифрового телевизионного сигнала | 1988 |

|

SU1566485A1 |

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

Изобретение относится к вычислительной технике и может быть использовано в системах и устройствах, функционирующих в системе остаточных классов о Целью изобретения является расширение функциональных возможностей за счет суммирования по модулю. Суммирующее устройство содержит суммирующий блок 1, элемент И 2, счетчик 3, блок k памяти, регистр 5, первый и второй входы 6 и 7 синхронизации, установочный вход 8 и третий вход 9 синхронизации. 2 ил., 1 табл.

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-02-23—Публикация

1990-06-27—Подача