Изобретение относится к устройствам коммутации сигналов с широкой полосой частот.

Цель изобретения - повышение быстродействия.

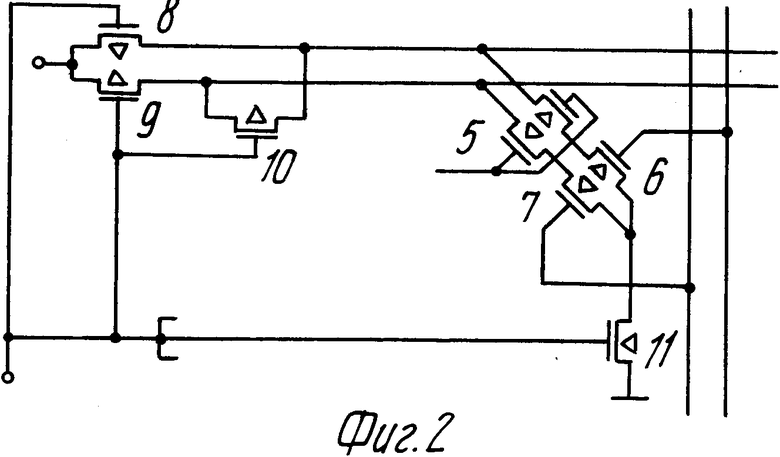

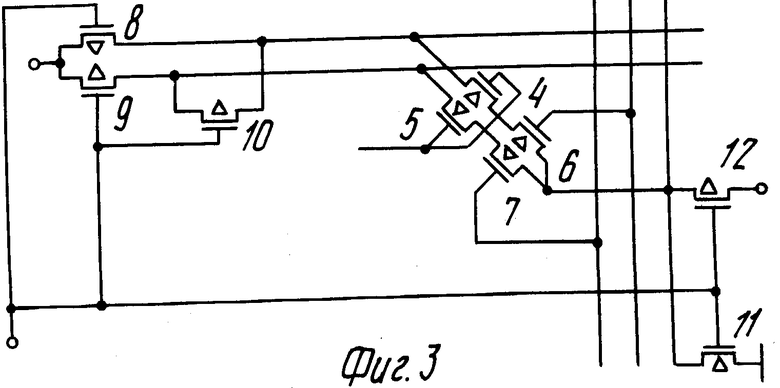

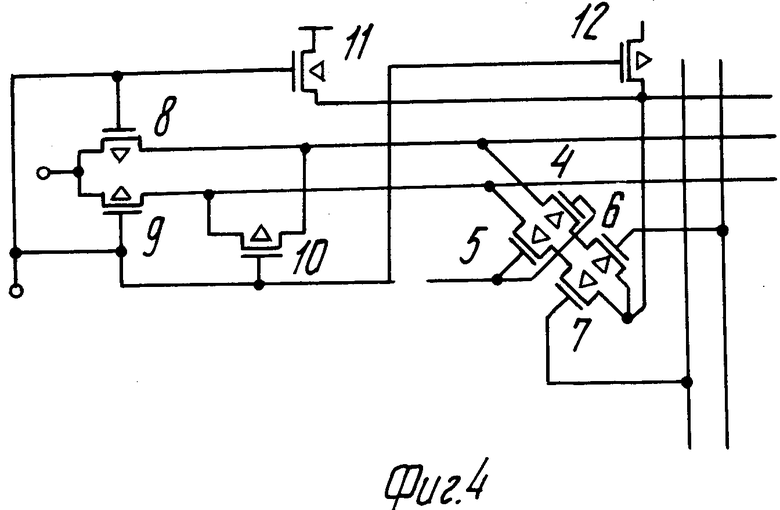

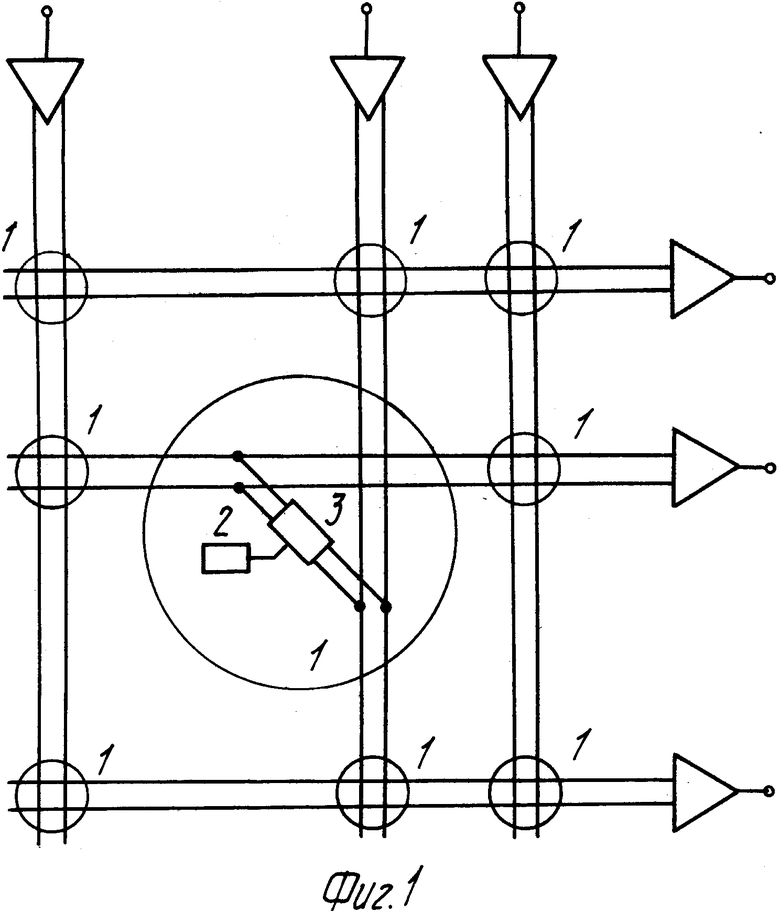

На фиг. 1 - показано устройство коммутации широкополосных сигналов; на фиг. 2 - 4 - примеры схемно-технической реализации их элементов связи в соответствии с изобретением.

Устройство коммутации широкополосных сигналов содержит: узлы коммутации 1, блоки 2 управления, блоки 3 коммутации. При этом блоки 3 коммутации содержат первый и второй переключающие транзисторы, 4и 5 соответственно, первый и второй входные транзисторы 6 и 7 соответственно, первый и второй предвключенные транзисторы 8 и 9, компенсирующий транзистор 10, считывающий транзистор 11, дополнительный транзистор 12.

Устройство коммутации широкополосных сигналов работает следующим образом.

В течении предварительной фазы рv выходные линии заряжаются через первый или второй предвключенные транзисторы 8 или 9 по меньшей мере приблизительно до рабочего потенциала UDD, для чего первый и второй предвключенные транзисторы 8 и 9 переводятся в проводящее состояние с помощью тактовой линии.

При этом при спадающем фронте тактового сигнала Т расположенный между двумя проводами выходной линии компенсирующий транзистор 10 также переводится в проводящее состояние, в результате чего возникает короткое замыкание обоих проводников, за счет чего в начале предварительной фазы весьма быстро обеспечивается компенсация потенциала обоих проводов. После этого оба (теперь компенсированные потенциалу) провода через предвключенные транзисторы 8, 9 заряжаются до рабочего потенциала, причем длительность заряда сокращается в общей сложности за счет того, что после реализованной компенсирующим транзистором 10 компенсации потенциала первый и второй предвключенные транзисторы 8, 9 вовлечены теперь в процессе заряда.

Одновременно с деблокированием предвключенных транзисторов 8, 9 и компенсирующего транзистора 10 осуществляется противоположное управление, считывающим транзистором 11, т. е., его запирание с помощью того же тактового сигнала Т, так что заряд обоих проводов выходных линий матрицы может осуществляться независимо от управления работой переключительных транзисторов 4, 5 и входных транзисторов 6, 7. В той или иной входной линии матрицы, при этом может создаваться (или сохраняться) еже соответствующий подлежащему переключению двоичному разряду потенциал.

Если наряду с индивидуальным для входной линии матрицы считывающим транзистором 11 предусмотрен индивидуальный для входной линии матрицы дополнительный транзистор 12 (фиг. 3) или наряду с индивидуальным для выходной линии матрицы считывающим транзистором 11 предусмотрен индивидуальный для выходной линии матрицы дополнительный транзистор 12 предварительного заряда (фиг. 4), то в этом случае в течение предварительной фазы PV через этот транзистор осуществляется заряд линии псевдомассы, в результате чего обеспечивается разгрузка той или иной блоков 3 коммутации. Это, в частности, при обширных матрицах точек связи с большим количеством, подключенных к линии РМ псевдомассы, пар блоков коммутации ведет к существенному сокращению времени заряда, которое, в свою очередь, полностью входит в соответствующее повышение быстродействия.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2105430C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1991 |

|

RU2105431C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2103832C1 |

| ШИРОКОПОЛОСНОЕ УСТРОЙСТВО КОММУТАЦИИ | 1991 |

|

RU2103841C1 |

| Устройство коммутации широкополосных сигналов | 1987 |

|

SU1738105A3 |

| Устройство коммутации широкополосных сигналов | 1987 |

|

SU1838887A3 |

| УСТРОЙСТВО СВЯЗИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2013877C1 |

| СПОСОБ КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1987 |

|

RU2105428C1 |

| СПОСОБ КОММУТАЦИИ ЭЛЕМЕНТОВ ШИРОКОПОЛОСНОГО СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1987 |

|

RU2105429C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1989 |

|

RU2106755C1 |

Использование: устройства коммутации сигналов с широкой полосой частот. Сущность изобретения: устройство содержит узлы коммутации 1, блоки 2 управления, блоки 3 коммутации, первый и второй переключающие транзисторы 4 и 5, первый и второй входные транзисторы 6 и 7, первый и второй предвключенные транзисторы 8 и 9, компенсирующий транзистор 10, считывающий транзистор 11, дополнительный транзистор 12. Путем компенсации потенциалов проводов выходных линий повышается быстродействие. 2 з. п. ф-лы, 4 ил.

| EP, патент, 0264046, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1998-01-27—Публикация

1989-05-29—Подача