1

Предложение относится к вычислительной технике.

Известно устройство для сложения-вычитания неизбыточного и избыточного аргументов в двоичной системе счисления, содержащее блоки формирования суммы и переноса, выполненные на логических элементах.

Известное устройство обладает низким быстродействием.

Предложенное устройство отличается тем, что в нем каждый из блоков формирования суммы и переноса содержат две схемы формирования соответственно логического дополнения и действительного значения суммы и переноса, состоящих из трех элементов «И, и подключенных к их выходам элементов «ИЛИ, связанных выходом с усилителеминвертором. Первые два входа первых элементов «И каждой схемы формирования соединены с щинами логического дополнения положительного и отрицательного значений избыточного аргумента. Третьи входы первых элементов «И схем формирования дополнения суммы и переноса блоков формирования суммы и переноса соединены с щиной действительного значения неизбыточного артуМента. Третьи входы первых элементов «И схем формирования действительного значения суммы и переноса - с щиной логического дополнения неизбыточного аргумента. Первые входы вторых и третьих элементов «И соединены с шинами действительных положительного и отрицательного значений избыточного аргумента соответственно. Другие входы

второго и третьего элементов «И схемы формирования дополнения суммы соединены с тинами логического дополнения неизбыточного аргумента. Другие входы второго и третьего элементов «И схемы формирования

действительного значения суммы - с шинами действительного значения неизбыточного аргул1ента. Другие входы второго и третьего элементов «И схемы формирования дополнения переноса соединены с шиной действительного значения (при сложении) и шиной логического дополнения (при вычитании) управляющего сигнала соответственно. Другие входы второго и третьего элементов «И схемы формирования действительного значения переноса соединены с шиной логического дополнения и шиной действительного значения управляющего сигнала соответственно. Выход инвертора схемы формирования дополнения суммы данного разряда и выход

инвертора схемы формирования действигельного значения переноса блока формирования переноса предшествующего разряда соединены с выходными шинами положительного значения суммы. Выход инвертора схемы

формирования действительного значения суммы данного разряда и выход инвертора схемы формирования дополнения переноса предшествующего разряда соединены с выходными шинами отрицательного значения суммы.

Это позволяет повысить быстродействие устройства.

Избыточное кодирование осуществляется введением в каждый разряд отрицательной единицы, т. е. один из аргументов кодируется

в двоичной системе с цифрами 1, О, 1: сумма в каждом разряде принимает значение, равное О или 1, а перенос - О или 1, при этом окончательная сумма в г-ом разряде, получаемая в двоичной системе с цифрами 1, О, 1, имеет либо положительное, либо отрицательное значения и является простым объединением истинного значения суммы в i-M разряде и логического дополнения переноса из 1-го разряда для отрицательного значения окончательной суммы и простым объединением дополнения суммы в i-om разряде с истинным значением переноса из (i-1)-го разряда для положительного значения окончательной суммы (под простым объединением понимается то, что каждое значение окончательной суммы в t-OM разряде выдается двумя шинами: соответствующими шилами суммы из 1-го разряда и переноса из (i-1)-го разряда). При таком построении устройства сложения-вычитания результат операции сложения или вычитания появляется за один логический уровень.

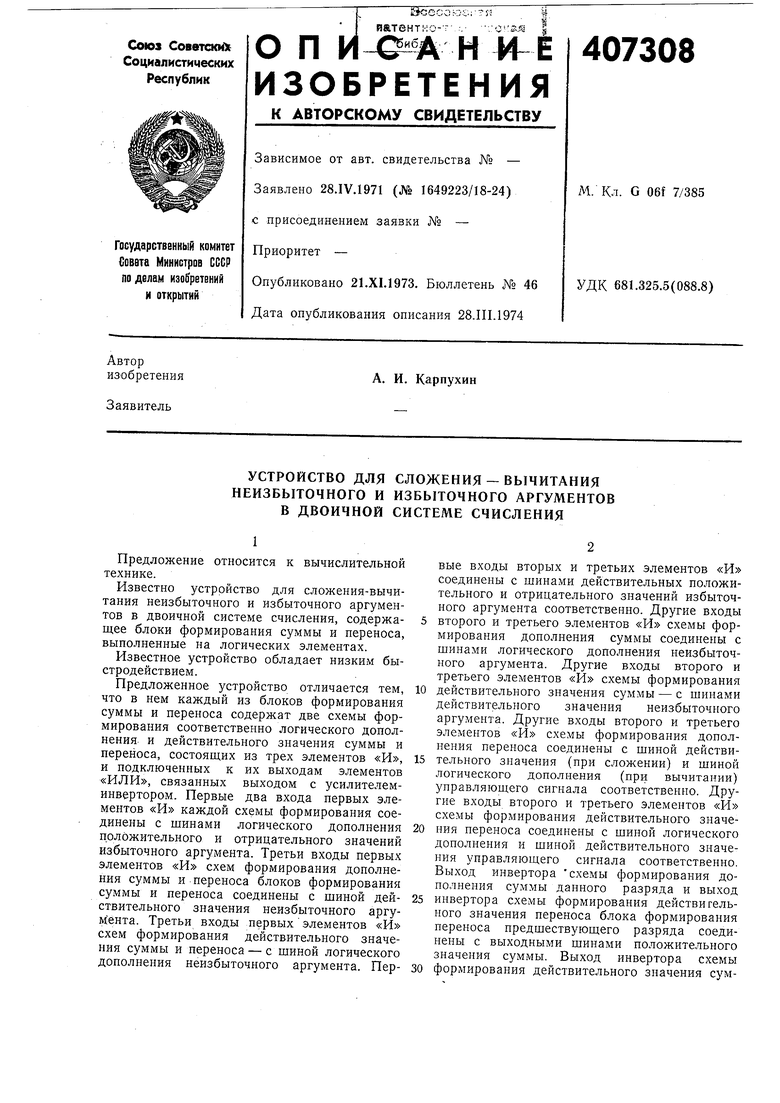

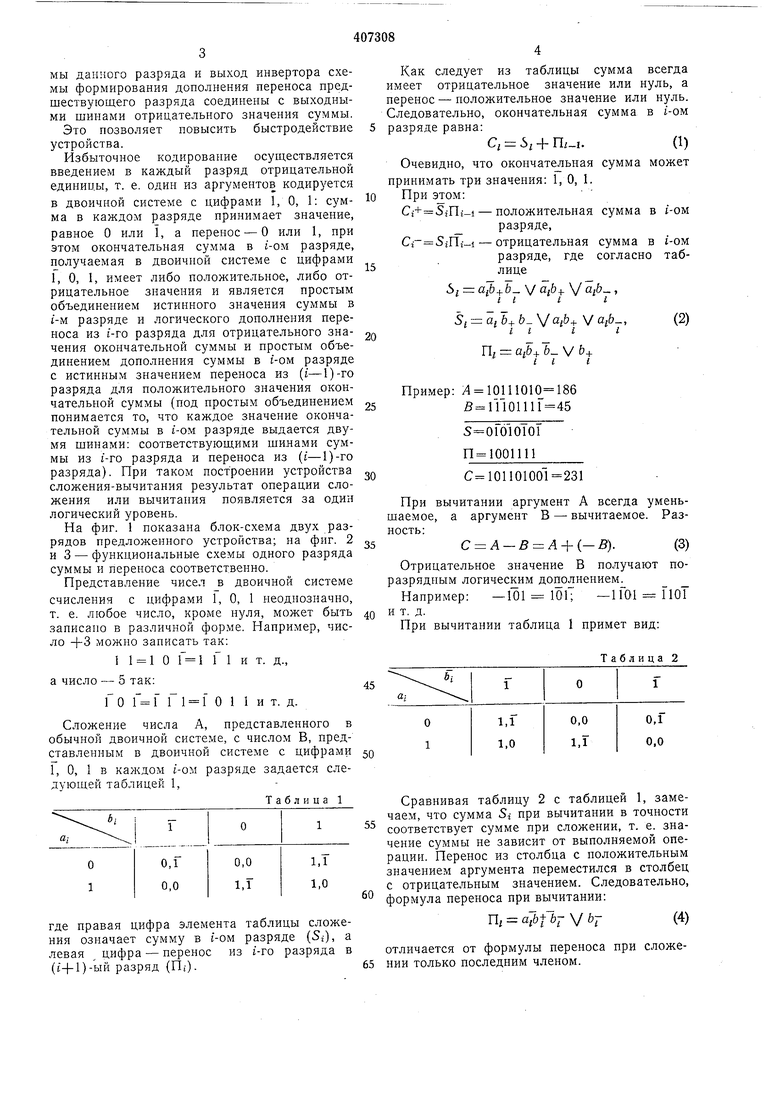

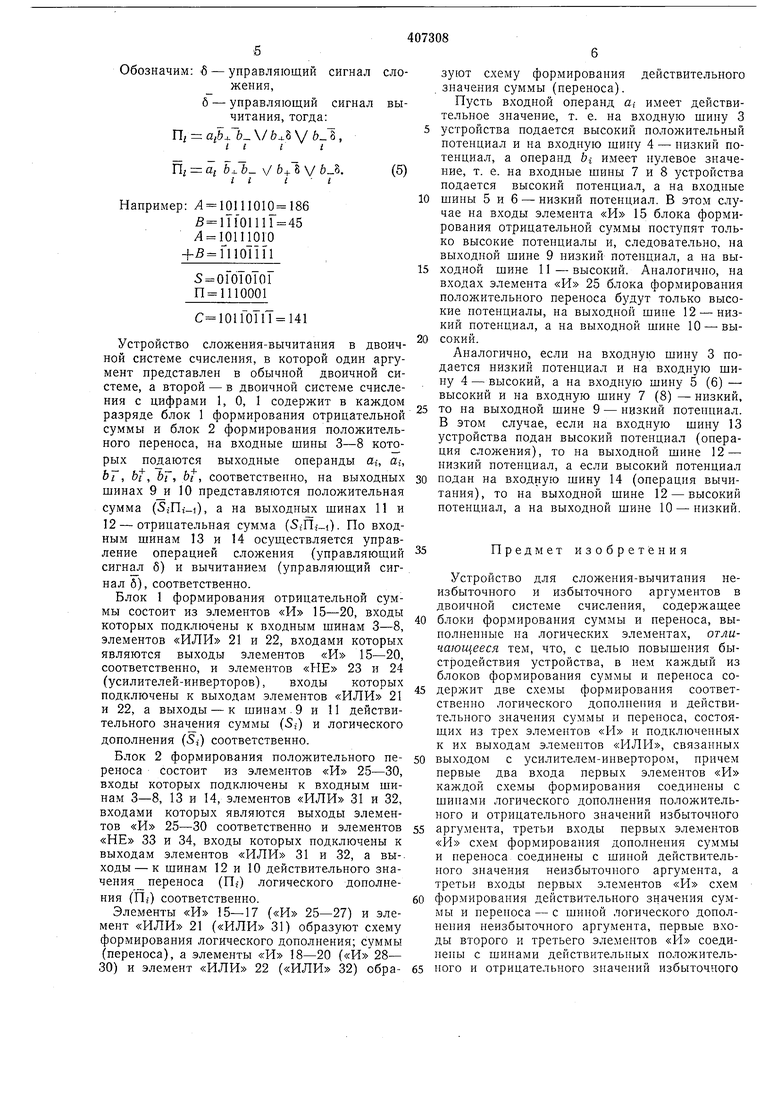

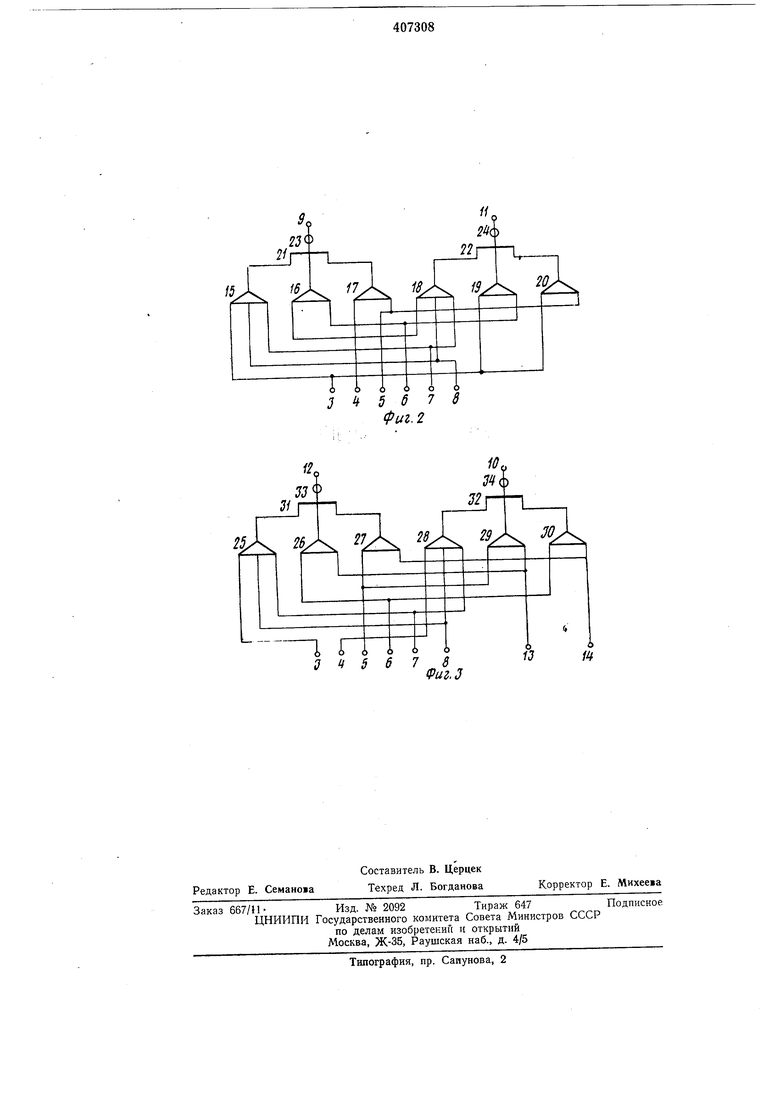

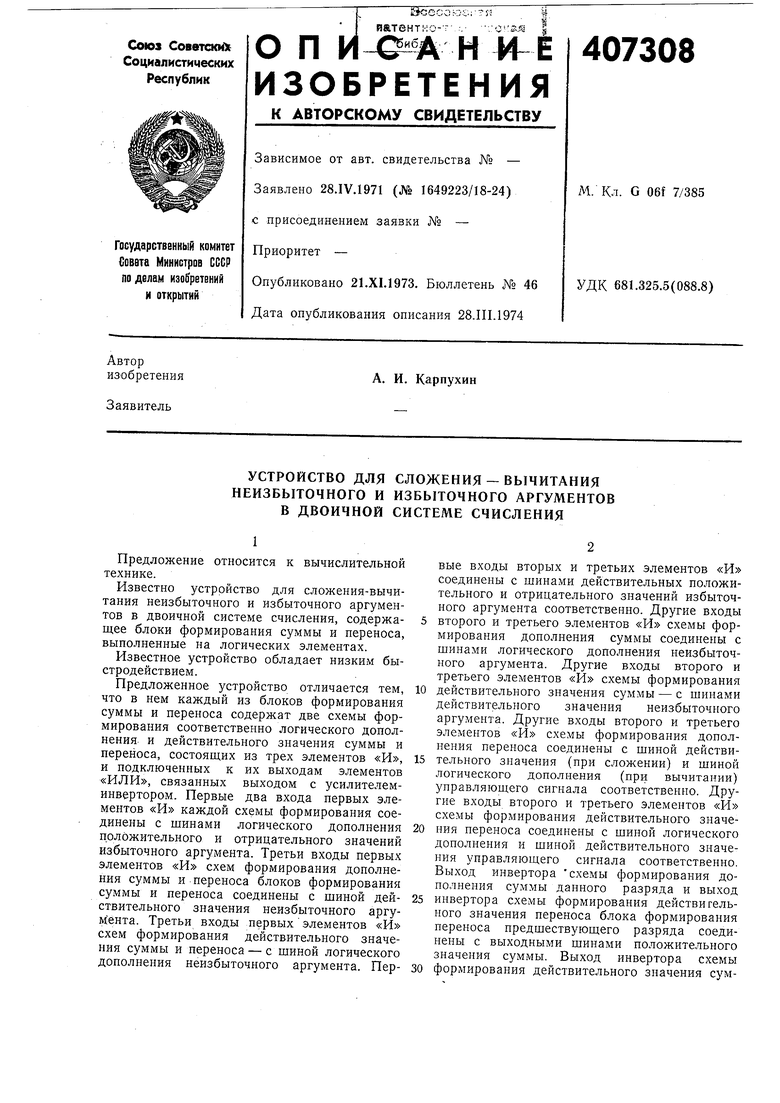

На фиг. 1 показана блок-схема двух разрядов предложенного устройства; на фиг. 2 и 3 - функциональные схемы одного разряда суммы и переноса соответственно.

Представление чисел в двоичной системе счисления с цифрами Г, О, 1 неоднозначно, т. е. любое число, кроме нуля, может быть записано в различной форме. Например, число -)-3 можно записать так:

1 1 1 О Г i Г 1 и т. д., а число - 5 так:

Г О Г Г Г 1 f О 1 1 и т. д. Сложение числа А, представленного в обычной двоичной системе, с числом В, представленным в двоичной системе с цифрами 1, О, 1 в каждом i-oM разряде задается следующей таблицей 1, Таблица 1 где правая цифра элемента таблицы сложения означает сумму в t-ом разряде (Si), а левая цифра - перенос из i-ro разряда в (-|-1)-ый разряд (П;).

Как следует из таблицы сумма всегда

имеет отрицательное значение или нуль, а

перенос - положительное значение или нуль.

Следовательно, окончательная сумма в i-ом

разряде равна:

Q 6г + П.,.(1)

Очевидно, что окончательная сумма может принимать три значения: 1, О, 1. При этом:

Сг+ 5гП;-1 - положительная сумма в i-ом разряде,

Ci- SiHt-i - отрицательная сумма в г-ом разряде, где согласно таблице

6 - ttib+b V / ctib-i Si ui Ъ+ 6 V V o-ib-,

Ь+ I i I

Пример: 10111010 186

s rrioiiir 45

5 01010101

П 1001111

С 101101001 231

При вычитании аргумент А всегда уменьшаемое, а аргумент В - вычитаемое. Разность:

С А - В А + (-В).(3)

Отрицательное значение В получают поразрядным логическим догюлнением.

Например: -101 ШГ; -ifOl ГюТ и т. д.

При вычитании таблица 1 примет вид:

Таблица 2 Сравнивая таблицу 2 с таблицей 1, замечаем, что сумма Si при вычитании в точности соответствует сумме при сложении, т. е. значение суммы не зависит от выполняемой операции. Перенос из столбца с положительным значением аргумента переместился в столбец с отрицательным значением. Следовательно, формула переноса при вычитании: Пг 07611 V Ьт(4) отличается от формулы переноса при сложении только последним членом. Обозначим: б - управляющий сигнал сложения, б - управляющий сигнал вычитания, тогда: Пг а.Ь 6 / V - 8 , i I It Til «г ЬГЬ- / V . Например: Л 10111010 186 S llf01111-45 Л 101П010 +Д-Г11011П 5 оГоТоТоГ П 1110001 С 10110111 141 Устройство сложения-вычитания в двоичной системе счисления, в которой один аргумент представлен в обычной двоичной системе, а второй - в двоичной системе счисления с цифрами 1, О, 1 содержит в каждом . Z,,, 1 л:.„,.„„;; „„,,„„„, разряде блок 1 формирования отрицательной суммы и блок 2 формирования положительного переноса, на входные шины 3-8 которых подаются выходные операнды а,, Яг, ЬТ, bt, ЬГ, bt, соответственно, па выходных шинах 9 и 10 представляются положительная сумма (5гПг-1), а на выходных шинах И и 12 - отрицательная сумма (Sin,-i). По входным шинам 13 и 14 осуществляется управление операцией сложения (управляющий сигнал б) и вычитанием (управляющий сигнал б), соответственно. Блок 1 формирования отрицательной суммы состоит из элементов «И 15-20, входы которых подключены к входным шинам 3-8, элементов «ИЛИ 21 и 22, входами которых являются выходы элементов «И 15-20, соответственно, и элементов «НЕ 23 и 24 /.N (усилителей-инверторов), входы доторьтх подключены к выходам элементов «ИЛИ 21 и 22, а выходы - к шинам. 9 и 11 действительного значения суммы (5,) и логического дополнения (5,) соответственно. Блок 2 формирования положительного переноса состоит из элементов «И 25-30, входы которых подключены к входным шинам 3-8, 13 и 14, элементов «ИЛИ 31 и 32, входами которых являются выходы элементов «И 25-30 соответственно и элементов «НЕ 33 и 34, входы которых подключены к выходам элемептов «ИЛИ 31 и 32, а вы-. ходы - к шинам 12 и 10 действительного значения переноса (Пг) логического дополнения (Пг) соответственно. Элементы «И 15-17 («И 25-27) и элемент «ИЛИ 21 («ИЛИ 31) образуют схему формирования логического дополнения; суммы (переноса), а элементы «И 18-20 («И 2830) и элемент «ИЛИ 22 («ИЛИ 32) образуют схему формирования действительного значения суммы (переноса). Пусть входной операнд а,; имеет действительное значение, т. е. на входную шину 3 устройства подается высокий положительный потенциал и на входную шину 4 - низкий потенциал, а операнд &, имеет нулевое значение, т. е. на входные шипы 7 и 8 устройства подается высокий потенциал, а на входные шины 5 и 6 - низкий потенциал. В этом случае на входы элемента «И 15 блока формирования отрицательной суммы поступят только высокие потенциалы и, следовательно, на выходной шине 9 низкий потенциал, а па выходной шине 11 - высокий. Аналогично, на входах элемента «И 25 блока формирования положительного переноса будут только высокие потенциалы, на выходной шине 12 - низкий потенциал, а на выходной шине 10--высокий. Аналогично, если на входную шину 3 подается низкий потенциал и на входную шину 4 - высокий, а па входную шину 5 (6) - высокий и на входную шину 7 (8) - низкий. «лидпу. шп„у , о; - «..пии, то па выходной шине 9 -низкий потенциал. В этом случае, если на входную шину 13 устройства подан высокий потенциал (операция сложения), то на выходной шине 12 - низкий потенциал, а если высокий потенциал подан на входную шину 14 (операция вычитания), то на выходной шине 12 - высокий потенциал, а на выходной шине 10 - низкий. Предмет изобретения Устройство для сложения-вычитания неизбыточпого и избыточпого аргументов в двоичной системе счисления, содержащее блоки формирования суммы и переноса, выполненные на логических элементах, отличающееся тем, что, с целью повышения быстродействия устройства, в нем каждый из блоков формирования суммы и переноса содержит две схемы формирования соответственно логического дополнения и действительного значения суммы и переноса, состоящих из трех элементов «И и подключенных к их выходам элементов «ИЛИ, связанных выходом с усилителем-инвертором, причем первые два в.хода первых элементов «И каждой схемы формирования соединены с шипами логического дополнения положительного и отрицательного значений избыточного аргумента, третьи входы первых элементов «И схем формирования дополнения суммы и переноса соединены с шиной действительного значения неизбыточного аргумента, а третьи входы первых элементов «И схем формирования действительного значения суммы и переноса - с шиной логического дополнения неизбыточного аргумента, первые входы второго и третьего элементов «И соединены с шинами действительных положительного и отрицательного значений избыточного

аргумента соответственно, другие входы второго и третьего элементов «И схемы формирования дополнения суммы соединены с шинами логического дополнения неизбыточного аргумента, а другие входы второго и третьего элементов «И схемы формирования действительного значения суммы - с шинами действительного значения неизбыточного аргумента, другие входы второго и третьего элементов «И схемы формирования дополнения переноса соединены с шиной действительного значения (при сложении) и шиной логического дополнения (при вычитании) управляющего сигнала соответственно, другие входы второго и третьего элементов «И схемы формирования действительного значения переноса соединены с шиной логического дополнения и шиной действительного значения управляющего сигнала соответственно, выход инвертора схемы формирования дополнения суммы данного разряда и выход инвертора схемы формирования действительного значения переноса предшествующего разряда соединены с выходными шинами положительного

значения суммы, а выход инвертора схемы формирования действительного значения суммы данного разряда и выход инвертора схемы формирования дополнения переноса предшествующего разряда соединены с выходными шинами отрицательного значения суммы.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2109325C1 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| УСТРОЙСТВО для ЦИФРОВОГО РЕГУЛИРОВАНИЯ СКОРОСТИ | 1973 |

|

SU374580A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| СУММАТОР С ПЕРЕМЕННЫМ МОДУЛЕМ СЛОЖЕНИЯ | 2000 |

|

RU2183347C2 |

| Устройство для сложения в избыточной двоичной системе | 1978 |

|

SU860064A2 |

| Устройство для сложения в избыточнойдВОичНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824201A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Устройство для сложения в избыточнойСиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824198A1 |

J 5 б 7 д

Фиг.2

Авторы

Даты

1973-01-01—Публикация