Изобретение относится к технике передачи дискретных сигналов и предназначено для использования как в радиолиниях, так и в проводных линиях связи для синхронной передачи данных, с применением многопозиционных видов манипуляции и избыточного кодирования, а также с применением шумоподобных сигналов с малой базой.

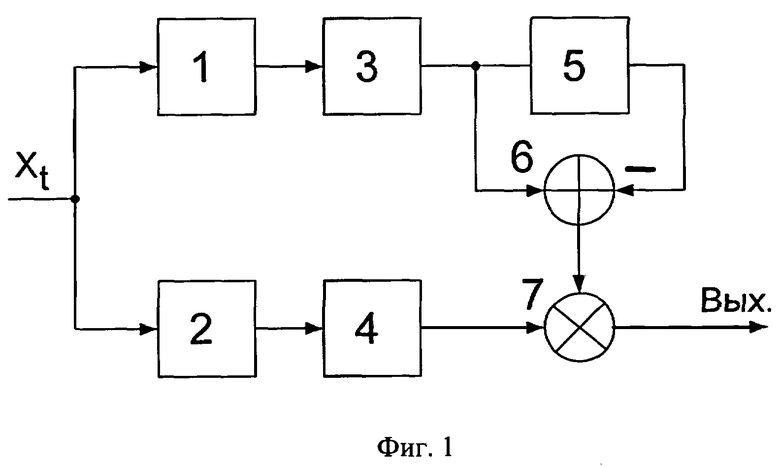

Известен оптимальный дискриминатор символьной синхронизации [1], показанный на фиг.1 и состоящий из элемента интегрирования 1 за время, равное длительности символа Т, элемента интегрирования 2 за время τ0, нелинейного элемента 3, элемента задержки 4 на время Т-τ0/2, элемента задержки 5 на длительность Т, блока вычитания 6 и блока умножения 7, выход которого является выходом дискриминатора.

Основными недостатками этого устройства являются следующие:

- элемент 1 структурной схемы выносит решение о принятом символе, элементы 3, 5, 6 фиксируют моменты смены символов, переходы через ноль и направление переходов, в связи с чем выходной сигнал дискриминатора зависит от принятого решения, возникает обратная связь по решению, которая приводит к потере работоспособности дискриминатора при низких, меньших единицы, отношениях сигнал/шум на символ информации;

- оптимальный дискриминатор не предназначен для работы с сигналами многопозиционных видов манипуляциии.

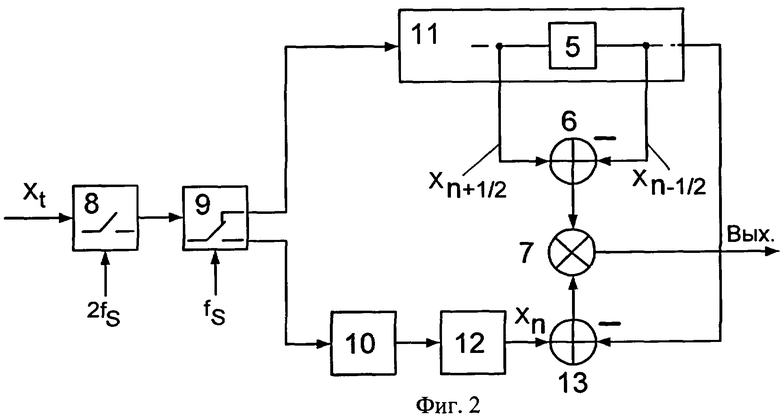

Наиболее близким, принятым за прототип, является фазовый детектор такта по модифицированному способу Гарднера [2], показанный на фиг.2 и содержащий демультиплексор 9, к входу которого подведен сигнал и который образует главные значения отсчета с интервалом длительности символа Т сигнала и выдает на первую ветвь с первым элементом задержки 5 на длительность Т, к входу и выходу которого подключен первый блок вычитания 6, и который дополнительно образует лежащие соответственно между двумя главными значениями отсчета промежуточные значения отсчета и выдает на вторую ветвь со вторым элементом задержки 12 на длительность Т/2, блок умножения 7, к первому входу которого через вторую ветвь подводят задержанное промежуточное значение отсчета и второй вход которого соединен с выходом первого блока вычитания 6, объединяющего соседние главные значения отсчета, причем с выхода блока умножения 7 снимается фазовый критерий такта, дополнительно в первую ветвь включен трансверсальный фильтр 11, элементы задержки которого содержат первый элемент задержки 5, во второй ветви предусмотрен дополнительный элемент задержки 10, предусмотрен дополнительный блок вычитания 13, входы которого поключены соответственно к выходу трансверсального фильтра 11 и к выходу элемента задержки 12 на длительность Т/2, к которому приложено задержанное во второй ветви промежуточное значение отсчета, причем выход дополнительного блока вычитания 13 соединен с первым входом блока умножения.

На фиг.2 также показан дискретизатор 8, который является составной частью устройств символьной синхронизации.

Фазовый детектор такта по модифицированному способу Гарднера получения фазового критерия (результата фазового детектирования) такта обладает недостаточной помехозащищенностью, а также имеет потери фазового критерия при обработке сигналов с многопозиционными видами манипуляции.

Причины недостаточной помехозащищенности заключаются в следующем.

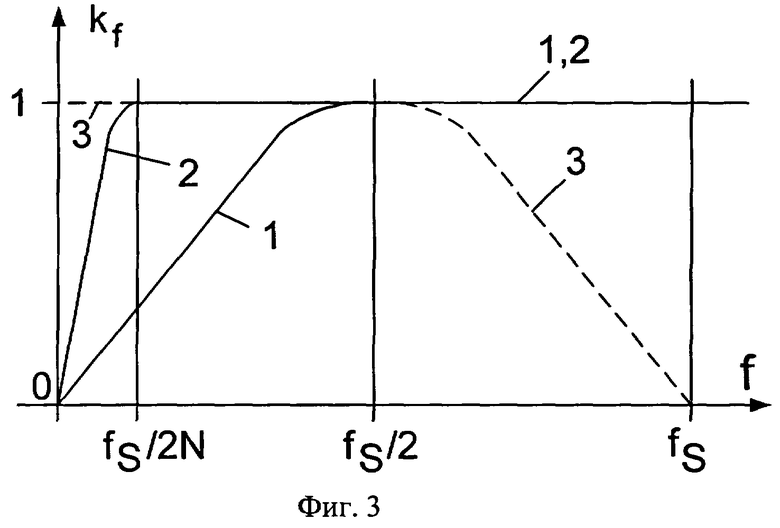

На один из входов блока умножения 7 фиг.2 поступает сигнал с блока вычитания 6, который совместно с элементом задержки 5 осуществляет операцию дифференцирования входного сигнала или его высокочастотную фильтрацию. Таким образом сигнал, поступающий на вход блока умножения 7, не содержит в своем составе низкочастотных спектральных составляющих шума (помех), имеющихся в сигнале, который поступает на вход дискретизатора 8. Амплитудно-частотная характеристика (АЧХ) 1 такого фильтра приведена на фиг.3, на которой также приведена АЧХ 3 канального фильтра низких частот, согласованного с шириной полосы принимаемого сигнала и расположенного на пути его следования.

При суперпозиции этих двух фильтров на перемножитель поступает оптимальный сигнал с максимумом спектра на полутактовой частоте (тактовая частота в спектре принимаемого сигнала отсутствует), тем самым достигается предварительная фильтрация верхней ветви перед нелинейной обработкой сигнала.

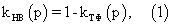

На другой вход блока умножения 7 фиг.2 поступает сигнал с блока вычитания 13, АЧХ на выходе которого определяется передаточной характеристикой трансверсального фильтра, включенного в цепь обратной связи по входному сигналу. Комплексный коэффициент передачи нижней ветви при этом имеет вид:

где р=jω - комплексный оператор, ω - угловая частота,

kТФ(p) - комплексный коэффициент передачи трансверсального фильтра.

Из формулы 1 видно, что АЧХ нижней ветви имеет зеркальное отражение относительно частоты среза АЧХ трансверсального фильтра (график 2 фиг.3), то есть когда полоса задержания нижней ветви определяется полосой пропускания трансверсального фильтра и зависит от его длины или количества звеньев N. Значение полосы задержания нижней ветви в N раз меньше верхней, что в целом снижает потенциальную помехозащищенность устройства. Увеличение количества звеньев трансверсального фильтра приводит к уменьшению его полосы пропускания и, как следствие, к уменьшению полосы защиты от воздействия канальных помех, а уменьшение - к зависимости от структуры сигнала.

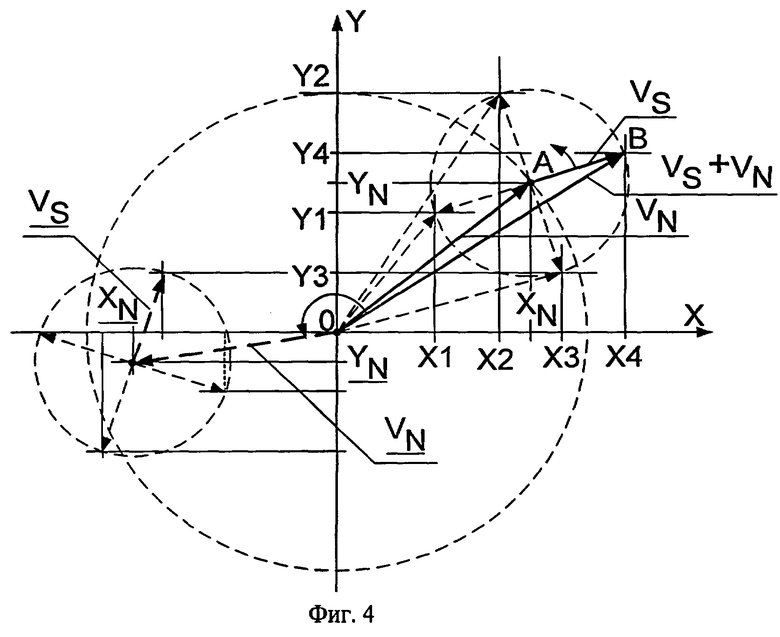

Потери фазового критерия при обработке сигналов с многопозиционными видами манипуляции также связаны с инерционностью фильтра в цепи обратной связи нижней ветви. Потери фазового критерия поясняются векторной диаграммой фиг.4 и временной диаграммой фиг.5.

На фиг.4 показан вариант расположения на комплексной плоскости векторов сигнала и шума при квадратурной четырехпозиционной фазовой манипуляции для некогерентной обработки сигнала, при отрицательном отношении сигнал/шум, где:

- VS - вектор сигнала;

- VN - вектор шума;

- VS+Vn - суммарный вектор сигнала и шума;

- Xn - проекция вектора шума на действительную ось;

- Yn - проекция вектора шума на мнимую ось;

- X1...Х4 - проекции суммарного вектора на действительную ось;

- Y1...Y4 - проекции суммарного вектора на мнимую ось;

-  - вектор сигнала для другого момента времени;

- вектор сигнала для другого момента времени;

-  - вектор шума для другого момента времени;

- вектор шума для другого момента времени;

-  - проекция вектора шума на действительную ось для другого момента времени;

- проекция вектора шума на действительную ось для другого момента времени;

-  - проекция вектора шума на мнимую ось для другого момента времени.

- проекция вектора шума на мнимую ось для другого момента времени.

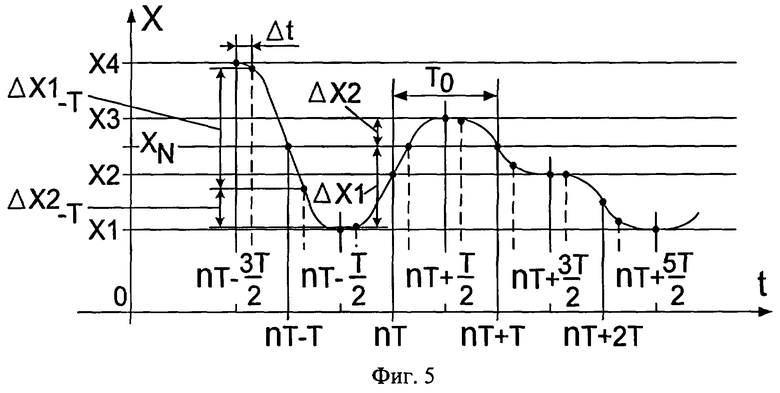

На временной диаграмме фиг.5 показан вариант проекции X(t) суммарного вектора сигнала и шума на действительную ось при четырехпозиционной фазовой манипуляции, где:

- nТ-Т/2 и nT+T/2 - моменты времени образования главных значений отсчетов сигнала;

- nT - моменты времени образования промежуточных значений отсчетов сигнала.

Трансверсальный фильтр в этом случае успевает отслеживать медленно меняющийся вектор шума. В моменты времени nT и (n+2)Т по модифицированному способу Гарднера получения фазового критерия такта будут возникать ошибки, равные:

δ(nТ)=(Х1-Х3)((Х2-ХN);

δ(nТ+2Т)=(Х2-X1)([Х(nТ+2Т)-XN].

Эти ошибки имеют разные знаки, суммарное значение ошибок определения фазового критерия в конечном итоге на длительном интервале времени будет стремиться к нулю. Среднеквадратическое значение величин ошибок указывает на количественные потери фазового критерия при обработке сигналов с многопозиционными видами манипуляции, и которое приводит к снижению крутизны фазового детектора и его помехозащищенности.

Предложены два варианта дифференциального фазового дискриминатора символьной синхронизации.

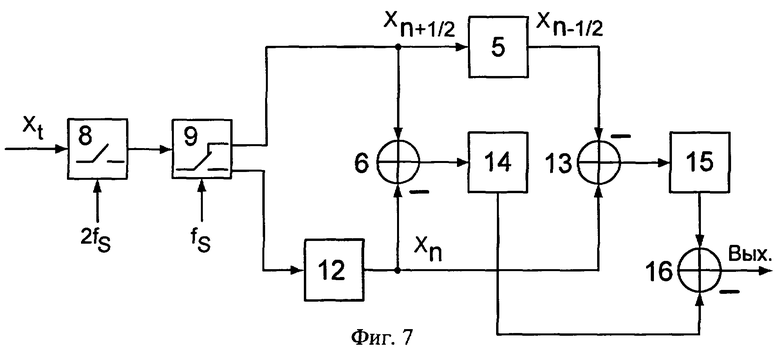

Первый вариант (п.1 формулы) дифференциального фазового дискриминатора содержит первый элемент задержки на длительность Т, второй элемент задержки на длительность Т/2, первый и второй блоки вычитания, первые входы которых соединены соответственно с входом первого элемента задержки и выходом второго элемента задержки, демультиплексор, к входу которого подведен сигнал, и который образует главные значения отсчета сигнала с интервалом длительности символа Т первой ветви с первьм элементом задержки на длительность Т, и который дополнительно образует лежащие соответственно между двумя главными значениями отсчета промежуточные значения отсчета сигнала второй ветви со вторым элементом задержки на длительность Т/2, отличающийся тем, что дополнительно содержит первый и второй квадраторы, третий блок вычитания, причем первый выход демультиплексора ветви главных отсчетов соединен с входом первого элемента задержки на длительность Т и первым входом первого блока вычитания, а второй выход демультиплексора ветви промежуточных отсчетов соединен с входом второго элемента задержки на длительность Т/2, выход которого соединен со вторым входом первого блока вычитания, выход первого элемента задержки на длительность Т соединен со вторым входом второго блока вычитания, выходы первого и второго блоков вычитания соединены соответственно со входами первого и второго квадраторов, выход первого квадратора соединен с первым входом третьего блока вычитания, а выход второго квадратора соединен со вторым входом третьего блока вычитания, выход которого является выходом устройства.

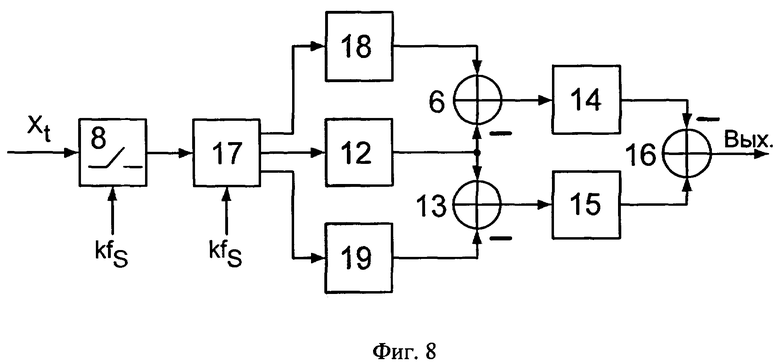

Второй вариант дифференциального фазового дискриминатора символьной синхронизации (п.2 формулы) содержит первый и второй блоки вычитания, второй элемент задержки на длительность Т/2, выход которого соединен с первым входом второго блока вычитания, отличающийся тем, что дополнительно содержит третий блок вычитания, первый и второй квадраторы, третий элемент задержки на длительность Т/2+τ0, четвертый элемент задержки на длительность Т/2-τ0, формирователь-распределитель суммарных опережающих, суммарных промежуточных и суммарных задержанных отсчетов сигнала, вход которого является входом устройства, а выход опережающих отсчетов формирователя-распределителя соединен с входом третьего элемента задержки на длительность Т/2+τ0, выход которого соединен с первым входом первого блока вычитания, выход промежуточных отсчетов формирователя-распределителя соединен с входом второго элемента задержки на длительность Т/2, выход которого соединен со вторым входом первого блока вычитания, выход задержанных отсчетов формирователя-распределителя соединен с входом четвертого элемента задержки на длительность Т/2-τ0, выход которого соединен со вторым входом второго блока вычитания, выходы первого и второго блоков вычитания соединены соответственно со входами первого и второго квадраторов, выход первого квадратора соединен с первым входом третьего блока вычитания, а выход второго квадратора соединен со вторым входом третьего блока вычитания, выход которого является выходом устройства.

Предлагаемые варианты фазового дискриминатора позволяют по сравнению с прототипом повысить помехозащищенность фазового детектирования тактовой частоты символов при обработке сигналов с многопозиционными видами модуляции.

Достижение технического результата первого варианта фазового дискриминатора определяется совокупностью следующих существенных признаков:

- наличие демультиплексора в фазовом дискриминаторе и фазовом детекторе такта прототипа, который образует главные значения отсчетов сигнала на длительности символа Т и дополнительные, лежащие посредине между этими главными значениями, промежуточные значения отсчетов сигнала;

- наличие первого и второго элементов задержки в фазовом дискриминаторе и фазовом детекторе такта прототипа, которые приводят к единому моменту времени значения двух главных и промежуточного отсчетов сигнала;

- наличие первого блока вычитания, который в отличие от прототипа образует разность между первым главным отсчетом сигнала и промежуточным отсчетом сигнала;

- наличие второго блока вычитания, который в отличие от прототипа образует разность между промежуточным отсчетом сигнала и вторым главным отсчетом сигнала;

- наличие дополнительных первого и второго квадраторов, которые производят квадрирование сигналов с выходов первого и второго блоков вычитания;

- наличие дополнительного третьего блока вычитания, который образует разность сигналов с выхода первого и второго квадраторов, которая является выходным сигналом дискриминатора;

- соединение составляющих элементов фазового дискриминатора однозначно определено.

Анализ перечисленных признаков первого варианта фазового дискриминатора показывает, что их совокупность является достаточной для достижения технического результата и характеризует предложение, как законченное техническое решение.

Достижение технического результата второго варианта фазового дискриминатора определяется совокупностью следующих существенных признаков:

- наличие в фазовом дискриминаторе формирователя-распределителя, который, в отличие от демультиплексора прототипа, при более высокой входной тактовой частоте образует суммарные опережающие, суммарные промежуточные и суммарные задержанные отсчеты сигнала;

- наличие в фазовом дискриминаторе, что связано с работой формирователя-распределителя отсчетов, трех элементов задержки, которые приводят к единому моменту времени значения опережающего, промежуточного и задержанного отсчетов сигнала;

- наличие первого блока вычитания, который в отличие от прототипа образует разность между опережающим отсчетом сигнала и промежуточным отсчетом сигнала;

- наличие второго блока вычитания, который в отличие от прототипа образует разность между промежуточным отсчетом сигнала и задержанным отсчетом сигнала;

- наличие дополнительных первого и второго квадраторов, которые производят квадрирование сигналов с выходов первого и второго блоков вычитания;

- наличие дополнительного третьего блока вычитания, который образует разность сигналов с выхода первого и второго квадраторов, которая является выходным сигналом дискриминатора;

- соединение составляющих элементов фазового дискриминатора однозначно определено.

Анализ перечисленных признаков второго варианта фазового дискриминатора показывает, что для достижения технического результата их совокупность не требует добавления других признаков, то есть является достаточной и характеризует предложение, как законченное техническое решение.

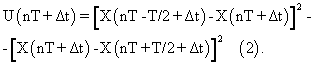

Получение фазового критерия на выходе первого варианта дифференциального фазового дискриминатора поясняется временной диаграммой фиг.5 варианта проекции X(t) суммарного вектора сигнала и шума на действительную ось при четырехпозиционной фазовой манипуляции, где

- ΔХ1- разность между главным значением отсчета сигнала Х(nТ-Т/2+Δt) и промежуточным значением отсчета сигнала X(nT+Δt);

- ΔХ2 - разность между промежуточным значением отсчета сигнала Х(nТ+Δt) и главным значением отсчета сигнала X(nT+Т/2+Δt);

- ΔХ1(-Т), ΔХ2(-Т) - первая и вторая разности при сдвиге главных и промежуточного значений отсчетов сигнала на интервал времени минус Т. Квадрированные разности ΔХ1 и ΔХ2 всегда имеют положительное значение и при Δt=0 равны друг другу, при этом разность между ними и фазовый критерий становятся равными нулю. Разность сигналов на выходах квадраторов при фазовом сдвиге дает однозначный фазовый критерий, который имеет вид:

Квадрирование первой и второй разностей отсчетов сигнала может быть при небольшой потере помехозащищенности заменено выполнением нелинейной операции получения их абсолютного значения (модулей).

Дискриминационная характеристика фазового дискриминатора в зависимости от разности фаз имеет синусоидальную форму, а при абсолютных значениях первой и второй разностей - пилообразную, экстремумы которой находятся в точках разности фаз - π/2 и +π/2. При входном сигнале прямоугольной формы дискриминационная характеристика становится релейной.

При использовании квадратурных видов модуляции фазовый критерий образуется путем суммирования фазовых критериев мнимой Y(t) и действительной X(t) проекций сигнала.

Получение разностей ΔХ1 и ΔХ2 (дифференцирование сигнала) максимально защищает (фильтрует) фазовый критерий от низкочастотных составляющих шумового спектра и при этом не возникает потерь при обработке сигналов с многопозиционными видами манипуляции, присущих прототипу. Дифференцирование сигнала производит смещение отрезков колебаний полутактовой частоты в моменты смены позиций символов к нулю, чем достигается предварительная фильтрация, исключение низкочастотных составляющих шумового спектра перед нелинейной обработкой сигнала.

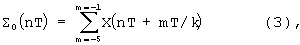

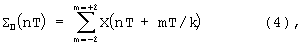

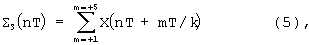

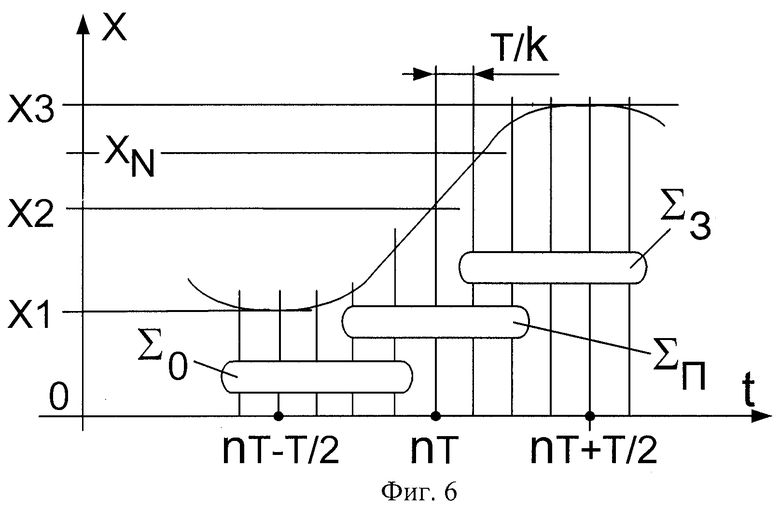

Для защиты фазового критерия от высокочастотных составляющих шумового спектра, прошедших через канальный фильтр, а также для ослабления требований к его исполнению, во втором варианте фазового дискриминатора дополнительно предусмотрена низкочастотная фильтрация, осуществляемая путем увеличения частоты дискретизации в k раз и замены главных и промежуточных значений отсчетов сигнала на суммарные опережающие, суммарные задержанные и суммарные промежуточные. Образование суммарных опережающих, задержанных и промежуточных значений отсчетов сигнала при k=8 поясняется временной диаграммой, показанной на фиг.6. Суммарные опережающие, промежуточные и задержанные значения отсчетов сигнала при этом определяются выражениями:

где m - целое число, принимающее в данном случае значения от -5 до +5. Из временной диаграммы, показанной на фиг.6, видно, что диапазон суммирования превышает длительность элемента Т, дальнейшее расширение диапазона суммирования нежелательно, так как при этом возникает зависимость фазового критерия от структуры сигнала. В данном случае длительность третьего и четвертого элементов задержки будет определяться при τ0=3Т/4.

На основании изложенного выше каждый из предложенных вариантов дифференциального фазового дискриминатора обладает по сравнению с прототипом более повышенной помехозащищенностью, основанной на высокочастотной фильтрации входного сигнала. Второй вариант более сложен для осуществления, но при этом обладает преимуществом по сравнению с первым, так как в нем дополнительно предусмотрена низкочастотная фильтрация входного сигнала для защиты фазового критерия от высокочастотных составляющих шумового спектра, прошедших через канальный фильтр. При применении того или иного варианта фазового дискриминатора в устройствах символьной синхронизации, в которых предусмотрен оптимальный канальный фильтр, их технические результаты становятся соизмеримыми. Таким образом, каждый из предложенных вариантов фазового дискриминатора является самостоятельным изобретением, но при этом они связаны между собой единым замыслом.

Для пояснения предложенных вариантов дифференциального фазового дискриминатора символьной синхронизации приводятся следующие фигуры:

- Фиг. 5. Временная диаграмма проекции суммарного вектора сигнала и шума на действительную ось при четырехпозиционной фазовой манипуляции.

- Фиг. 6. Временная диаграмма работы формирователя-распределителя суммарных опережающих, суммарных промежуточных и суммарных задержанных отсчетов сигнала.

- Фиг. 7. Структурная схема первого варианта дифференциального фазового дискриминатора.

- Фиг. 8. Структурная схема второго варианта дифференциального фазового дискриминатора.

Предложенный первый вариант дифференциального фазового дискриминатора символьной синхронизации, см. фиг.7, содержит:

5 - первый элемент задержки на длительность Т;

6 - первый блок вычитания;

9 - демультиплексор;

12 - второй элемент задержки на длительность Т/2;

13 - второй блок вычитания;

14 - первый квадратор;

15 - второй квадратор;

16 - третий блок вычитания.

Вход демультиплексора 9 является входом фазового дискриминатора, первый выход которого соединен с первым входом первого блока вычитания 6 и входом первого элемента задержки 5 на длительность Т, а второй выход демультиплексора 9 соединен с входом второго элемента задержки 12 на длительность Т/2, выход которого соединен со вторым входом первого блока вычитания 6 и первым входом второго блока вычитания 13, выход первого элемента задержки 5 на длительность Т соединен со вторым входом второго блока вычитания 13, выходы первого и второго блоков вычитания соединены соответственно со входами первого 14 и второго 15 квадраторов, выход первого квадратора 14 соединен с первым входом третьего блока вычитания 16, а выход второго квадратора 15 соединен со вторым входом третьего блока вычитания 16, выход которого является выходом фазового дискриминатора.

Полярность включения блоков вычитания на фиг.7 показана условно, так как работа дискриминатора не зависит от полярности включения первого и второго блоков вычитания, а полярность включения третьего блока вычитания будет определяться конкретным устройством символьной синхронизации. Указанный на фиг.7 дискретизатор 8 является составной частью устройства символьной синхронизации.

Работа первого варианта фазового дискриминатора поясняется временной диаграммой, приведенной на фиг.5. Фазовый дискриминатор работает следующим образом: отфильтрованный сигнал X(t) поступает с выхода канального фильтра на вход дискретизатора 8, который производит отсчеты (выборки) сигнала с удвоенной тактовой частотой 2fS, демультиплексор 9 разделяет эти выборки на главные и промежуточные с тактовой частотой fS; первый элемент задержки 5 главных значений отсчетов на длительность Т и второй элемент задержки 12 промежуточных значений отсчетов на длительность Т/2 приводят первые и вторые главные значения отсчетов сигнала и промежуточные значения отсчетов сигнала к одному моменту времени, в который с помощью первого 6 и второго 13 блоков вычитания производится получение разности ΔХ1 между главным значением отсчета Х(nТ-Т/2+Δt) сигнала и промежуточным значением отсчета Х(nТ+Δt) сигнала и разности ΔХ2 между промежуточным значением отсчета X(nT+Δt) сигнала и вторым, главным значением отсчета X(nT+Т/2+Δt) сигнала. На выходах первого 14 и второго 15 квадраторов образуются квадрированные первая ΔХ1 и вторая ΔХ2 разности сигнала, в тоже время на выходе третьего блока вычитания 16 образуется третья разность между квадрированными первой ΔХ1 и второй ΔХ2 разностями, которая является фазовым критерием. Процесс получения фазового критерия периодически повторяется с интервалом времени, который определяется управляемым тактовым генератором, период которого соизмерим с длительностью символа Т.

Предложенный второй вариант дифференциального фазового дискриминатора символьной синхронизации, см. фиг.8, содержит:

6 - первый блок вычитания;

12 - второй элемент задержки на длительность Т/2;

13 - второй блок вычитания;

14 - первый квадратор;

15 - второй квадратор;

16 - третий блок вычитания;

17 - формирователь-распределитель суммарных опережающих, суммарных промежуточных и суммарных задержанных отсчетов сигнала;

18 - третий элемент задержки на длительность Т/2+τ0;

19 - четвертый элемент задержки на длительность Т/2-τ0.

Вход формирователя-распределителя 17 является входом фазового дискриминатора, выход опережающих отсчетов формирователя-распределителя соединен с входом третьего элемента задержки 18 на длительность Т/2+τ0, выход которого соединен с первым входом первого блока вычитания 6, выход промежуточных отсчетов формирователя-распределителя соединен с входом второго элемента задержки 12 на длительность Т/2, выход которого соединен со вторым входом первого блока вычитания 6 и с первым входом второго блока вычитания 13, выход задержанных отсчетов формирователя-распределителя соединен с входом четвертого элемента задержки 19 на длительность Т/2-τ0, выход которого соединен со вторым входом второго блока вычитания 13, выходы первого 6 и второго 13 блоков вычитания соединены соответственно со входами первого 14 и второго 15 квадраторов, выход первого квадратора 14 соединен с первым входом третьего блока вычитания 16, а выход второго квадратора 15 соединен со вторым входом третьего блока вычитания 16, выход которого является выходом устройства.

Второй вариант фазового дискриминатора работает следующим образом: отфильтрованный сигнал X(t) поступает с выхода канального фильтра на вход дискретизатора 8, который производит отсчеты сигнала с повышенной тактовой частотой kfS; формирователь-распределитель, образует суммарные опережающие, суммарные промежуточные и суммарные задержанные отсчеты сигнала в соответствии с временной диаграммой фиг.6; третий 18, второй 12 и четвертый 19 элементы задержки приводят опережающие, промежуточные и задержанные отсчеты сигнала к одному моменту времени; в дальнейшем работа второго варианта фазового дискриминатора аналогична работе первого.

В качестве дискретизатора могут быть использованы аналого-цифровые преобразователи (АЦП) отечественного или зарубежного производства, которые являются неотъемлемой частью устройств цифровой обработки сигналов. В качестве формирователя-распределителя, образующего суммарные опережающие, суммарные промежуточные и суммарные задержанные отсчеты сигнала, может использоваться как накапливающий сумматор со сбросом, так и трансверсальный фильтр.

Дифференциальный фазовый дискриминатор символьной синхронизации может является составной частью устройств цифровой обработки сигналов, выполненных на основе программируемых логических интегральных схем (ПЛИС), базовых матричных кристаллах (БМК) или сигнальных процессоров.

Реально достижимые экспериментальные результаты, а именно среднеквадратическое отклонение фазы тактовой частоты, при использовании предложенных вариантов дифференциального фазового дискриминатора в устройстве символьной синхронизации при соотношении сигнал/шум на входе, равном минус 6 дБ, составляет не более 0,1 радиана в полосе частот от 20 Гц до 3,4 кГц. При использовании прототипа в тех же равных условиях тот же результат наблюдается при соотношении сигнал/шум на входе, равном минус 2 дБ.

Таким образом, предлагаемые варианты дифференциального фазового дискриминатора позволяют повысить помехозащищенность фазового детектирования тактовой частоты по сравнению с прототипом не менее чем на 4 дБ.

Источники информации

1. Справочник. Цифровые радиоприемные системы/ Под ред. М.И. Жодзишского. Москва, Радио и связь, 1990 г., с.114, рис.5.4;

2. Бертольд Ланкл (DE), Георг Зебальд (DE). Фазовый детектор такта. Патент RU 2115252 (Прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШУМОПОДОБНЫХ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2006 |

|

RU2313184C1 |

| ФАЗОВЫЙ ДЕТЕКТОР ТАКТА | 1993 |

|

RU2115252C1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ С НЕПРЕРЫВНОЙ ФАЗОЙ | 2006 |

|

RU2323536C1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ | 2010 |

|

RU2423798C1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ВРЕМЕННОЙ ЗАДЕРЖКОЙ СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1999 |

|

RU2157593C1 |

| СПОСОБ КОРРЕЛЯЦИОННОГО ПРИЁМА СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2237978C2 |

| ВРЕМЕННОЙ ДИСКРИМИНАТОР УСТРОЙСТВА ТАКТОВОЙ СИНХРОНИЗАЦИИ | 2006 |

|

RU2314646C1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1997 |

|

RU2127954C1 |

| РАДИОМОДЕМ | 2010 |

|

RU2460215C1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

Изобретение относится к технике передачи дискретных сигналов и предназначено для использования как в радиолиниях, так и в проводных линиях связи для синхронной передачи данных с применением многопозиционных видов манипуляции и избыточного кодирования, а также с применением шумоподобных сигналов с малой базой. Техническим результатом является повышение помехозащищенности фазового дискриминатора и устройств символьной синхронизации, выполненных на их основе. Устройство по первому варианту содержит демультиплексор, два элемента задержки, два блока вычитания, два квадратора. Устройство по второму варианту содержит формирователь-распределитель суммарных опережающих, суммарных промежуточных и суммарных задержанных отсчетов сигнала, три элемента задержки, три блока вычитания, два квадратора. 8 ил.

| ФАЗОВЫЙ ДЕТЕКТОР ТАКТА | 1993 |

|

RU2115252C1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1997 |

|

RU2127954C1 |

| СПОСОБ И УСТРОЙСТВО ВОССТАНОВЛЕНИЯ ТАКТОВОЙ СИНХРОНИЗАЦИИ СИМВОЛОВ ИЗ ПРИНИМАЕМОГО СИНФАЗНОГО И ШИРОКОПОЛОСНОГО КВАДРАТУРНОГО СИГНАЛОВ | 1996 |

|

RU2145776C1 |

| Устройство символьной синхронизации | 1990 |

|

SU1775869A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1988 |

|

SU1757080A1 |

| Огнетушитель | 0 |

|

SU91A1 |

| Устройство электрической сигнализации | 1936 |

|

SU54322A1 |

| ВАГОНЕТКА | 0 |

|

SU366265A1 |

Авторы

Даты

2004-06-27—Публикация

2002-04-16—Подача