Изобретение относится к электротехнике и может быть использовано в системах управления входными преобразователями электроподвижного состава переменного тока.

Известен способ формирования синхронизирующего сигнала, состоящий в том, что сигнал питающего напряжения пропускают через фильтр, полупериод его делят на равные интервалы, на которых форму сигнала заменяют его средним значением, и при его нулевом значении формируют синхронизирующий сигнал. Недостаток этого способа состоит в том, что он не обладает достаточной помехоустойчивостью. В случае появления в питающей сети помехи, форма и положение которой в каждом полупериоде одинаковы, формируется искаженная аппроксимированная функция, что приводит к ошибкам формирования синхронизирующего сигнала и, следовательно, к нарушениям работы силового преобразователя (см. авторское свидетельство СССР №945952, М. Кл. 3 Н 03 К 1/17, 1980 г.).

Наиболее близким по технической сущности является способ формирования синхронизирующего сигнала, заключающийся в том, что полупериод напряжения питающей сети делят на интервалы, в каждом интервале измеряют значение напряжения питающей сети, преобразуют его в цифровой код, определяют наличие искажения значения напряжения, при отсутствии искажений несколько раз подряд определяют экстраполированное значение напряжения питающей сети, сравнивают значение напряжения питающей сети с его экстраполированным значением, если расхождение допустимо, подают на дешифратор код введенного значения, если расхождение превышает допустимое значение, то подают на дешифратор код экстраполированного значения, и при значениях кода, соответствующих нулевому напряжению питающей сети, формируют синхронизирующий сигнал (см. авторское свидетельство СССР №1187252, кл. Н 03 К 5/13, Бюл. №39, 1985 г.).

Существенным недостатком этого способа является также низкая помехоустойчивость при сильно искаженной питающей сети и наличие высокочастотных помех, создаваемых работающим на участке контактной питающей сети современным э.п.с. с 4QS-преобразователями и автономными инверторами.

Задачей изобретения является повышение точности формирования синхронизирующего сигнала, позволяющее улучшить качество управления преобразователями тягового привода э.п.с.

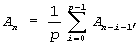

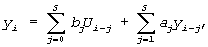

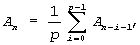

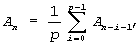

Поставленная задача решается способом управления, в котором, для формирования синхронизирующего сигнала, полупериод питающего напряжения делят на интервалы, в начале каждого i-го интервала измеряют напряжение питающей сети, преобразуют его в цифровой код Ui, который для повышения помехоустойчивости пропускают через цифровой фильтр. Цифровой фильтр формирует на своем выходе синусоидальный или близкий к нему сигнал yi, после чего определяют максимум (амплитуду) сигнала А за полупериод. За последние р полупериодов напряжения питающей сети определяют максимум сигнала напряжения питающей сети для текущего полупериода по формуле

где n - номер текущего полупериода;

р - количество предыдущих полупериодов;

А - максимальное значение сигнала в полупериоде.

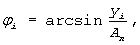

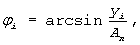

Затем определяют фазовый сдвиг введенного значения сигнала напряжения на текущем интервале относительно синхронизирующего сигнала по формуле

который сравнивают с необходимым

ϕi=ϕi-1+Δϕ,

где ϕi-1 - фазовый сдвиг на предыдущем интервале;

Δϕ - величина интервала.

При совпадении фазовых сдвигов несколько раз подряд в начале следующего интервала выводят фазовый сдвиг до конца полупериода питающего напряжения в таймер. При нулевом значении кода таймера в конце текущего полупериода формируют синхронизирующий сигнал, соответствующий моменту перехода питающего напряжения через ноль.

Предложенный способ существенно повышает точность формирования синхронизирующего сигнала при сильно искаженной питающей сети, что позволяет точнее реализовать необходимый угол нагрузки 4QS-преобразователя и повысить его коэффициент мощности.

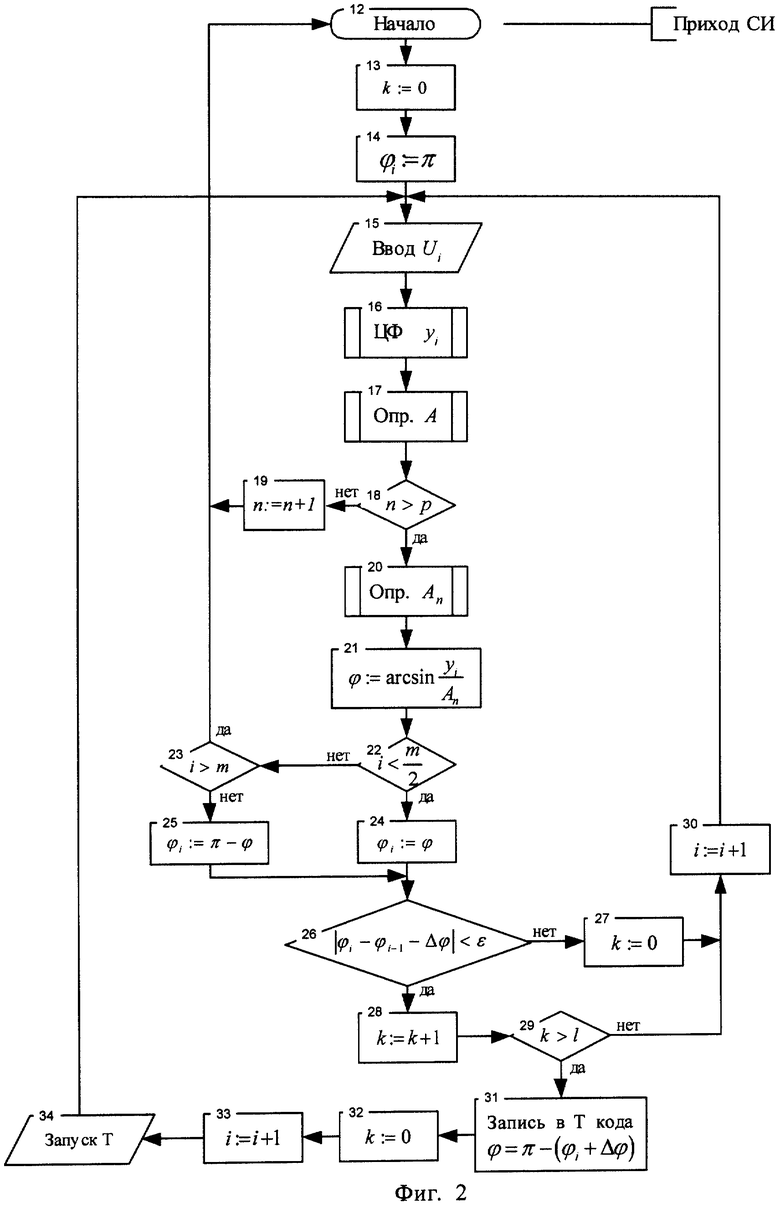

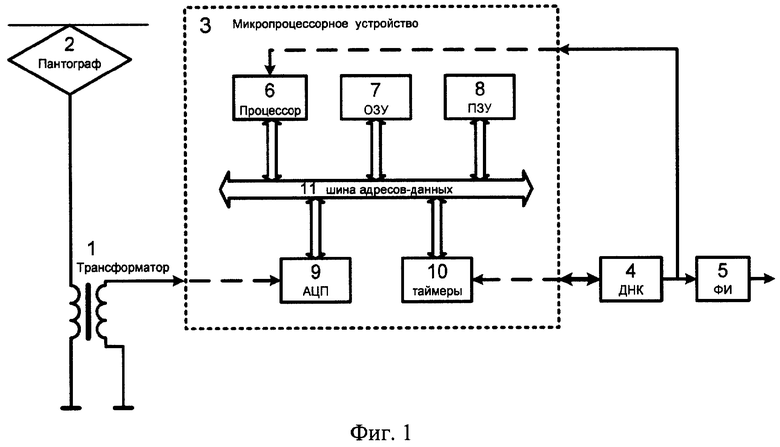

На фиг.1 изображено устройство для реализации предлагаемого способа, на фиг.2 - алгоритм работы устройства.

Устройство содержит трансформатор 1, первичная обмотка которого подключена к пантографу 2, а вторичная обмотка - к входу микропроцессорного устройства 3, выход которого соединен с входом дешифратора нулевого кода (ДНК) 4, выходом последнего соединенного с входом формирователя импульсов (ФИ) 5 и вторым входом устройства 3. Микропроцессорное устройство 3 состоит из процессора (П) 6, оперативного запоминающего устройства (ОЗУ) 7, постоянного запоминающего устройства (ПЗУ) 8, аналого-цифрового преобразователя (АЦП) 9, таймеров (Т) 10. Входы-выходы П 6, ОЗУ 7, ПЗУ 8, Т 10 и АЦП 9 соединены шиной адресов-данных 11. Выход ДНК 4 соединен с входами прерываний П 6.

П 6, ОЗУ 7, ПЗУ 8, АЦП 9, Т 10 могут быть интегрированы в цифровой сигнальный процессор из семейства TMS320LF24xx (Процессоры цифровой обработки сигналов фирмы Texas Instruments. // ЗАО "SCAN Инжиниринг - телеком", М., 2000 г., стр.31).

Способ реализуют следующим образом. При наличии напряжения питающей сети переменного тока на пантографе 2 во вторичной обмотке трансформатора 1 индуцируется э.д.с. На аналоговый вход устройства 3 подается напряжение, форма которого повторяет форму напряжения питающей сети. Устройство работает в соответствии с алгоритмом, занесенным в ПЗУ 8, приведенном на фиг.2, вычисляя момент перехода питающего напряжения через ноль, по которому ДНК 4 и ФИ 5 выдают синхронизирующий сигнал (СИ).

Каждый полупериод напряжения питающей сети делят на m интервалов, величина которого определяется по формуле

В каждом n-ом полупериоде напряжения питающей сети задают начальные значения переменных k=0, ϕ=π (180 эл. градусов) (блоки 13, 14), где k - число неискаженных интервалов синусоиды подряд;

ϕ - текущий фазовый сдвиг сигнала.

Напряжение питающей сети с помощью АЦП 9 на каждом i-интервале (блок 15) преобразуют в цифровой код Ui, вводят в П 6, запоминается в ОЗУ 7 и пропускают через цифровой фильтр (блок 16), выходной сигнал которого имеет синусоидальную или близкую к нему форму, и вычисляют по формуле

где S - порядок фильтра;

aj и bj - постоянные коэффициенты фильтра (например, для полосового цифрового фильтра второго порядка с полосой пропускания 49...51 Гц они следующие:

см. книгу: "Цифровая обработка сигналов."/ А.Б.Сергиенко - СПб.: Питер, 2003. - 604 с.).

В блоке 17 находят максимальное значение (амплитуда) сигнала А полупериода напряжения питающей сети, которое будет использоваться в вычислениях для следующего полупериода. Для текущего полупериода за максимальное значение амплитуды сигнала An принимается значение, вычисленное по формуле скользящего среднего за последние р полупериодов:

где n - номер текущего полупериода питающей сети (блоки 18...20).

Текущий фазовый сдвиг измеренного напряжения питающей сети вычисляют в блоке 21 по формуле

В блоках 22...25 определяют половину полупериода нахождения текущего интервала сигнала, если первая, то его фазовый сдвиг равен ϕi=ϕ (блок 24), если вторая, то его фазовый сдвиг вычисляют как

ϕi=π-ϕ (блок 25).

Фазовый сдвиг определен, если в каждом из l (блоки 26, 28, 27, 29) вычислений подряд выполняется условие

|ϕi-ϕi-1-Δϕ|<ε (блок 26),

где ε - допустимая ошибка вычисления фазового сдвига.

Если ошибка определения фазы между предыдущим и новым значением меньше допустимой, то производят коррекцию фазового сдвига по формуле

ϕ=π-(ϕi+Δϕ) (блок 31),

в противном случае считают, что произошел сбой, при этом обнуляют счетчик числа неискаженных интервалов синусоиды (блок 27), коррекцию фазового сдвига не производят, и переходят к следующему интервалу вычислений (блок 30). В Т 10 (блок 31) загружают код откорректированного фазового сдвига ϕ, обнуляют счетчик числа неискаженных интервалов (блок 32) и перезапускают Т 10 в начале следующего интервала (блоки 33, 34). ДНК 4 при нулевом значении кода в Т 10 формирует сигнал, поступающий на вход прерывания П 6 и ФИ 5. По сигналу прерывания П 6 начинает выполнять тот же самый алгоритм (с блока 12) для очередного полупериода питающего напряжения. ФИ 5 вырабатывает на своем выходе синхронизирующий сигнал с заданными параметрами.

Способ, исследованный на натурном стенде индукторного тягового привода, содержащем 4QS-преобразователь, автономный инвертор напряжения и тяговый трехфазный индукторный двигатель, питающийся от индукционного преобразователя, имитирующего контактную сеть, показал высокую помехоустойчивость и высокую точность формирования синхронизирующего сигнала, погрешность формирования которого составила не более 1...1,5 эл. градусов, что гораздо лучше, чем у применяемых на современном э.п.с. (5...10 и до 14 эл. градусов). Это повышает точность формирования углов управления преобразователями и, соответственно, улучшает их энергетические показатели.

Изобретение относится к электротехнике и может быть использовано в системах управления входными преобразователями электроподвижного состава. Технический результат - повышение помехоустойчивости при сильно искаженной питающей сети и наличии высокочастотных помех. Поставленная задача решается способом управления, в котором, для формирования синхронизирующего сигнала, полупериод питающего напряжения делят на интервалы, в начале каждого i-го интервала измеряют напряжение питающей сети, преобразуют его в цифровой код Ui, который для повышения помехоустойчивости пропускают через цифровой фильтр. Цифровой фильтр формирует на своем выходе синусоидальный или близкий к нему сигнал yi, после чего определяют максимум (амплитуду) сигнала А за полупериод. За последние р полупериодов напряжения питающей сети определяют максимум сигнала напряжения питающей сети для текущего полупериода по формуле

где n - номер текущего полупериода; р - количество предыдущих полупериодов; А - максимальное значение сигнала в полупериоде. Затем определяют фазовый сдвиг введенного сигнала напряжения на текущем интервале относительно синхронизирующего сигнала по формуле

который сравнивают с необходимым ϕi=ϕi-1+Δϕ, где ϕi-1 - фазовый сдвиг на предыдущем интервале; Δϕ - величина интервала. При совпадении фазовых сдвигов несколько раз подряд в начале следующего интервала выводят фазовый сдвиг до конца полупериода питающего напряжения в таймер. При нулевом значении кода таймера в конце текущего полупериода формируют синхронизирующий сигнал, соответствующий моменту перехода питающего напряжения через ноль. 2 ил.

Способ формирования синхронизирующего сигнала, заключающийся в том, что делят полупериод напряжения питающей сети на интервалы, в начале каждого интервала измеряют напряжение питающей сети, преобразуют его в цифровой код, при значениях кода, соответствующих нулевому напряжению питающей сети, формируют синхронизирующий сигнал, отличающийся тем, что значения напряжения питающей сети пропускают через цифровой фильтр, определяют максимум напряжения питающей сети за полупериод, по последним полупериодам питающей сети определяют максимум напряжения питающей сети по формуле

где n - номер текущего полупериода;

р - количество предыдущих полупериодов;

А - максимальное значение амплитуды сигнала в полупериоде,

затем определяют фазовый сдвиг введенного значения напряжения питающей сети относительно синхронизирующего сигнала по формуле

где уi - сигнал с выхода цифрового фильтра, сравнивают полученный фазовый сдвиг с необходимым

ϕi=ϕi-1+Δϕ,

где ϕi-1 - фазовый сдвиг введенного значения напряжения питающей сети на предыдущем интервале;

Δϕ - величина интервала, и при совпадении фазовых сдвигов несколько раз подряд выводят в начале следующего интервала фазовый сдвиг до конца полупериода питающего напряжения  в таймер, код которого станет равным нулю в конце текущего полупериода.

в таймер, код которого станет равным нулю в конце текущего полупериода.

| Устройство для формирования синхронизирующего сигнала | 1983 |

|

SU1187252A1 |

| Устройство для формирования синхронизирующего сигнала | 1980 |

|

SU945952A1 |

| ФОРМИРОВАТЕЛЬ СИНХРОНИЗИРУЮЩИХ ИМПУЛЬСОВ | 1997 |

|

RU2118038C1 |

| ФОРМИРОВАТЕЛЬ СИНХРОНИЗИРУЮЩИХ ИМПУЛЬСОВ | 1996 |

|

RU2118037C1 |

| ФОРМИРОВАТЕЛЬ СИНХРОНИЗИРУЮЩИХ ИМПУЛЬСОВ | 2001 |

|

RU2183378C1 |

| US 4908754, А, 13.03.1990 | |||

| US 4680506, А, 14.07.1987. | |||

Авторы

Даты

2005-10-10—Публикация

2004-06-17—Подача