оо

00

ел

оо

2, Дешифратор по п. 1, отличающийся тем, что элемент заряда выполнен на-транзисторе р-тйпа, затвор которого является входом элемента заряда, исток - первым выходом, а сток - вторым выходом элемента заряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МДП-ТРАНЗИСТОРАХ | 1973 |

|

SU408374A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| ДЕШИФРАТОР | 2005 |

|

RU2307405C2 |

| Полупроводниковое запоминающее устройство | 1981 |

|

SU987679A1 |

| Формирователь импульсов на МДП-транзисторах | 1985 |

|

SU1569973A1 |

| Адресный формирователь на КМДП-транзисторах | 1985 |

|

SU1280451A1 |

| Дешифратор адреса | 1982 |

|

SU1068999A1 |

| D-триггер на КМДП-транзисторах | 1990 |

|

SU1728963A1 |

| Дешифратор на МДП-транзисторах | 1983 |

|

SU1455362A1 |

| Параллельный дешифратор на допол-НяющиХ Мдп-ТРАНзиСТОРАХ" | 1978 |

|

SU798997A1 |

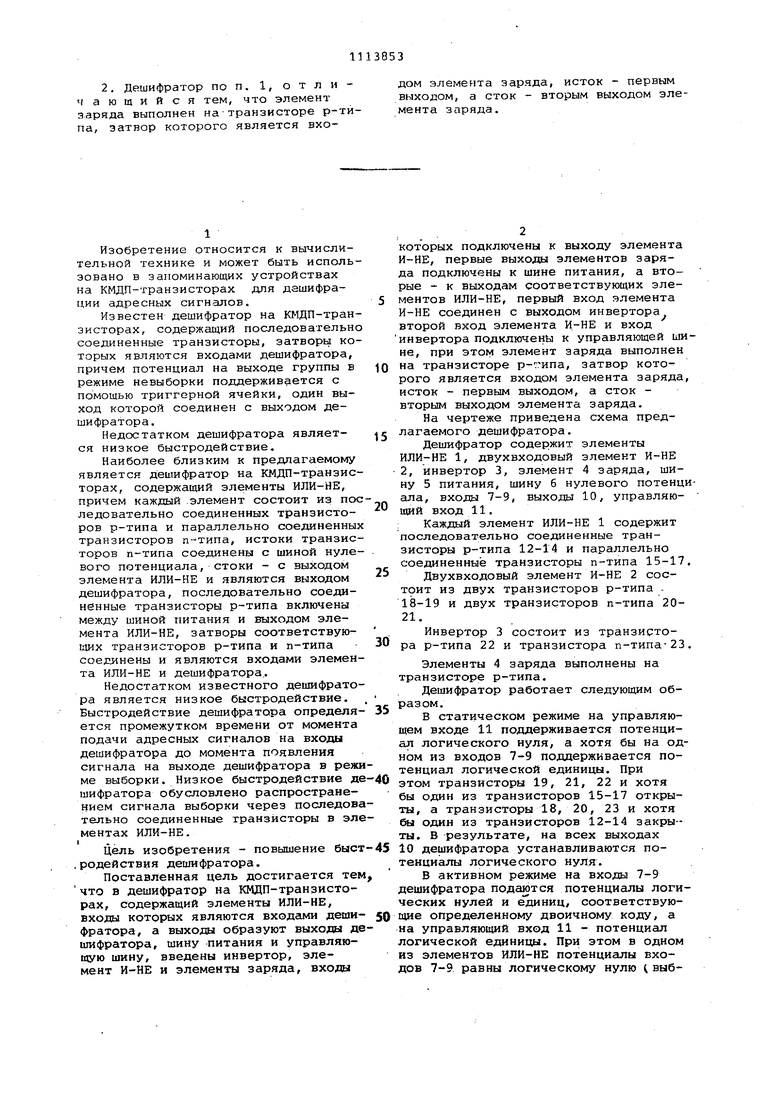

Изобретение относится к вычислительной технике и может быть исполь зовано в запоминающих устройствах на КМДП-транзисторах для дешифрации адресных сигналов. Известен дешифратор на КМДП-транзисторах, содержащий последовательно соединенные транзисторы, затворы которых являются входами дешифратора, причем потенциал на выходе группы в режиме невыборки поддерживается с помощью триггсрной ячейки, один выход которой соединен с выходом дешифратора. Недостатком дешифратора является низкое быстродействие. Наиболее близким к предлагаемому является д;ешифратор на КМДП-транзисторах, содержащий элементы ИЛИ-НЕ, причем каждый .элемент состоит из пос ледовательно соединенных транзисторов р-типа и параллельно соедщненных транзисторов п--типа, истоки транзис торов п-типа соединены с шиной нуле вого потенциала, стоки - с выходом элемента ИЛИ-НЕ и являются выходом дешифратора, последовательно соединенные транзисторы р-типа включены между шиной питания и выходом элемента ИЛИ-НЕ, затворы соответствующих транзисторов р-типа и п-типа соединены и являются входами элемента ИЛИ-НЕ и дешифратора.. Недостатком известного дешифрато ра является низкое быстродействие. Быстродействие дешифратора определяется промежутком времени от момента подачи адресных сигналов на входы дешифратора до момента появления сигнала на выходе дешифратора в режи ме выборки. Низкое быстродействие де шифратора обусловлено распространением сигнала выборки через последова тельно соединенные транзисторы в эле ментах ИЛИ-НЕ. I .. Цель изобретения - повышение быот .родействия дешифратора. Поставленная цель достигается тем что в дешифратор на КМДП-транзисторах, содержащий элементы ИЛИ-НЕ, входы которых являются входгили дешифратора, а выходы образуют выходы де шифратора, шину питания и управляющую шину, введены инвертор, элемент И-НЕ и элементы заряда, входы которых подключены к выходу элемента И-НЕ, первые выходы элементов заряда подключены к шине питания, а вторые - к выходам соответствующих элементов ИЛИ-НЕ, первый вход элемента И-НЕ соединен с выходом инвертора второй вход элемента И-НЕ и вход инвертора подключены к управляющей шине, при этом элемент заряда выполнен на транзисторе р-гипа, затвор которого является входом элемента заряда, исток - первым выходом, а сток вторым выходом элемента заряда. На чертеже приведена схема предлагаемого дешифратора. Дешифратор содержит элементы ИЛИ-НЕ 1, двухвходовый элемент И-НЕ 2, инвертор 3, элемент 4 заряда, шину 5 питания, шину б нулевого потенциала, входы 7-9, выходы 10, управляющий вход 11. : Каждый элемент ИЛИ-НЕ 1 содержит последовательно соединенные транзисторы р-типа 12-14 и параллельно соединенные транзисторы п-типа 15-17. Двухвходовый элемент И-НЕ 2 состоит из двух транзисторов р-типа 18-19 и двух транзисторов п-типа 2021. Инвертор 3 состоит из транзистора р-типа 22 и транзистора п-типа-23. Элементы 4 заряда выполнены на транзисторе р-типа. Дешифратор работает следующим образом. В статическом режиме на управляющем входе 11 поддерживается потенциал логического нуля, а хотя бы на одном из входов 7-9 поддерживается потенциал логической единицы. При этом транзисторы 19, 21, 22 и хотя бы один из транзисторов 15-17 открыты, а транзисторы 18, 20, 23 и хотя ал один из транзисторов 12-14 закрыты. В результате, на всех выходах 10 дешифратора устанавливаются потенциалы логического нуля. В активном режиме на входы 7-9 дешифратора подаются потенциалы логических нулей и единиц, соответствующие определенному двоичному коду, а на управляющий вход 11 - потенциал логической единицы. При этом в одном из элементов ИЛИ-НЕ потенциалы входов 7-9 равны логическому нулю ( выбранный элемент), а наборы потенциалов на входах всех остальных элементов ИЛИ-НЕ содержат хотя бы по о ной логиче ской единице (невыбранные элементы V Таким образом, в невыбра ных элементах ИЛИ-НЕ хотя бы один из транзисторов 15-17 оказывается открытым и хотя бы один из транзист ров 12-14 оказывается закрытым. В выбранном элементе все транзисторы 15-17 оказываются закрытыми, а тран зистор 12 - открытым, поскольку напряжение между затвором и истоком этого транзистора равно питающему напряжению. Транзисторы 13 и 14 выб ранного элемента открываются поочередно: когда напряжение между затвором и истоком транзистора 13 достигает порогового Напряжения этого транзистора, то он открывается, и так далее до транзистора 14 включительно. Появление потенциала логиче кой единицы на управляющем входе 11 приврлит к отпиранию транзисторов 20 и 23 и запиранию транзисторо 19 и 22. В результате, происходит уменьшение потенциала на выходе эле мента И-НЕ, что приводит к отпирани транзисторов элементов 4 заряда. От пирание транзистора элемента 4 заряда, соответствующего выбранному элементу ИЛИ-НЕ, приводит к повышению потенциала на выходе этого элемента и соответствующем выходе 10 д шифратора, при этом допустимо и неп ное формирование уровня логической единицы на выходе выбранного элемента j уровень, доформировыпается после включения группы последовательно соединенных транзисторов 12-14. Отпирание транзисторов элементов 4 заряда, соответствующих невыбранным элементам ИЛИ-НЕ, приводит лишь к незначительному повышению потенциала на выходах элементов, поскольку выходы элементов оказываются подключенными к шине 6 / нулевого потенциала через один или несколько открытых транзисторов 1517. После того как инвертор 3 переключится, т.е. потенциал выхода инвертора достигнет порога переключения элемента И-НЕ 2, потенциал выхода элемента И-НЕ начинает повьпиаться, что приводит к запиранию транзисторов элементов 4 заряда. Таким образом, в активном режиме на выходе выбранного элемента ИЛИ-НЕ дешифратора устанавливается уровень логической единицы, а на выходах невыбранных элементов - уровни логического нуля. Введение элементов заряда, инвертора и двухвходового элемента И-НЕ позволило ускорить процесс формирования сигнала логической единицы на выходе дешифратора, т.е. повысить быстродействие дешифратора. В результате, как показало моделирование на ЭВМ, предложенный дешифратор обладает в 2-2,5 раза более высоким быстродействием по сравнению с прототипом.

Авторы

Даты

1984-09-15—Публикация

1982-08-12—Подача