Изобретение относится к способам испытаний информационно-управляющих систем (далее ИУС), которые должны формировать необходимые управляющие команды в зависимости от условий обстановки, которые определяются поступающими на вход ИУС информационными сигналами, путем формирования и использования необходимых и достаточных испытательных тестов (наборы испытательных последовательностей информационных сигналов), сформированных по результатам математического планирования эксперимента. Технический результат способа позволит существенно сократить процесс испытаний ИУС. Способ и устройство проверки логики работы информационно-управляющих систем включает формирование совокупности необходимых и достаточных испытательных тестов, а также контроль допустимых отклонений времени формирования выходного сигнала для проверки соответствия ИУС заданным требованиям.

Известен способ формирования испытательных тестов электронных устройств [патент РФ №2469372] для испытаний электронных устройств различного назначения путем использования испытательных тестов (наборы испытательных воздействий и соответствующих им допустимых отклонений контролируемых параметров устройств), сформированных по результатам математического планирования эксперимента. Способ включает реализацию эксперимента с совокупностью устройств и построение математических моделей, отражающих влияние входных сигналов и эксплуатационных воздействий, а также внутренних факторов (разбросов параметров комплектующих элементов), используя которые (математические модели), формируют наборы воздействий и соответствующих им допустимых отклонений выходных параметров устройств (испытательные тесты) для проверки соответствия изготавливаемых устройств заданным требованиям.

Недостатком указанного способа является невозможность его использования для формирования испытательных последовательностей информационных сигналов для проведения испытаний ИУС.

Известен способ формирования испытательных тестов для испытаний автоматов [Айзерман М.А., Гусев Л.А., Розоноэр Л.И., Смирнова И.М., Таль А.А. «Логика. Автоматы. Алгоритмы.». Издательство «Физматгиз», Москва, 1963 г. ] включающий:

1) формирование и подачу на вход ИУС всех возможных последовательностей входных сигналов;

2) для всех последовательностей входных сигналов, содержащих хотя бы одно условие логической функции, ИУС своевременно сформирована правильная управляющая команда (нет пропусков из-за логики);

3) для всех последовательностей входных сигналов, не содержащих ни одного из условий логической функции, не сформирована управляющая команда (нет ложных тревог из-за логики обработки сигналов).

Недостатком данного способа являются необходимость формирования и подачи на вход ИУС всех возможных последовательностей входных сигналов. Суммарное число таких последовательностей для заданного числа входных сигналов с учетом сочетаний и перестановок (без повторений) довольно велико, но его несложно определить по приведенной зависимости:

,

,

где n - число входных сигналов,

! - знак факториала.

Так, например, для 7 входных сигналов необходимо сформировать и проверить около 26000 различных последовательностей, для 8 сигналов - более 45 тысяч и т.д. При этом критерием правильности логики работы ИУС является отсутствие ошибок первого и второго рода, то есть справедливо:

для любой последовательности входных сигналов, не содержащей условий логической функции, управляющая команда не вырабатывается;

управляющая команда вырабатывается при поступлении первого сигнала, сочетание которого с поступившими ранее сигналами данной последовательности образует одно из условий логической функции.

Перед проведением каждого испытания необходимо определить ожидаемый правильный результат для данной последовательности входных сигналов и ожидаемое время формирования управляющей команды при наступлении условий логической функции.

Однако в реальных условиях для проведения такого числа испытаний сложных ИУС может не хватить ни времени, ни материальных средств.

Целью изобретения является разработка способа и устройства формирования специального множества представительных последовательностей, которые должны содержать минимальные и достаточные последовательности входных сигналов, проверка на которых гарантировала бы правильную работу ИУС, как и полная совокупность.

Поставленная цель достигается тем, что предлагаемый способ формирует минимальное число последовательностей входных сигналов, проверка на которых гарантировала бы правильную работу ИУС, как и полная совокупность. Разработанное устройство реализует предлагаемый способ.

Рассмотрим информационно управляющую систему, которая должна формировать необходимые управляющие команды в зависимости от условий обстановки, которые определяются поступающими на вход ИУС информационными сигналами. Для обеспечения этой функции в ИУС «прошивается» логика, на основе соответствующей критериальной логической функции F(A). Данная функция зависит от булевых логических переменных Ai (i=1, 2, …, Ν), каждой из которой соответствует единственный входной информационный сигнал.

Пусть функция F(A) построена с использованием только знаков логических суммы и произведения: дизъюнкции (+) и конъюнкции (x), а знак логического отрицания при этом не применяется. Слагаемые функции F(A), далее называемые как логические условия, реализуют схему «ИЛИ», и представляют произведение некоторых переменных Ai (схема «И»). Получение ИУС i-го входного сигнала переводит переменную Ai в истинное событие, а после получения входного сигнала, образующего с предыдущими сигналами сочетание истинных событий, соответствующее одному из логических условий функции F(A), формируется и выдается необходимая управляющая команда в течение времени, не превышающего заданное.

В процессе создания (на этапе разработки), очевидно, по разным причинам (неправильное понимание разработчиками требований технического задания, ошибки программирования и др.) могут появиться два типа ошибок в реализации логики функционирования ИУС в различных условиях обстановки, которые необходимо выявить и устранить в ходе испытаний:

ошибки 1 рода (пропуск критических условий обстановки) - несвоевременно формируется или вообще не формируется необходимая управляющая команда при наступлении сочетания событий, соответствующей одному из условий логической функции F(A);

ошибки 2 рода (ложные тревоги) - формируется управляющая команда при наступлении сочетания событий, не соответствующей ни одному из условий логической функции F(A).

Вместе с тем справедливо предположить, что среди всех возможных последовательностей входных сигналов (все сочетания и перестановки) существуют избыточные, которые ничего нового не вносят в подтверждение правильности логики работы ИУС.

Будем называть критичным сочетание входных сигналов, содержащее хотя бы одно из условий логической функции. Соответственно, некритичным будет сочетание сигналов, не содержащее ни одного из условий логической функции.

Будем называть поглощаемой некритичную последовательность, если ее логические переменные полностью входят в состав хотя бы одного некритичного сочетания. Соответственно некритичное сочетание, переменные которой не входят полностью ни в одну некритичную последовательность, будем называть поглощающей.

Пример 1: Некритичное сочетание (А2-А4-А5) является поглощающим для 15 поглощаемых некритичных последовательностей: А2, А4, А5, А2-А4, А2-А5, А4-А2, А4-А5, А5-А2, А5-А4, А2-А4-А5, А2-А5-А4, А5-А2-А4, А5-А4-А2, А4-А2-А5, А4-А5-А2.

Нетрудно доказать, что испытания логики ИУС при подаче на вход поглощающей некритичной последовательности входных сигналов в любой последовательности эквивалентны проведению испытаний для всех входящих в нее поглощаемых некритичных последовательностей.

Утверждение 1. Если в процессе испытаний установлено, что одна из последовательностей поглощающего некритичного сочетания входных сигналов (А1, А2,…, Ai, …, AN) не переводит логическую функцию F(A) в истинное значение, то и все остальные возможные последовательности (перестановки) данного сочетания также не переводят логическую функцию F(A) в истинное значение.

Утверждение 1 вытекает из инвариантности условий логической функции F(A) к перестановкам переменных Ai.

Утверждение 2. Если в процессе испытаний установлено, что поглощающее некритичное сочетание входных сигналов (А1, А2, …, Ai, …, AN) не переводит логическую функцию F(A) в истинное значение, то и все поглощаемые им последовательности входных сигналов не переводят логическую функцию F(A) в истинное значение.

Утверждение 2 вытекает из двух положений:

поглощаемые последовательности или являются перестановками, или содержат подмножество входных сигналов данного поглощающего некритичного сочетания;

инвариантности условий логической функции F(A) к перестановкам переменных Ai.

Таким образом, проведя положительное испытание (отсутствие ложной тревоги) любой последовательности поглощающего некритичного сочетания входных сигналов можно утверждать, что и вся совокупность поглощаемых им последовательностей автоматически проверена с положительным результатом в процессе этого единственного испытания.

Утверждение 3. Для подтверждения правильности логики работы ИУС вместо полного перебора всех возможных последовательностей входных сигналов (сочетаний и перестановок) достаточно использовать в качестве тестов множество поглощающих некритичных сочетаний входных сигналов, а также каждое из условий логической функции.

Доказательство утверждения 3.

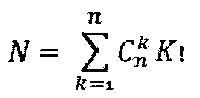

Для доказательства будем последовательно разбивать множество всех последовательностей на определенные подмножества и группы (см. Фиг 1).

Во-первых, выделим уже известные подмножества некритичных и критичных последовательностей. Ранее уже было доказано, что из-за инвариантности условий логической функции F(A) к перестановкам переменных Ai вместо некритичных последовательностей достаточно использовать в качестве тестов множество поглощающих некритичных сочетаний входных сигналов (в любой последовательности).

Во-вторых, из подмножества критичных последовательностей выделим группу №1, содержащую все последовательности, точно соответствующие каждому условию логической функции F(A). В силу инвариантности условий логической функции F(A) к перестановкам переменных Ai вместо критичных последовательностей из группы №1 достаточно использовать в качестве тестов соответствующие критичные сочетания данных входных сигналов (в любой последовательности). Таким образом, требуется провести с положительным результатом испытания отдельно по выполнению каждого условия логической функции F(A). Положительным результатом является отсутствие ошибок 1 рода (пропуска критических условий обстановки) и своевременное формирование необходимой управляющей команды при получении именно того входного сигнала (логической переменной), который в сочетании с предшествующими сигналами составляет проверяемое условие логической функции F(A).

Оставшееся подмножество последовательностей будем называть смешанными критичными, так как в каждой из них наряду с условиями логической функции F(A) содержатся и некритичные последовательности. Разделим это подмножество на три группы - №№ 2, 3 и 4.

В группу №2 включим последовательности, которые начинаются с одного из условий логической функции F(A). Данная группа не требует отдельных проверок, так как автоматически будет проверена при положительных результатах испытаний последовательностей группы №1.

В группу №3 включим те, которые начинаются с некритичной последовательности, за которой следуют переменные, соответствующие одному из условий логической функции F(A). Данная группа также не требует отдельных проверок, так как автоматически будет проверена при положительных результатах испытаний множества поглощающих некритичных сочетаний входных сигналов (в любой последовательности) и последовательностей группы №1.

Наконец, в группе №4 останутся те, которые начинаются с одной из некритичной последовательности, при этом в отличие от группы №3 за ней следует одна из переменных, которая в сочетании с одной или несколькими предшествующими переменными составляет одно из условий логической функции (концовка последовательности за этой переменной принципиального значения не имеет). Из ранее доказанного утверждения о некритичных последовательностях следует, что перестановки внутри него с точки зрения испытаний эквивалентны. Это позволяет любую последовательность из группы №4 преобразовать в эквивалентную последовательность группы №3, в которой за некритичной последовательностью сразу следует одно из условий логической функции F(A). Следовательно, группа №4 по аналогии с группой №3, также не требует отдельных проверок, так как автоматически будет проверена при положительных результатах испытаний множества поглощающих некритичных сочетаний входных сигналов (в любой последовательности) и последовательностей группы №1.

Поскольку других типов последовательностей, кроме рассмотренных выше, быть не может, утверждение считается доказанным.

Таким образом, чтобы минимизировать число испытаний логики ИУС необходимо предварительно сформировать две совокупности сочетаний входных сигналов:

совокупность критичных сочетаний входных сигналов, соответствующих условиям логической функции;

совокупность поглощающих некритичных сочетаний входных сигналов.

Формирование совокупности критичных сочетаний входных сигналов осуществляется путем включения всех последовательностей, точно соответствующих каждому условию логической функции F(A).

Формирование совокупности поглощающих некритичных сочетаний включает следующие четыре процедуры.

1. Выбираются только M переменных логической функции Ai (i=1, 2, …, n), входящих в произведения («одиночки» исключаются из рассмотрения);

2. Из анализа условий логической функции выбирается размер поглощающих некритичных сочетаний K.

K=Σ(kj-1),

где k - количество переменных в j-м логическом условии (j=1,J);

J - количество логических условий.

3. Последовательно формируются все сочетания переменных из M по K.

4. С использованием изложенного выше способа определения правильного результата логики работы ИУС для заданной последовательности входных сигналов отбраковываются критичные сочетания, при этом оставшееся множество содержит только поглощающие некритичные сочетания.

Пример 2. Пусть F(A)=Α1+А2А3+А4А5А6;

1. Выбираем 5 переменных, входящих в произведения - А2, А3, А4, А5, A6 (все, кроме A1).

2. Определяем размер поглощающих некритичных сочетаний 1-1+2--1+3-1=3 переменные (из 4-х переменных составить некритичное сочетание уже не удается).

Формируем все сочетания из 5 выбранных переменных по 3 (10 сочетаний) и, исключая 4, содержащих критичные сочетания (А2, А3, А4), (А2, A3, А5), (А2, А3, А6), (А6, А4, А5), получаем 6 поглощающих некритичных сочетаний:

(А2, А4, А5), (А2, А4, А6), (А3, А4, А5), (А3, А4, А6), (А2, А5, А6), (А3, А5, А6).

Используя предлагаемый способ, минимально необходимое число испытаний для логической функции F(A)=Α1+Α2Α3+Α4Α5Α6 составит всего 9 испытаний (три критичные сочетания входных сигналов: (Α1), (А2А3) и (А6, А4, А5) и 6 поглощающих некритичных сочетаний входных сигналов).

Тогда как полное число возможных испытаний составляет 2196.

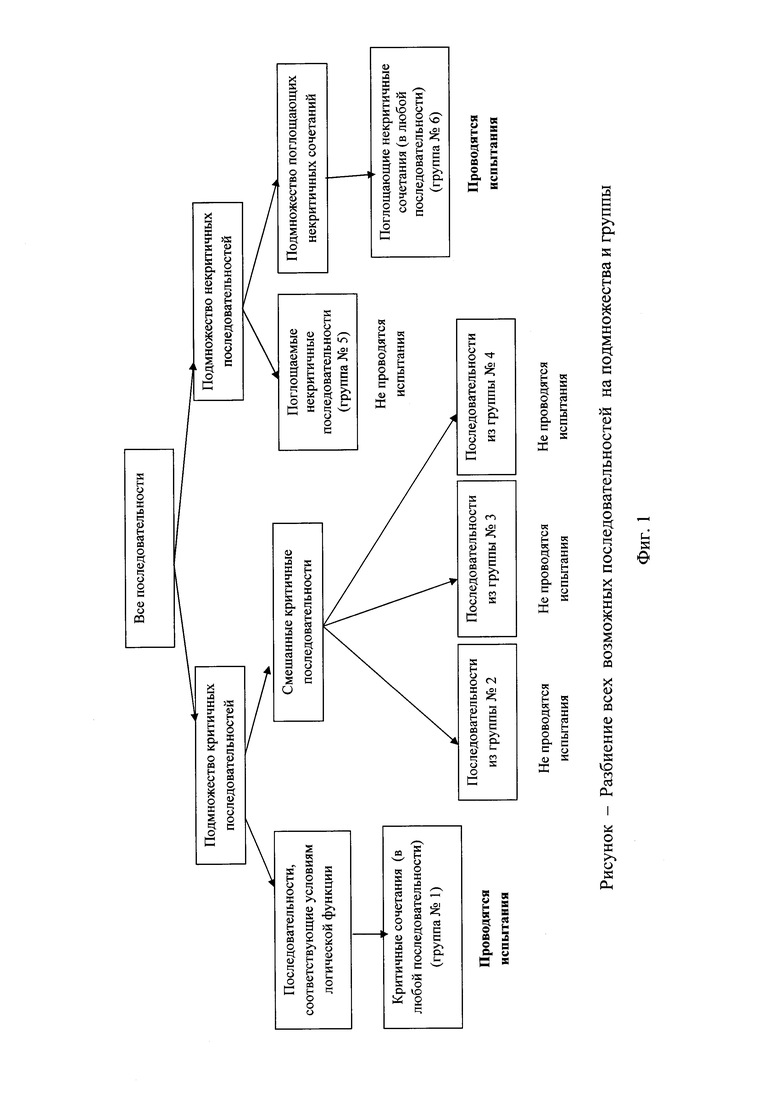

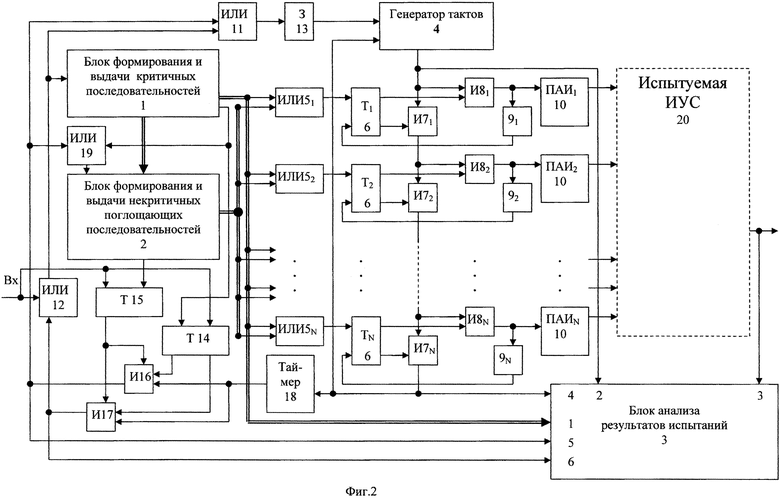

Схема устройства для проверки логики работы ИУС в процессе ее испытаний, реализующее описанный выше способ приведена на Фиг 2.

Устройство содержит: блок формирования и выдачи критичных последовательностей 1, блок формирования и выдачи некритичных поглощающих последовательностей 2, блок анализа результатов испытаний 3, генератор тактов 4, группа элементов ИЛИ 51-5Ν, группа триггеров 61-6N, первая группа элементов И 71-7Ν, вторая группа элементов И 81-8Ν, группа элементов задержки 91-9N, N - программно-аппаратных имитаторов (ПАИ) входных сигналов ИУС 10, первый и второй элементы ИЛИ 11, 12, элемент задержки 13, первый и второй триггеры режима 14, 15, первый и второй элементы И 16, 17, таймер 18, третий элементы ИЛИ 19. На чертеже пунктиром показана ИУС 20 и управляющий вход устройства «Вх». Первые информационные выходы блока формирования и выдачи критичных последовательностей 1 соединены с входами группы соответствующих элементов ИЛИ 51-5N и информационными входами 1 блока анализа результатов испытаний 3, а управляющий выход с входом третьего элемента ИЛИ 19 и с входом установки триггера режима 14 в единичное состояние, вторые информационные выходы блока формирования и выдачи критичных последовательностей 1 соединены с информационными входами блока формирования и выдачи некритичных поглощающих последовательностей 2, управляющий выход блока формирования и выдачи некритичных поглощающих последовательностей 2 соединен с входом установки второго триггера 15 в нулевое состояние, а информационные выходы блока формирования и выдачи некритичных поглощающих последовательностей 2 соединены с вторыми входами группы соответствующих элементов ИЛИ 51-5N, выходы которых соединены с входами установки в единичное состояние группы соответствующих триггеров 61-6N, нулевые выходы которых соединены с первыми входами группы элементов И 71-7N, а единичные выходы соединены с первыми входами группы элементов И 81-8N, выход генератора тактов 4 соединен со вторым входом блока анализа результатов испытаний 3 и со вторыми входами первых элементов И первой и второй групп 7, 8, выход i-го (i=1, 2, …, Ν-1) элемента И первой группы 7 соединен со вторыми входами (i+1)-x элементов И первой и второй групп 7, 8, выходы элементов И второй группы соединены с входами соответствующих ПАИ 101-10N и входами группы соответствующих элементов задержек 91-9Ν, выходы которых соединены с входами установки в нулевое состояние группы соответствующих триггеров 61-6N, выходы ПАИ 101-10 соединены с соответствующими входами испытуемой ИУС, выход которой соединен с третьим входом блока анализа результатов испытаний 3, выход N-го элемента И первой группы соединен с четвертым входом блока анализа результатов испытаний 3, входом таймера 18 и с входом останова генератора тактов 4, выход таймера 18 соединен с первыми входами первого и второго элемента И 16, 17, ко вторым входам которых подключен единичный выход второго триггера режима 15, а к третьим входам единичный и нулевой выходы первого триггера режима 14, выход первого элемента И 16 соединен с пятым входом блока анализа результатов испытаний 3, с первым входом первого элемента ИЛИ 11 и входом третьего элемента ИЛИ 19, выход которого соединен с управляющим входом блока формирования и выдачи некритичных поглощающих последовательностей 2, выход второго элемента И 17 соединен с шестым входом блока анализа результатов испытаний 3 и с первым входом второго элемента ИЛИ 12, второй вход которого является управляющим входом устройства, соединен с входом установки первого триггера в нулевое состояние и с входом установки второго триггера в единичное состояние, а выход соединен с управляющим входом блока формирования и выдачи критичных последовательностей 1 и вторым входом первого элемента ИЛИ 11, выход которого подключен через элемент задержки 13 к входу запуска генератора тактов 4.

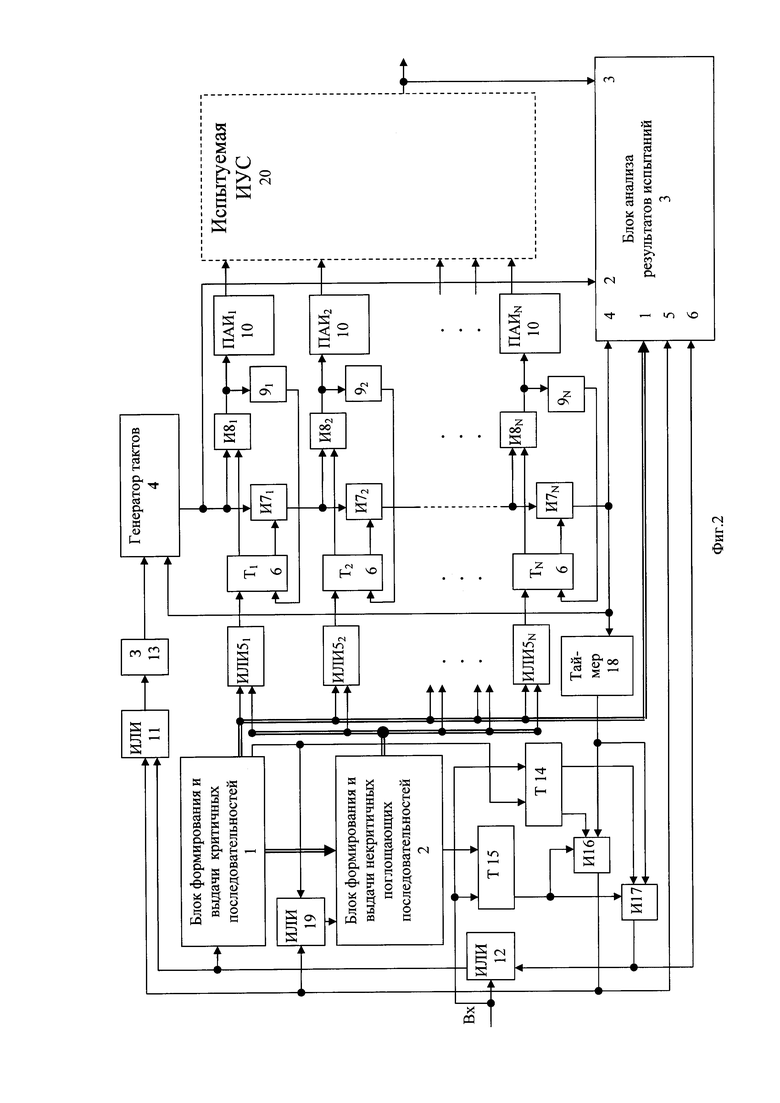

Блок формирования и выдачи критичных последовательностей содержит устройство набора и ввода 21 и блок хранения и выдачи 22, причем выходы устройства набора и ввода 21 соединены с входами блок хранения и выдачи 22 первые и вторые информационные выходы которого являются первыми и вторыми выходами блока формирования и выдачи критичных последовательностей, а управляющие вход и выход являются управляющими входом и выходом блока формирования и выдачи критичных последовательностей.

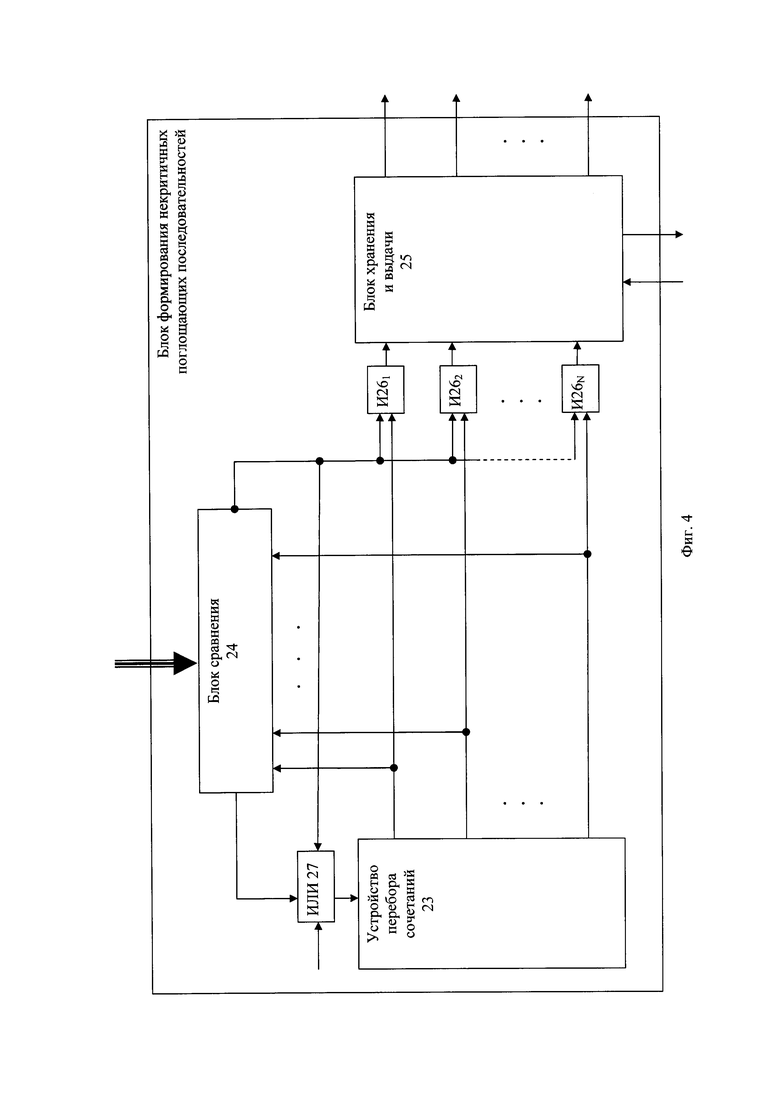

Блок формирования и выдачи поглощающих некритичных последовательностей содержит устройство перебора сочетаний 23, блок сравнения 24, блок хранения и выдачи 25, группу элементов И 26, элемент ИЛИ 27, причем выходы устройства перебора сочетаний 23 соединены с входами группы соответствующих элементов И 26 и с информационными входами блока сравнения 24, вторые информационные входы которого являются входами блока формирования и выдачи 25, первый выход блока сравнения 24 соединен с входом элемента ИЛИ 27, второй выход блока сравнения соединен со вторыми входами группы элементов И 26 и вторым входом элемента ИЛИ 27, третий вход которого является входом запуска формирования сочетаний, выход соединен с управляющим входом устройства перебора сочетаний 23, выходы группы элементов И 26 соединены с информационными входами блока хранения и выдачи 25, информационные выходы которого являются выходами блока формирования и выдачи поглощающих некритичных последовательностей, а управляющие вход и выход являются управляющими входом и выходом, блока формирования и выдачи поглощающих некритичных последовательностей.

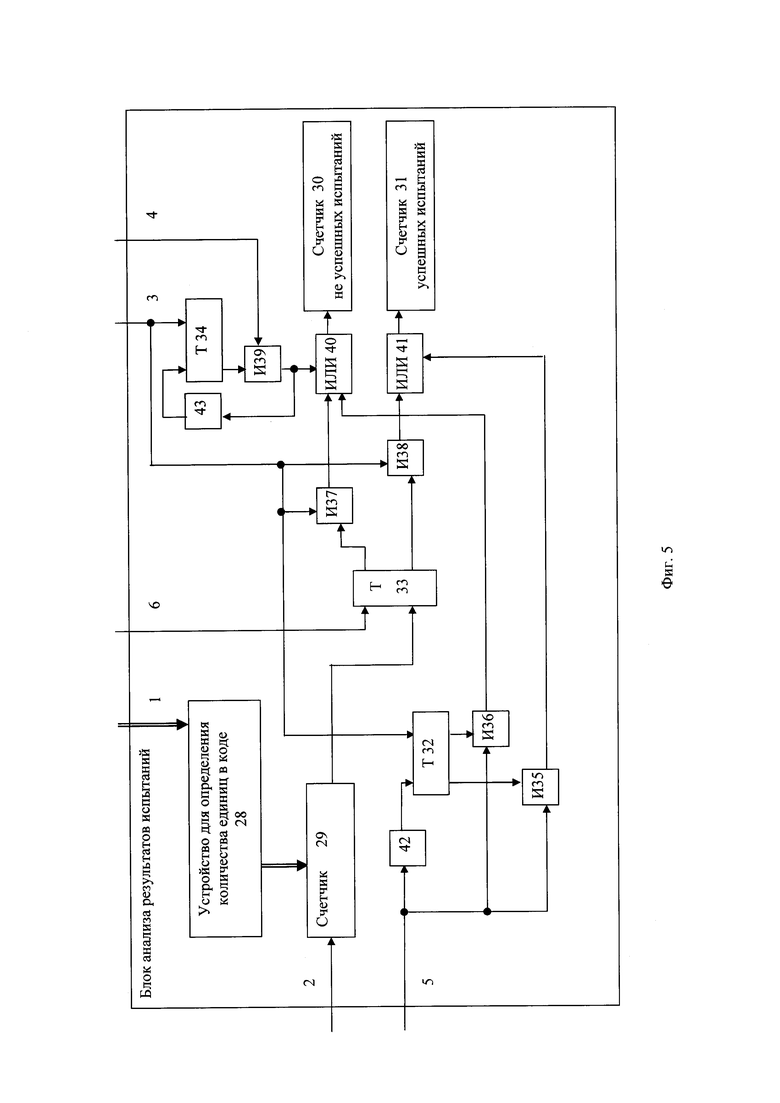

Блок анализа результатов испытаний содержит устройство для определения количества единиц в коде 28, первый счетчик 29, счетчик неуспешных испытаний 30, счетчик успешных испытаний 31, первый, второй и третий триггеры 32, 33, 34, первый, второй, третий, четвертый и пятый элементы И 35-39, первый и второй элементы ИЛИ 40, 41, первый и второй элементы задержки 42, 43, причем первые информационные входы блока анализа результатов испытаний соединен с входами устройства для определения количества единиц в коде 28, выходы которого соединены с входами установки первого счетчика 29 в соответствующее количеству единиц в коде состояние, второй вход блока анализа результатов испытаний соединен с вычитающим входом первого счетчика 29, выход которого соединен с входом установки в единичное состояние второго триггера 33, к с входу установки в нулевое состояние второго подключен четвертый вход блока анализа результатов испытаний, пятый вход блока анализа результатов испытаний соединен с входами первого и второго элементов И 35, 36 и через первый элемент задержки 42 с входом установки в нулевое состояние первого триггера 32, выходы которого соединены с входами первого и второго элементов И 35, 36, выход первого элемента И 35 соединен с входом второго элемента ИЛИ 41, а выход второго элемента И 36 соединен с входом первого элемента ИЛИ 40, выходы второго триггера 33 соединены с входами третьего и четвертого элементов И 37, 38, выход третьего элемента И 37 соединен с входом первого элемента ИЛИ 40, а выход четвертого элемента И 38 соединен с входом второго элемента ИЛИ 41, третий вход блока анализа результатов испытаний соединен с входами установки первого и третьего триггера 32, 34 в единичное состояние и входами третьего и четвертого элементов И 37, 38, шестой вход блока анализа результатов испытаний соединен с входом пятого элемента И 39, ко второму входу которого подключен нулевой выход третьего триггера 34, выход пятого элемента И 39 соединен с входом первого элемента ИЛИ 40 и через второй элемент задержки 43 к входу установки в нулевое состояние третьего триггера 34, выход первого элемента ИЛИ 40 соединен с входом счетчика неуспешных испытаний 30, а выход второго элемента ИЛИ 41 соединен входом счетчика успешных испытаний 31.

Работу устройства рассмотрим на приведенном выше примере №2. Пусть ИУС предназначена для реализации следующей логической функции:

F(A)=A1+А2А3+А4А5А6.

До начала испытаний путем анализа логической функции, испытуемой ИУС, формируются условия логической функции (A1), (А2А3), (А4А5А6) и с помощью устройства набора и ввода 21 (фиг. 3) блока формирования и выдачи критичных последовательностей осуществляется запись всех критичных последовательностей в блок хранения и выдачи 22. Устройство набора и ввода 21, в общем случае, может представлять наборное поле. Блок хранения и выдачи 22 может быть выполнен в виде сдвиговых регистров. В блок хранения и выдачи 22 будут записаны три кода: (100000), (011000) и (000111).

Затем формируем поглощающие некритичные последовательности следующим образом.

Выбираем 5 переменных, входящих в произведения - А2, А3, А4, А5, А6 (все, кроме A1).

Определяем размер поглощающих некритичных сочетаний 1-1+2--1+3-1=3 переменные (из 4-х переменных составить некритичное сочетание уже не удается).

В устройство перебора сочетаний 23 (фиг. 4) вводим состав переменных и количество переменных в сочетаниях и запуская устройство перебора сочетаний формируем первый код 011100, который поступает в блок сравнения. Так как данный код содержит критичную последовательность 011000, то на первом выходе блока сравнения 24 появится сигнал, который поступит через элемент ИЛИ 27 на управляющий вход устройства перебора сочетаний 23 и будет сформировано следующее сочетание 011010, которое также содержит критичную последовательность 011000. Аналогично будут сформированы следующие сочетания 011001 и 010110. Последнее сочетание не содержит критичную последовательность и сигнал появится на втором выходе блока сравнения 24, по которому откроются элементы И 26 и в блок хранения и выдачи 25 поступит код, не содержащий критичную последовательность. Сигнал со второго выхода блока 24 поступит через элемент ИЛИ 27 на управляющий вход устройства перебора сочетаний 23 и будет сформировано следующее сочетание 010101. Аналогично будут сформированы следующие сочетания 010011, 001110, 001101, 001011 и 000111. Последнее сочетание содержит критичную последовательность и, следовательно, в блок хранения и выдачи 25 не запишется. Таким образом, в блоке хранения и выдачи 25 будут записаны коды: 010110, 010101, 010011, 001110, 001101, 001011, которые содержат 6 поглощающих некритичных сочетаний.

После формирования критичных последовательностей и поглощающих некритичных последовательностей проводятся испытания ИУС следующим образом.

На вход 20 устройства (фиг. 2) подается сигнал, который установит триггер 15 в единичное состояние и через элемент ИЛИ 12 поступит вход элемента ИЛИ 11 и на управляющий вход блока формирования и выдачи критичных последовательностей 1. Блок формирования и выдачи критичных последовательностей 1 по сигналу выдает первую критичную последовательность 100000, которая поступит через элементы ИЛИ 5 на входы триггеров бив блок анализа в устройство определения единиц 28 и установит счетчик 29 в состояние один (по количеству единиц в коде). С выхода элемента ИЛИ 11 через элемент задержки 13 запускается генератор тактов 4. Период следования импульсов выбирают равным допустимому времени формирования сигнала ИУС (требования технического задания). С выхода генератора тактов 4 первый импульс поступит через открытый элемент И 81 на вход ПАИ 101, через элемент задержки 91 установит триггер 61 в нулевое состояние и поступит на вычитающий вход счетчика 29 блока анализа 3. Счетчик 29 обнулится и триггер 33 установится в единичное состояние. ПАИ 101 выдаст в ИУС в соответствии с заданными параметрами сигнал Α1. Если на выходе испытуемой ИУС в течение допустимого времени появится управляющий сигнал, который поступит на третий вход блока анализа, то этот сигнал установит триггеры 32, 34 в единицу и через открытый элемент И 38, ИЛИ 41 поступит в счетчик успешных испытаний. Если ИУС не сформирует сигнал до второго такта, то второй тактовый импульс пройдя открытые элементы И 71-7Ν, поступит на вход таймера 18 вход останова генератора тактов 4 и четвертый вход блока анализа и установит триггер 33 в нулевое состояние. Если ИУС сформирует сигнал после второго такта, что не соответствует заданным требованиям по времени формирования сигнала, то сигнал с выхода ИУС установит триггеры 32, 34 в единичное состояние и, пройдя открытый элемент И37, элемент ИЛИ 40 поступит на вход счетчика неуспешных испытаний 30. Если ИУС не сформирует сигнал до окончания действия таймера 18. то сигнал с выхода таймера 18 поступит через открытый элемент И 17 на шестой вход блока анализа и через открытый элемент И 39, ИЛИ 40 поступит на вход счетчика неуспешных испытаний 30, кроме того, сигнал с выхода элемента И 17 поступит через элемент ИЛИ 12 на управляющий вход блока формирования и выдачи критичных последовательностей 1 и элемент ИЛИ 11. Блок формирования и выдачи критичных последовательностей 1 по сигналу выдает вторую критичную последовательность 011000, которая поступит через элементы ИЛИ 5 на входы триггеров 6 и в блок анализа в устройство определения единиц 28 и установит счетчик 29 в состояние два (по количеству единиц в коде). С выхода элемента ИЛИ 11 через элемент задержки 13 запускается генератор тактов 4.

Первый тактовый импульс поступит через открытый элемент И 71 и И 82 на вход ПАИ 102 через элемент задержки 92 установит триггер 62 в нулевое состояние и поступит на вычитающий вход счетчика 29 блока анализа 3. ПАИ 102 выдаст в ИУС в соответствии с заданными параметрами сигнал А2. Значение счетчика 29 уменьшится на единицу.

Если ИУС сформирует сигнал после первого такта, что не соответствует логическому условию формирования сигнала, то сигнал с выхода ИУС установит триггеры 32, 34 в единичное состояние и, пройдя открытый элемент И37, элемент ИЛИ 40 поступит на вход счетчика неуспешных испытаний 30. Если ИУС не сформирует сигнал после первого такта, то второй тактовый импульс поступит через открытый элемент И 71 И 72 и И 83 на вход ПАИ 103 через элемент задержки 93 установит триггер 63 в нулевое состояние и поступит на вычитающий вход счетчика 29 блока анализа 3. ПАИ 103 выдаст в ИУС в соответствии с заданными параметрами сигнал А3. Счетчик 29 обнулится и триггер 33 установится в единичное состояние.

Если на выходе испытуемой ИУС в течении допустимого времени появится управляющий сигнал, который поступит на третий вход блока анализа, то этот сигнал установит триггеры 32, 34 в единицу и через открытый элемент И 38, ИЛИ 41 поступит в счетчик успешных испытаний. Если ИУС не сформирует сигнал до третьего такта, то третий тактовый импульс, пройдя открытые элементы И 71-7N, поступит на вход таймера 18 вход останова генератора тактов 4 и четвертый вход блока анализа, и установит триггер 33 в нулевое состояние. Если ИУС сформирует сигнал после третьего такта, что не соответствует заданным требованиям по времени формирования сигнала, то сигнал с выхода ИУС установит триггеры 32, 34 в единичное состояние и, пройдя открытый элемент И37, элемент ИЛИ 40 поступит на вход счетчика неуспешных испытаний 30. Если ИУС не сформирует сигнал до окончания действия таймера 18, то сигнал с выхода таймера 18 поступит через открытый элемент И 17 на шестой вход блока анализа и через открытый элемент И 39, ИЛИ 40 поступит на вход счетчика неуспешных испытаний 30, кроме того, сигнал с выхода элемента И 17 поступит через элемент ИЛИ 12 на управляющий вход блока формирования и выдачи критичных последовательностей 1 и элемент ИЛИ 11. Блок формирования и выдачи критичных последовательностей 1 по сигналу выдает третью критичную последовательность 000111, которая поступит через элементы ИЛИ 5 на входы триггеров 6 и в блок анализа в устройство определения единиц 28, и установит счетчик 29 в состояние три (по количеству единиц в коде). С выхода элемента ИЛИ 11 через элемент задержки 13 запускается генератор тактов 4. Работа устройства будет продолжена описанным выше способом. После поступления с выхода элемента ИЛИ 12 на управляющий вход блока формирования и выдачи критичных последовательностей 1 сигнала выдачи очередной критической последовательности данный сигнал поступит на управляющий выход блока формирования и выдачи критичных последовательностей 1, т.к. все записанные последовательности выданы. Этот сигнал поступит через элемент ИЛИ 19 на вход блока формирования и выдачи некритичных поглощающих последовательностей 2 и установит триггер 14 в единичное состояние. Блок формирования и выдачи некритичных поглощающих последовательностей 2 выдает первую некритичную поглощающую последовательность 010110, которая запишется через элементы ИЛИ 5 в триггеры 6. Сигнал с выхода задержки 13 запустит генератор тактов. Описанным выше способом ПАИ 10 поочередно выдают в ИУС сигналы А2, А4, А5, которые не содержат критичных сочетаний и испытуемая ИУС не должна вырабатывать управляющий сигнал. Если испытуемая ИУС выработает управляющий сигнал, в блоке анализа триггер 32 установится в единичное состояние. Сигнал с выхода таймера 18 через элемент И 17 поступит на пятый вход блока анализа и через элементы И 36, ИЛИ 40 на вход счетчика неуспешных испытаний. В случае отсутствия сформированного ИУС управляющего сигнала триггер будет в нулевом состоянии и сигнал с выхода таймера 18 через элемент И 17 поступит на пятый вход блока анализа и через элементы И 35, ИЛИ 41 на вход счетчика успешных испытаний. Далее работа устройства будет продолжена аналогичным образом. После обработки последней некритичной поглощающей последовательности на управляющем выходе блока формирования и выдачи некритичных поглощающих последовательностей 2 появится сигнал устанавливающий триггер 15 в нулевое состояние и сигнализирующий об окончании процесса испытаний.

Таким образом, предложенный способ формирования специального множества представительных последовательностей входных сигналов для испытаний ИУС позволяет значительно сократить объем испытаний ИУС и гарантирует проверку ИУС так же, как и полная совокупность последовательностей входных сигналов.

Предложенное устройство для проверки логики работы информационно-управляющих систем позволяет автоматизировать процесс испытаний ИУС.

Учитывая необходимость испытаний ИУС после каждой доработки, после каждой смены версии программного обеспечения, изменения входных условий и сигналов, способ и предложенное устройство для проверки логики работы информационно-управляющих систем имеют весьма значительную ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программ | 1988 |

|

SU1617442A1 |

| УСТРОЙСТВО ДЛЯ ДИСТАНЦИОННОГО ПРОГРАММНОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ И СИГНАЛИЗАЦИЕЙ | 1993 |

|

RU2092886C1 |

| Устройство для дистанционного программного управления сигнализацией и электроприводными механизмами | 1989 |

|

SU1652964A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Генератор случайных чисел | 1981 |

|

SU991422A1 |

| Устройство для управления памятью | 1984 |

|

SU1236489A1 |

| Устройство для ввода-вывода дискретных сигналов микроЭВМ | 1989 |

|

SU1681306A1 |

| Устройство для вывода произвольно изменяющейся функции | 1980 |

|

SU955024A1 |

| Устройство для сопряжения микроЭВМ с каналами связи | 1989 |

|

SU1786490A1 |

| Логическое устройство | 1977 |

|

SU729588A1 |

Изобретение относится к способам испытаний информационно-управляющих систем (ИУС), которые должны формировать необходимые управляющие команды в зависимости от условий обстановки, которые определяются поступающими на вход ИУС информационными сигналами, путем формирования и использования необходимых и достаточных испытательных тестов, сформированных по результатам математического планирования эксперимента. Технический результат заключается в обеспечении автоматизации процесса испытаний ИУС. Технический результат достигается за счет проверки логики работы информационно-управляющих систем, которая включает формирование совокупности необходимых и достаточных испытательных тестов, а также контроль допустимых отклонений времени формирования выходного сигнала для проверки соответствия ИУС заданным требованиям, и формирования минимального числа последовательностей входных сигналов для испытаний ИУС, проверка на которых гарантирует правильную работу ИУС, как и полная совокупность последовательностей входных сигналов для испытаний ИУС. 2 н. и 3 з.п. ф-лы, 5 ил.

1. Способ для проверки логики работы информационно-управляющих систем, основанный на формирования диагностических тестов путем комбинаций входных тестовых сигналов с сочетаниями параметров сигналов и последовательностями подачи входных сигналов, отличающийся тем, что формируется совокупность критичных сочетаний входных сигналов, которая включает все критичные сочетания входных сигналов, соответствующие условиям логической функции, которые должна реализовать испытуемая ИУС, и формируется совокупность поглощающих некритичных сочетаний входных сигналов путем формирования сочетаний из M по K (М - количество переменных логической функции Ai (i=1, 2, …, Ν), входящих в произведения, K - размер поглощающих некритичных сочетаний, K определяется из соотношения: K=Σ(kj-1), где k - количество переменных в j-м логическом условии (j=1,J), J - количество логических условий), и исключения сочетаний, содержащих критичные сочетания входных сигналов, сформированная совокупность критичных сочетаний входных сигналов последовательно подается на вход испытуемой ИУС и контролируется формирование и своевременность формирования управляющих команд при поступлении последнего входного сигнала в последовательности критичного сочетания входных сигналов, затем последовательно подается на вход испытуемой ИУС сформированная совокупность поглощающих некритичных сочетаний входных сигналов и контролируется отсутствие сформированных команд или необоснованное формирование управляющих команд.

2. Устройство для проверки логики работы ИУС в процессе ее испытаний, реализующее способ по п. 1, содержащее N программно-аппаратных имитаторов входных сигналов (N - количество входных сигналов), причем выходы программно-аппаратных имитаторов соединены с соответствующими входами испытуемой ИУС, отличающееся тем, что в устройство введены блок формирования и выдачи критичных последовательностей, блок формирования и выдачи некритичных поглощающих последовательностей, блок анализа результатов испытаний, генератор тактов, группа элементов ИЛИ, группа триггеров, первая группа элементов, вторая группа элементов И, группа элементов задержки, первый, второй и третий элементы ИЛИ, элемент задержки, первый и второй триггеры режима, первый и второй элементы И, таймер, причем первые информационные выходы блока формирования и выдачи критичных последовательностей соединены с входами группы соответствующих элементов ИЛИ и информационными входами блока анализа результатов испытаний, а управляющий выход с входом третьего элемента ИЛИ, с входом установки первого триггера режима в единичное состояние и с входом третьего элемента ИЛИ, выход которого соединен с управляющим входом блока формирования и выдачи некритичных поглощающих последовательностей, вторые информационные выходы блока формирования и выдачи критичных последовательностей соединены с информационными входами блока формирования и выдачи некритичных поглощающих последовательностей, управляющий выход блока формирования и выдачи некритичных поглощающих последовательностей соединен с входом установки второго триггера режима в единичное состояние, а информационные выходы блока формирования и выдачи некритичных поглощающих последовательностей соединены со вторыми входами группы соответствующих элементов ИЛИ, выходы которых соединены с входами установки в единичное состояние группы соответствующих триггеров, нулевые выходы которых соединены с первыми входами первой группы элементов И, а единичные выходы соединены с первыми входами второй группы элементов И, выход генератора тактов соединен со вторым входом блока анализа результатов испытаний и со вторыми входами первых элементов И первой и второй групп, выход i-го (i=1, 2, …, Ν -1) элемента И первой группы соединен со вторыми входами (i+1)-x элементов И первой и второй групп, выходы элементов И второй группы соединены с входами соответствующих ПАИ входных сигналов и входами группы соответствующих элементов задержек, выходы которых соединены с входами установки в нулевое состояние группы соответствующих триггеров, выход испытуемой ИУС соединен с третьим входом блока анализа результатов испытаний, выход N-го элемента И первой группы соединен с четвертым входом блока анализа результатов испытаний, входом таймера и с входом останова генератора тактов, выход таймера соединен с первыми входами первого и второго элемента И, ко вторым входам которых подключен нулевой выход второго триггера режима, а к третьим входам единичный и нулевой выходы первого триггера режима, выход первого элемента И соединен с пятым входом блока анализа результатов испытаний, с входом третьего элемента ИЛИ и первым входом первого элемента ИЛИ, выход второго элемента И соединен с шестым входом блока анализа результатов испытаний и с первым входом второго элемента ИЛИ, второй вход которого является управляющим входом устройства и соединен с входом установки первого и второго триггера в нулевое состояние, а выход соединен с управляющим входом блока формирования и выдачи критичных последовательностей и вторым входом первого элемента ИЛИ, выход которого подключен через элемент задержки к входу запуска генератора тактов.

3. Устройство по п. 2, отличающееся тем, что блок формирования и выдачи критичных последовательностей содержит устройство набора и ввода и блок хранения и выдачи, причем выходы устройства набора и ввода соединены с входами блока хранения и выдачи, первые и вторые информационные выходы которого являются первыми и вторыми выходами блока формирования и выдачи критичных последовательностей, а управляющие вход и выход являются управляющими входом и выходом блока формирования и выдачи критичных последовательностей.

4. Устройство по п. 2, отличающееся тем, что блок формирования и выдачи поглощающих некритичных последовательностей содержит устройство перебора сочетаний, блок сравнения, блок хранения и выдачи, группу элементов И, элемент ИЛИ, причем выходы устройства перебора сочетаний соединены с входами группы соответствующих элементов И и с информационными входами блока сравнения, вторые информационные входы, которого являются входами блока формирования и выдачи поглощающих некритичных последовательностей, первый выход блока сравнения соединен с входом элемента ИЛИ, второй выход блока сравнения соединен со вторыми входами группы элементов И и вторым входом элемента ИЛИ, третий вход которого является входом запуска формирования сочетаний, выход соединен с управляющим входом устройства перебора сочетаний, выходы группы элементов И соединены с информационными входами блока хранения и выдачи, информационные выходы которого являются выходами блока формирования и выдачи поглощающих некритичных последовательностей, а управляющие вход и выход являются управляющими входом и выходом блока формирования и выдачи поглощающих некритичных последовательностей.

5. Устройство по п. 2, отличающееся тем, что блок анализа результатов испытаний содержит устройство для определения количества единиц в коде, первый счетчик, счетчик неуспешных испытаний, счетчик успешных испытаний, первый, второй и третий триггеры, первый, второй, третий, четвертый и пятый элементы И, первый и второй элементы ИЛИ, первый и второй элементы задержки, причем первые информационные входы блока анализа результатов испытаний соединен с входами устройства для определения количества единиц в коде, выходы которого соединены с входами установки первого счетчика в соответствующее количеству единиц в коде состояние, второй вход блока анализа результатов испытаний соединен с вычитающим входом первого счетчика, выход которого соединен с входом установки в единичное состояние второго триггера, к входу установки в нулевое состояние второго подключен четвертый вход блока анализа результатов испытаний, пятый вход блока анализа результатов испытаний соединен с входами первого и второго элементов И и через первый элемент задержки с входом установки в нулевое состояние первого триггера, выходы которого соединены с входами первого и второго элементов И, выход первого элемента И соединен с входом второго элемента ИЛИ, а выход второго элемента И соединен с входом первого элемента ИЛИ, выходы второго триггера соединены с входами третьего и четвертого элементов И, выход третьего элемента И соединен с входом первого элемента ИЛИ, а выход четвертого элемента И соединен с входом второго элемента ИЛИ, третий вход блока анализа результатов испытаний соединен с входами установки первого и третьего триггера в единичное состояние и входами третьего и четвертого элементов И, шестой вход блока анализа результатов испытаний соединен с входом пятого элемента И, ко второму входу которого подключен нулевой выход третьего триггера, выход пятого элемента И соединен с входом первого элемента ИЛИ и через второй элемент задержки с входом установки в нулевое состояние третьего триггера, выход первого элемента ИЛИ соединен с входом счетчика неуспешных испытаний, а выход второго элемента ИЛИ соединен с входом счетчика успешных испытаний.

| СПОСОБ ФОРМИРОВАНИЯ ИСПЫТАТЕЛЬНЫХ ТЕСТОВ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2011 |

|

RU2469372C1 |

| ДАТЧИК ТЕХНОЛОГИЧЕСКОГО ПАРАМЕТРА С ВОЗМОЖНОСТЬЮ ДИАГНОСТИКИ | 2006 |

|

RU2386992C2 |

| МОДЕЛИРУЮЩИЙ КОМПЛЕКС ДЛЯ ПРОВЕРКИ СИСТЕМЫ УПРАВЛЕНИЯ БЕСПИЛОТНОГО ЛЕТАТЕЛЬНОГО АППАРАТА | 2010 |

|

RU2432592C1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

Авторы

Даты

2016-08-27—Публикация

2015-03-24—Подача