1236489

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе процессора ЭВМ

Цель изобретения - расширение функциональных возможностей за счет обеспечения динамического режима работы управляемого блока памяти.

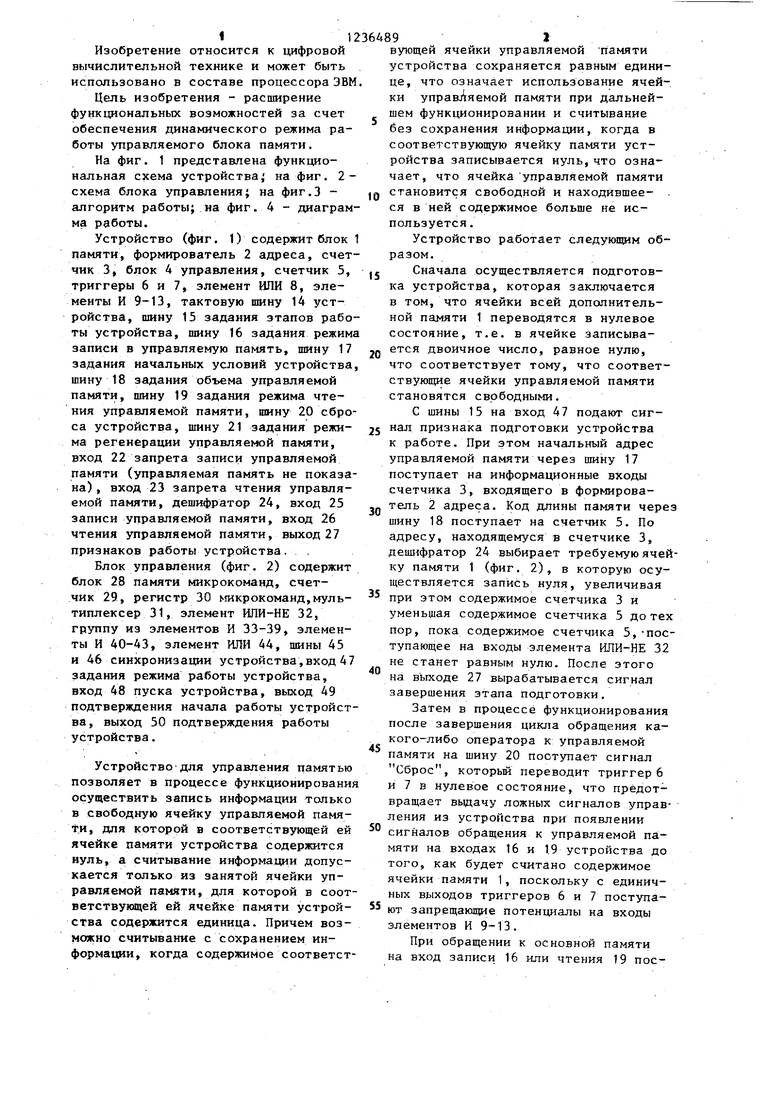

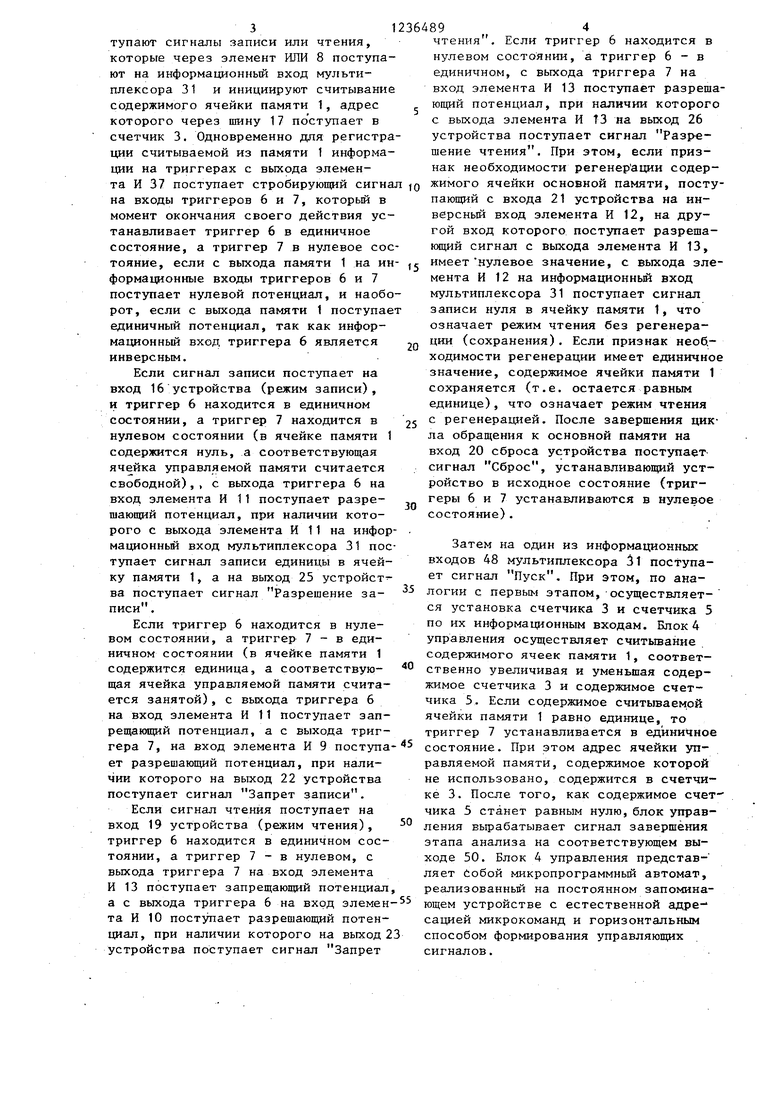

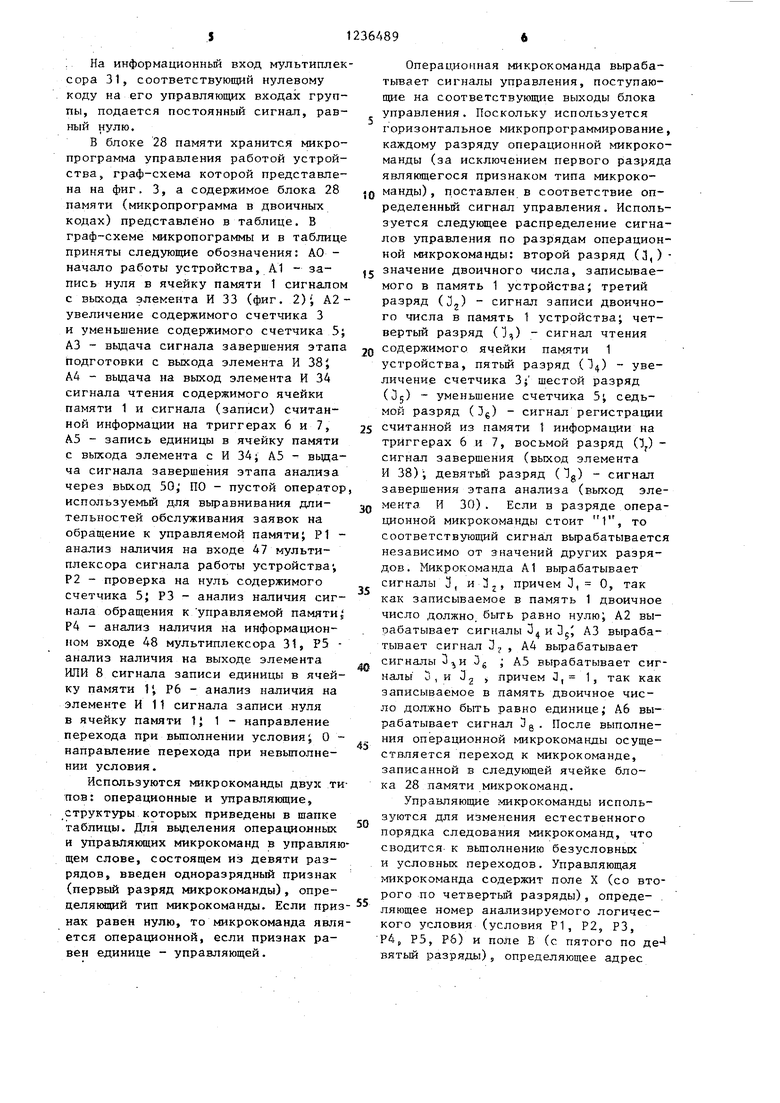

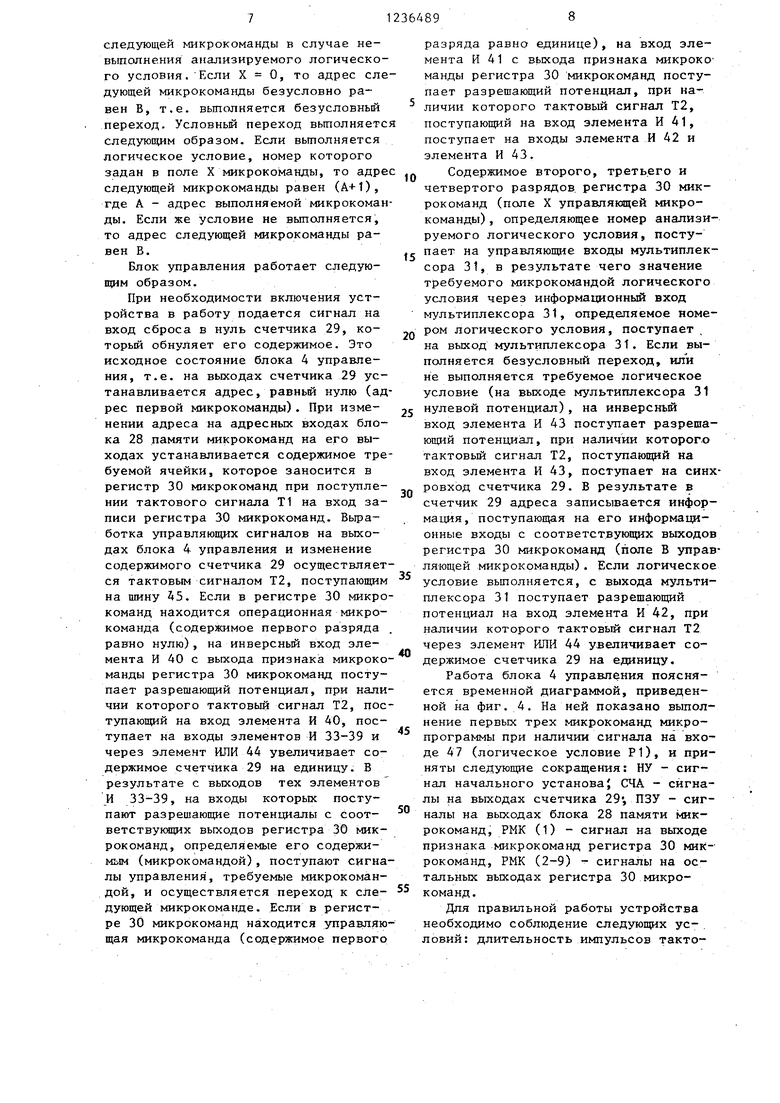

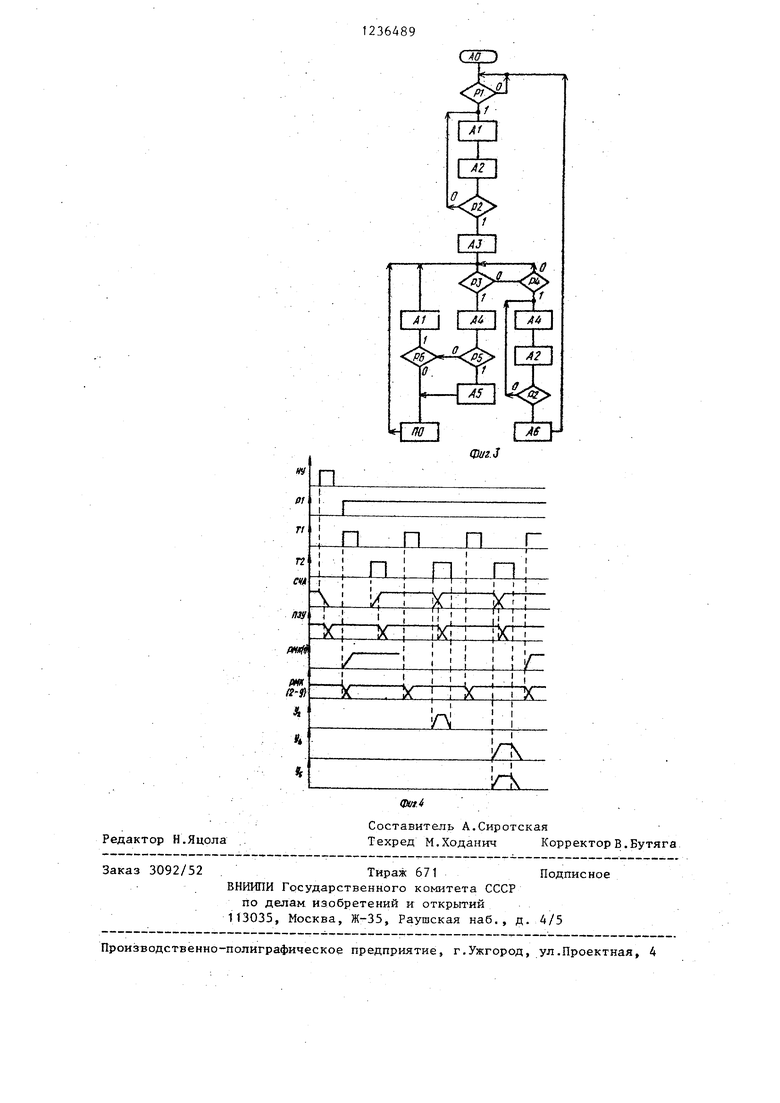

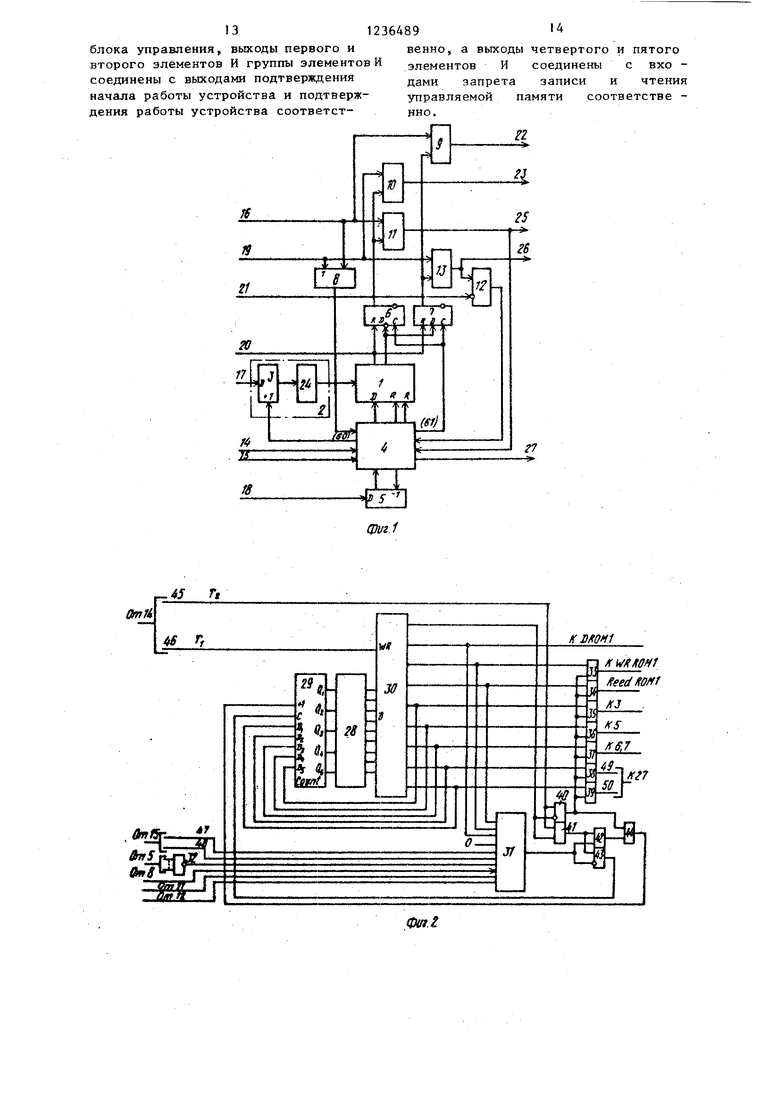

На фиг. 1 представлена функциональная схема устройства; на фиг. 2- схема блока управления; на фиг.З - алгоритм работы; на фиг. 4 - диаграмма работы.

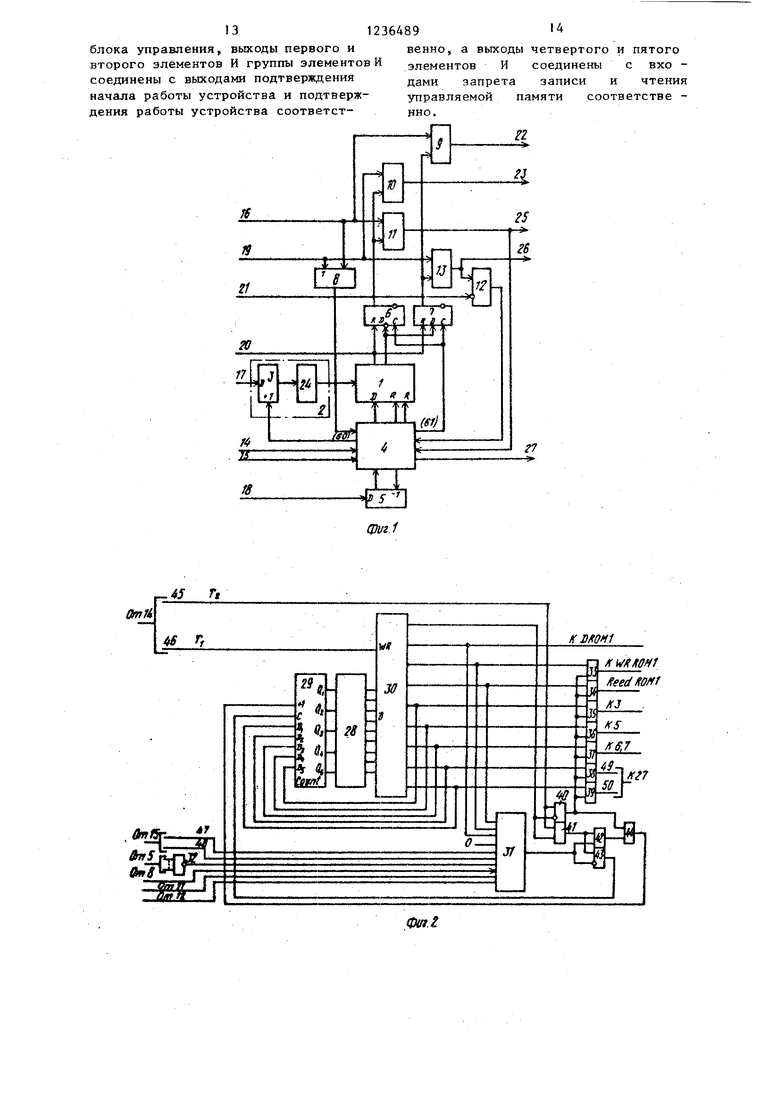

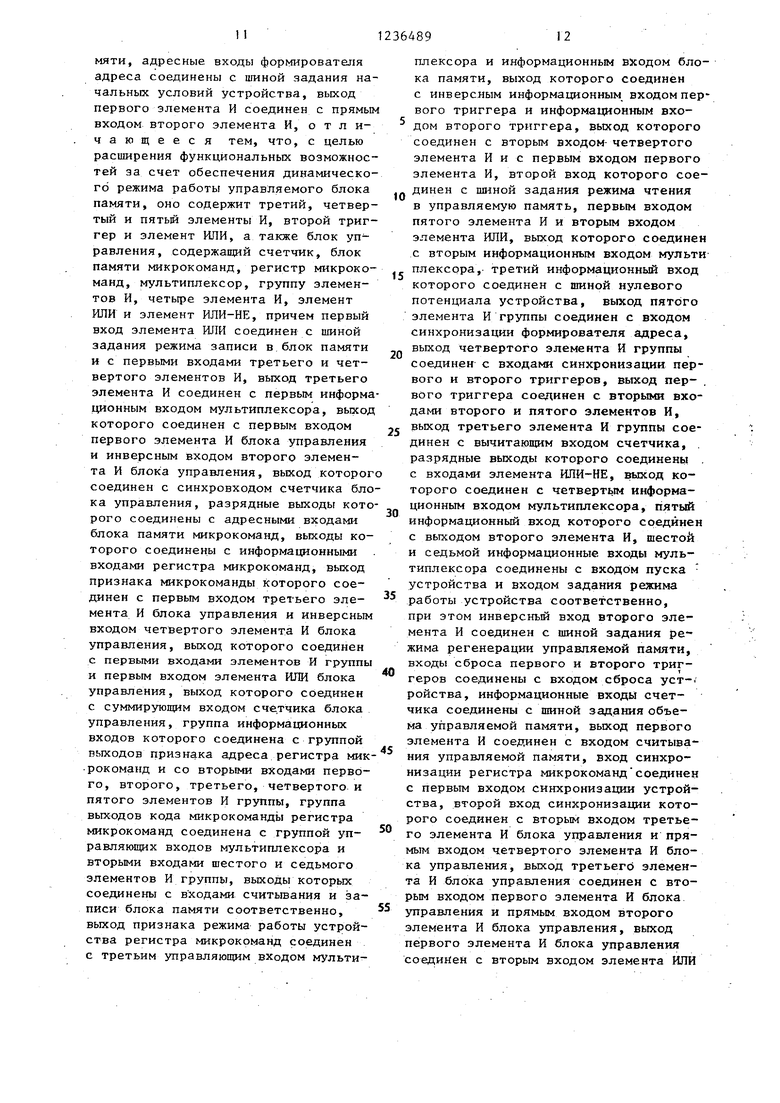

Устройство (фиг. 1) содержит блок памяти, формирователь 2 адреса, счетчик 3, блок 4 управления, счетчик 5, триггеры 6 и 7, элемент ИЛИ 8, элементы И 9-13, тактовую шину 14 устройства, шину 15 задания этапов работы устройства, шину 16 задания режима записи в управляемую память, шину 17 задания начальных условий устройства шину 18 задания объема управляемой памяти, шину 19 задания режима чтения управляемой памяти, шину 20 сброса устройства, шину 21 задания режи- ма регенерации управляе1«)й памяти, вход 22 запрета записи управляемой памяти (управляемая память не показана) , вход 23 запрета чтения управляемой памяти, дешифратор 24, вход 25 записи управляемой памяти, вход 26 чтения управляемой памяти, выход 27 признаков работы устройства.

Блок управления (фиг. 2) содержит блок 28 памяти микрокоманд, счетчик 29, регистр 30 микрокоманд,муль- типлексер 31, элемент ИЛИ-НЕ 32, группу из элементов И 33-39, элементы И 40-43, элемент ИЛИ 44, шины 45 и 46 синхронизации устройства,вход 47 задания режима работы устройства, вход 48 пуска устройства, выход 49 подтверждения начала работы устройства , выход 50 подтверждения работы

устройства.

Устройство для управления цамятью позволяет в процессе функционировани осуществить запись информации только в свободную ячейку управляемой памяти, для которой в соответствующей ей ячейке памяти устройства содержится нуль, а считывание информации допускается только из занятой ячейки управляемой памяти, для которой в соответствующей ей ячейке памяти устрой- ства содержится единица. Причем возможно считывание с сохранением информации, когда содержимое соответст

0

5

5

5

0

5

0

вующей ячейки управляемой памяти устройства сохраняется равным единице, что означает использование ячейки управляемой памяти при дальнейшем функционировании и считывание без сохранения информации, когда в соответствующую ячейку памяти устройства записывается нуль, что означает, что ячейка управляемой памяти становится свободной и находившееся в ней содержимое больше не используется .

Устройство работает следующим образом.

Сначала осуществляется подготовка устройства, которая заключается в том, что ячейки всей дополнительной 1 переводятся в нулевое состояние, т.е. в ячейке записывается двоичное число, равное нулю, что соответствует тому, что соответствующие ячейки управляемой памяти становятся свободными.

С шины 15 на вход 47 подают сигнал признака подготовки устройства к работе. При этом начальный адрес управ.аяемой памяти через шину 17 поступает на информационные входы счетчика 3, входящего в формирователь 2 адреса. Код дпины памяти через шину 18 поступает на счетчик 5. По адресу, находящемуся в счетчике 3, дешифратор 24 выбирает требуемую ячейку памяти 1 (фиг. 2), в которую осуществляется запись нуля, увеличивая при этом содержимое счетчика 3 и уменьшая содержимое счетчика 5 до тех пор, пока содержимое счетчика 5,-поступающее на входы элемента ИЛИ-НЕ 32 не станет равным нулю. После этого на в ыходе 27 вырабатывается сигнал завершения этапа подготовки.

Затем в процессе функционирования после завершения цикла обращения какого-либо оператора к управляемой памяти на шину 20 поступает сигнал Сброс, которьй переводит триггер 6 и 7 в нулевое состояние, что предотвращает вьщачу ложных сигналов управления из устройства при появлении сигналов обращения к управляемой памяти на входах 16 и 1.9 устройства до того, как будет считано содержимое ячейки памяти I, поскольку с единичных выходов триггеров 6 и 7 поступают запрещающие потенциалы на входы элементов И 9-13.

При обращении к основной памяти на вход записи 16 или чтения 19 поступают сигналы записи или чтения, которые через элемент ИЛИ 8 поступают на информационный вход мультиплексора 31 и инициируют считывание содержимого ячейки памяти 1, адрес которого через шину 17 поступает в счетчик 3. Одновременно для регистрации считываемой из памяти 1 информации на триггерах с выхода элемента И 37 поступает стробирующий сигнал ю жимого ячейки основной памяти, посту

на входы триггеров 6 и 7, который в момент окончания своего действия устанавливает триггер 6 в единичное состояние, а триггер 7 в нулевое состояние, если с выхода памяти 1 на информационные входы триггеров 6 и 7 поступает нулевой потенциал, и наоборот, если с выхода памяти 1 поступае единичный потенциал, так как информационный вход триггера 6 является инверсным.

Если сигнал записи поступает на вход 16 устройства (режим записи), и триггер 6 находится в единичном состоянии, а триггер 7 находится в нулевом состоянии (в ячейке памяти 1 содержится нуль, а соответствующая ячейка управляемой памяти считается свободной),, с выхода триггера 6 на вход элемента И 11 поступает разре- шаю1ций потенциал, при наличии которого с выхода элемента И 11 на инфор мационньм вход мультиплексора 31 поступает сигнал записи единицы в ячейку памяти 1, а на выход 25 устройства поступает сигнал Разрешение записи .

Если триггер 6 находится в нулевом состоянии, а триггер 7 - в единичном состоянии (в ячейке памяти 1 содержится единица, а соответствующая ячейка управляемой памяти считается занятой), с выхода триггера 6 на вход элемента И 11 поступает запрещающий потенциал, а с выхода триггера 7, на вход элемента И 9 поступа ет разрешающий потенциал, при наличии которого на выход 22 устройства поступает сигнал Запрет записи.

Если сигнал чтения поступает на вход 19 устройства (режим чтения), триггер 6 находится в единичном состоянии, а триггер 7 - в нулевом, с выхода триггера 7 на вход элемента И 13 поступает запрещающий потенциал, а с выхода триггера 6 на вход элемента И 10 поступает разрешающий потенциал, при наличии которого на выход 2 устройства поступает сигнал Запрет

12364894

чтения. Если триггер 6 находится в

нулевом состоянии, а триггер 6 - в единичном, с выхода триггера 7 на вход элемента И 13 поступает разрешающий потенциал, при наличии которого с выхода элемента И ТЗ на выход 26 устройства поступает сигнал Разрешение чтения. При этом, если признак необходимости регенер ации содер5

)5

20

25

30

35

40

45

50

пающий с входа 21 устройства на инверсный вход элемента И 12, на другой вход которого поступает разреша- кнций сигнал с выхода элемента И 13, имеет нулевое значение, с выхода элемента И 12 на информационньй вход мультиплексора 31 поступает сигнал записи нуля в ячейку памяти 1, что означает режим чтения без регенерации (сохранения). Если признак необходимости регенерации имеет единичное значение, содержимое ячейки памяти 1 сохраняется (т.е. остается равным единице), что означает режим чтения с регенерацией. После завершения цикла обращения к основной памяти на вход 20 сброса устройства поступает сигнал Сброс, устанавливающий устройство в исходное состояние (триггеры 6 и 7 устанавливаются в нулевое состояние).

Затем на один из информационных входов 48 мультиплексора 31 поступает сигнал Пуск, При этом, по аналогии с первым этапом,осуществляется установка счетчика 3 и счетчика 5 по их информационным входам. Блок 4 управления осуществляет считьгоание содержимого ячеек памяти 1, соответственно увеличивая и уменьшая содержимое счетчика 3 и содержимое счетчика 5. Если содержимое считываемой ячейки памяти 1 равно единице, то триггер 7 устанавливается в единичное состояние. При этом адрес ячейки зш- равляемой памяти, содержимое которой не использовано, содержится в счетчике 3. После того, как содержимое счет- чика 5 станет равным нулю, блок управления вырабатывает сигнал завершения этапа анализа на соответствующем выходе 50. Блок 4 управления представ- ляет Собой микропрограммный автомат, реализованньй на постоянном запоминающем устройстве с естественной адре- сацией микрокоманд и горизонтальным способом формирования управляющих сигналов.

; На информационный вход гультиплек сора 31, соответствующий нулевому коду на его управляющих входах группы, подается постоянный сигнал, равный нулю.

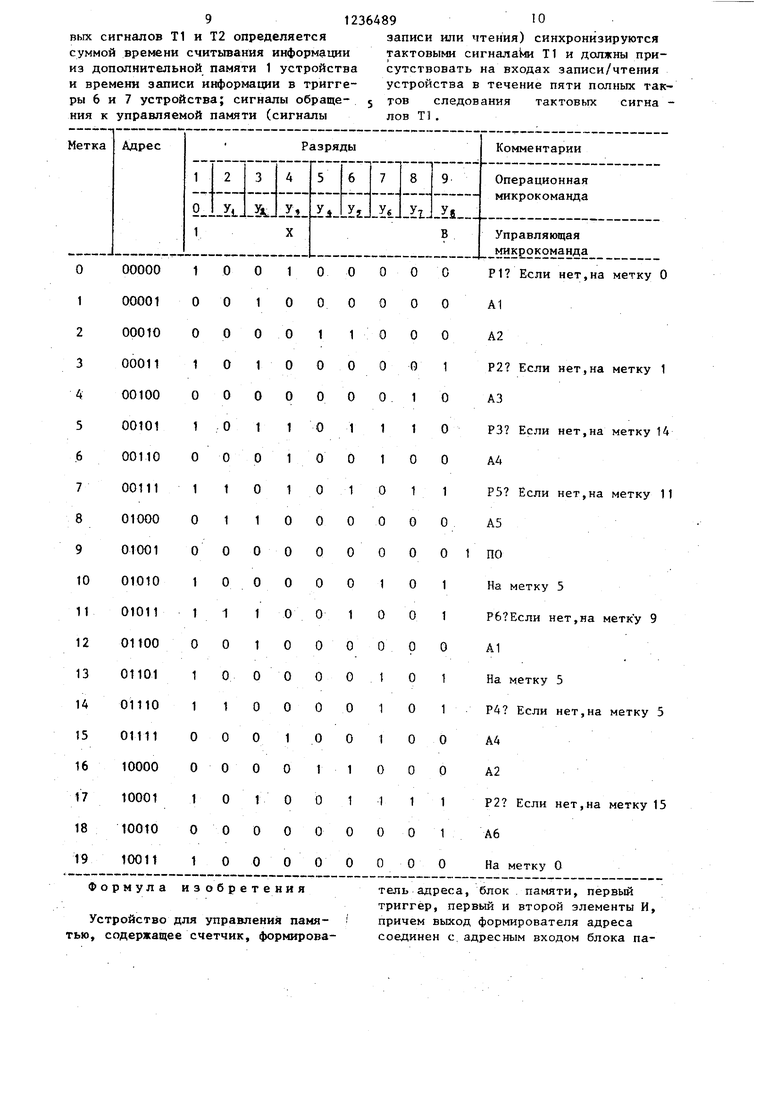

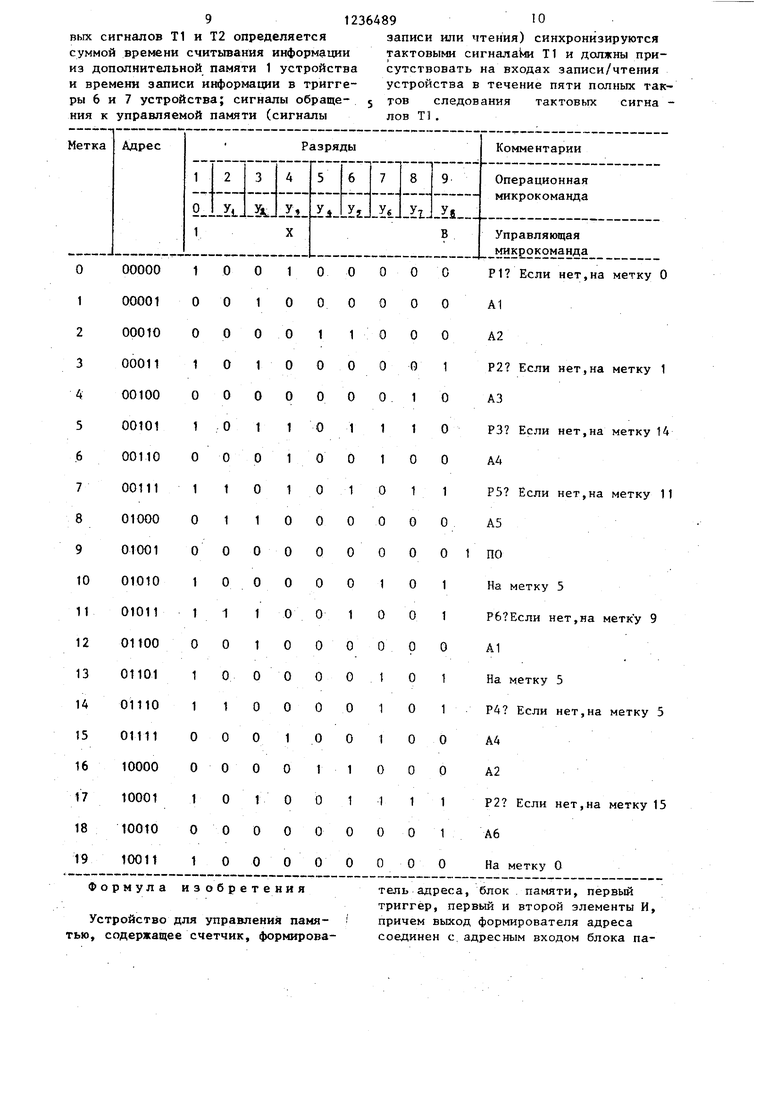

в блоке 28 памяти хранится микропрограмма управления работой устройства, граф-схема которой представлена на фиг. 3, а содержимое блока 28 памяти (микропрограмма в двоичных кодах) представлено в таблице. В граф-схеме микропограммы и в таб,пице приняты следующие обозначения: АО - начало работы устройства, А1 - запись нуля в ячейку памяти 1 сигналом с выхода элемента И 33 (фиг. 2), А2- увеличение содержимого счетчика 3 и уменьшение содержимого счетчика 5; A3 - выдача сигнала завершения этапа подготовки с выхода элемента И 38 А4 - выдача на выход элемента И 34 сигнала чтения содержимого ячейки памяти 1 и сигнала (записи) считанной информации на триггерах 6 и 7, А5 - запись единицы в ячейку памяти с выхода элемента с И 34; А5 - вьзда- ча сигнала завершения этапа анализа через выход 50 ПО - пустой оператор используемый для выравнивания длительностей обслуживания заявок на обращение к управляемой памяти; Р1 - анализ наличия на входе 47 мультиплексора сигнала работы устройства-, Р2 - проверка на нуль содержимого счетчика 5; РЗ - анализ наличия сигнала обращения к управляемой памяти Р4 - анализ наличия на информационном входе 48 мультиплексора 31s Р5 - анализ наличия на выходе элемента ИЛИ 8 сигнала записи единицы в ячейку памяти 1i Р6 - анализ наличия на элементе И 11 сигнала записи нуля в ячейку памяти 1J 1 - направление перехода при выпсетнении условия; О - направление перехода при невыполнении условия.

Используются микрокоманды двух типов: операционные и управляющие, структуры которых приведены в шапке таблицы. Для выделения операционных и управляющих микрокоманд в управляющем слове, состоящем из девяти разрядов, введен одноразрядный признак (первый разряд микрокоманды), опре- деляняций тип микрокоманды. Если признак равен нулю, то микрокоманда является операционной, если признак равен единице - управляющей.

0

Операционная микрокоманда вырабатывает сигналы управления, поступающие на соответствующие выходы блока управления. Поскольку используется горизонтальное микропрограммирование, каждому разряду операционной микрокоманды (за исключением первого разряда являющегося признаком типа микроко0 манды), поставлен в соответствие оп- ределенньш сигнал управления. Используется следующее распределение сигналов управления по разрядам операционной микрокоманды: второй разряд (3,)5 значение двоичного числа, записываемого в память 1 устройства; третий разряд (jj) - сигнал записи двоичного числа в память 1 устройства; четвертый разряд ()) - сигнал чтения содержимого ячейки памяти 1 устройства, пятый разряд (Т) увеличение счетчика 3} шестой разряд (Dj) - уменьшение счетчика 5; седьмой разряд (3g) - сигнал регистрации

5 считанной из памяти t информации на триггерах 6 и 7, восьмой разряд (1 - сигнал завершения (выход элемента И 38); девятьй разряд (Ig) - сигнал завершения этапа анализа (выход элемента И 30). Если в разряде операционной микрокоманды стоит 1, то соответствующий сигнал вьфабатывается независимо от значений других разрядов. Микрокоман,аа А1 вырабатывает сигналы 3, и 3j, причем О, О, так как записываемое в память 1 двоичное число должно, быть равно нулю; А2 вырабатывает сигналы 3 и DjJ A3 вырабатывает сигнал 1 , А4 вырабатывает сигналы 3g ; А5 вырабатывает сигналы 2 , и J 2 , причем J, 1, так как записываемое в память двоичное число должно быть равно единице; А6 вырабатывает сигнал 3g. После выполнения операционной микрокоманды осуществляется переход к микрокоманде, записанной в следующей ячейке блока 28 памяти микрокоманд.

Управляющие микрокоманды используются для изменения естественного порядка следования микрокоманд, что сводится- к вьшолнению безусловных и условных переходов. Управляющая микрокоманда содержит поле X (со второго по четвертьй разряды), опрёде- ляющее номер анализируемого логического условия (условия Р1, Р2, РЗ, Р4р Р5, Р6) и поле В (с пятого по де- вятый разряды)5 определяющее адрес

0

5

5

0

5

следующей микрокоманды в случае невыполнения анализируемого логического условия. Если X О, то адрес следующей микрокоманды безусловно равен В, т.е. вьтолняется безусловный переход. Условный переход выполняетс следующим образом. Если вьтолняется логическое условие, номер которого задан в поле X микрокоманды, то адре следующей микрокоманды равен (А+1), где А - адрес выполняемой микрокоманды. Если же условие не вьтолняется, то адрес следующей микрокоманды равен В.

Блок управления работает следую- 1ЦИМ образом.

При необходимости включения устройства в работу подается сигнал на вход сброса в нуль счетчика 29, ко- торый обнуляет его содержимое. Это исходное состояние блока 4 управления, т.е. на выходах счетчика 29 устанавливается адрес, равный нулю (адрес первой микрокоманды). При изме- нении адреса на адресных входах блока 28 памяти микрокоманд на его выходах устанавливается содержимое требуемой ячейки, которое заносится в регистр 30 микрокоманд при поступлении тактового сигнала Т1 на вход записи регистра 30 микрокоманд. Выработка управляющих сигналов на выходах блока 4 управления и изменение содержимого счетчика 29 осуществляется тактовым сигналом Т2, поступающим на шину А5. Если в регистре 30 микрокоманд находится операционная микрокоманда (содержимое первого разряда равно нулю), на инверсньм вход элемента И 40 с выхода признака микроко манды регистра 30 микрокоманд поступает разрешающий потенциал, при наличии которого тактовый сигнал Т2, поступающий на вход элемента И 40, поступает на входы элементов И 33-39 и через элемент ИЛИ 44 увеличивает содержимое счетчика 29 на единицу. В результате с выходов тех элементов И 33-39, на входы которых поступают разрешающие потенциалы с соот- ветствукицих выходов регистра 30 микрокоманд, определяемые его содержимым (микрокомандой), поступают сигналы управления, требуемые микрокомандой, и осуществляется переход к еле- дующей микрокоманде. Если в регистре 30 микрокоманд находится управляющая микрокоманда (содержимое первого

f5

.

c 5

0

разряда равно единице), на вход элемента И 41 с вькода признака микрокоманды регистра 30 микрокоманд поступает разрешающий потенциал, при наличии которого тактовый сигнал Т2, поступающий на вход элемента И 41, поступает на входы элемента И 42 и элемента И 43.

Содержимое второго, третьего и четвертого разрядов, регистра 30 микрокоманд (поле X управлякядей микрокоманды) , определяющее номер анализируемого логического условия, поступает на управляющие входы мультиплексора 31, в результате чего значение требуемого микрокомандой логического условия через информационный вход ryльтиплeкcopa 31, определяемое номером логического условия, поступает на выход мультиплексора 31. Если выполняется безусловный переход, или не выполняется требуемое логическое условие (на выходе мультиплексора 31 нулевой потенциал), на инверсньй вход элемента И 43 пост тгает разрешающий потенциал, при наличии которого тактовый сигнал Т2, поступающий на вход элемента И 43, поступает на синх- ровход счетчика 29. В результате в счетчик 29 адреса записывается инфор- , поступающая на его информационные входы с соответствунщих выходов регистра 30 микрокоманд (поле В управляющей микрокоманды). Если логическое условие выполняется, с выхода мультиплексора 31 поступает разрешающий потенциал на вход элемента И 42, при наличии которого тактовый сигнал Т2 через элемент ИЛИ 44 увеличивает содержимое счетчика 29 на единицу.

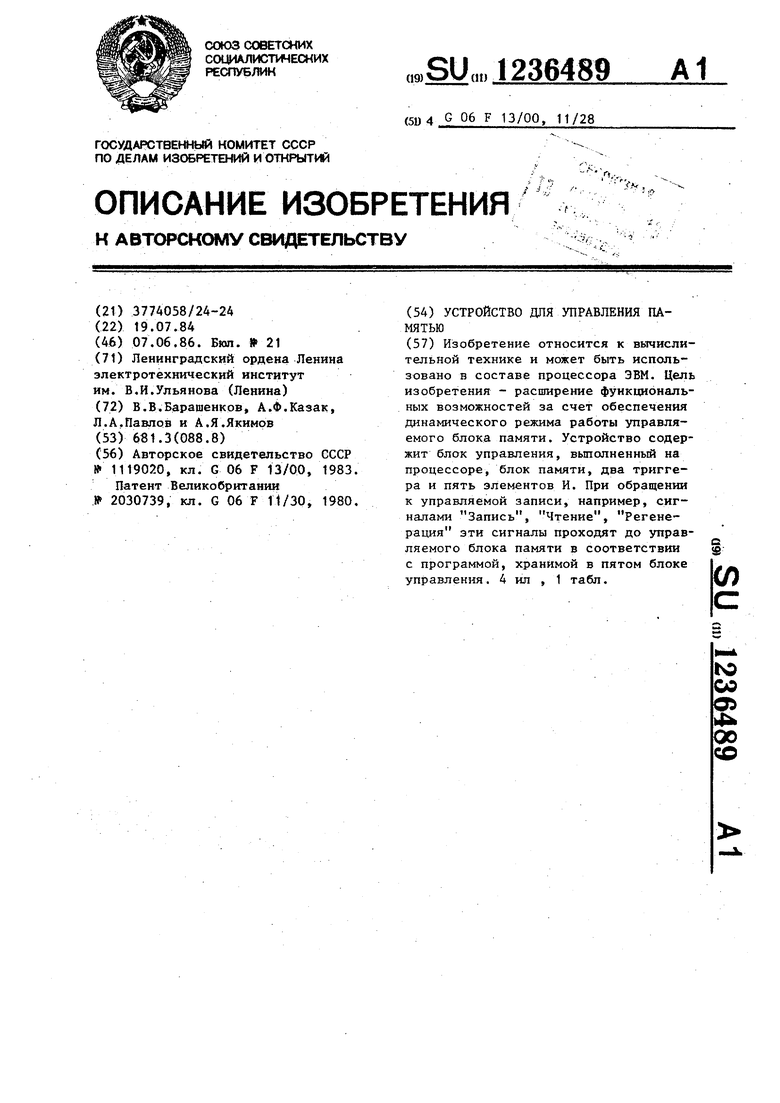

Работа блока 4 управления поясняется временной диаграммой, приведенной на фиг. 4. На ней показано выполнение первых трех микрокоманд микропрограммы при наличии сигнала на входе 47 (логическое условие Р1), и приняты следующие сокращения: НУ - сигнал начального установа СЧА - сигналы на выходах счетчика 29, ПЗУ - сигналы на выходах блока 28 памяти микрокоманд, РМК (1) - сигнал на выходе признака микрокоманд регистра 30 микрокоманд, РМК (2-9) - сигналы на остальных выходах регистра 30 микрокоманд.

Для правильной работы устройства необходимо соблюдение следующих ус- . ловий: длительность импульсов такто9 123648910

вых сигналов Т1 и Т2 определяетсязаписи или чтения) синхронизируются

суммой вреькни считывания информациитактовыми сигналами Т1 и должны прииз дополнительной памяти 1 устройствасутствовать на входах записи/чтеггия

и времени записи информации в тригге-устройства в течение пяти полных такры 6 и 7 устройства; сигналы обраще-j тов следования тактовых сигна НИН к управляемой памяти (сигналылов Т1 .

Формула изобретения

Устройство для управления памя- тью, содержащее счетчик, формирователь адреса, блок памяти, первый триггер, первый и второй элементы И, причем выход формирователя адреса соединен с. адресным входом блока па

мяти, адресные входы формирователя адреса соединены с шиной задания начальных условий устройства, выход первого элемента И соединен с прямым входом второго элемента И, о т л и- чающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения динамического режима работы управляемого блока памяти, оно содержит третий, четвертый и пятьй элементы И, второй триггер и элемент ИЛИ, а также блок управления, содержап1ий счетчик, блок памяти микрокоманд, регистр микрокоманд, мультиплексор, группу элементов И, четьфе элемента И, элемент ИЛИ и элемент ИЛИ-НЕ, причем первый вход элемента ИЛИ соединен с шиной задания режима записи в блок памяти и с первь1ми входами третьего и четвертого элементов И, выход третьего элемента И соединен с первым информационным входом мультиплексора, выход которого соединен с первым входом первого элемента И блока управления и инверсным входом второго элемента И блока управления, выход которог соединен с синхровходом счетчика блока управления, разрядные выходы которого соединены с адресными входами блока памяти микрокоманд, выходы которого соединены с информационными входами регистра микрокоманд, выход признака микрокоманды которого соединен с первым входом третьего эле- мента И блока управления и инверсным входом четвертого элемента И блока управления, выход которого соединен с первыми входами элементов И группы и первым входом элемента ИЛИ блока управления, выход которого соединен с суммирующим входом счетчика блока управления, группа информационных входов которого соединена с группой выходов признака адреса регистра микрокоманд и со вторыми входами первого, второго, третьего, четвертого и пятого элементов И группы, группа выходов кода микрокоманды регистра микрокоманд соединена с группой уп- равлякнцих входов мультиплексора и вторыми входами шестого и седьмого элементов И группы, выходы которых соединены с входами считьшания и записи блока памяти соответственно, выход признака режима работы устройства регистра микрокоманд соединен с третьим управляющим входом мульти

15

20

ч -

30

0

плексора и информационным входом блока памяти, выход которого соединен с инверсным информационным входом первого триггера и информационным входом второго триггера, выход которого соединен с вторым входом- четвертого элемента И и с первым входом первого элемента И, второй вход которого соединен с шиной задания режима чтения в управляемую память, первым входом пятого элемента И и вторым входом элемента ИЛИ, выход которого соединен с вторым информационным входом мульти плексора, третий информационный вход которого соединен с шиной нулевого потенциала устройства, выход пятЬго элемента И группы соединен с входом синхронизации формирователя адреса, выход четвертого элемента И группы соединен с входами синхронизации первого и второго триггеров, выход пер- . вого триггера соединен с вторыми входами второго и пятого элементов И, выход третьего элемента И группы соединен с вычитающим входом счетчика, . разрядные выходы которого соединены . с входами элемента Ш1И-НЕ, выход которого соединен с четверть1м информационным входом мультиплексора, пятый информационный вход которого соединен с выходом второго элемента И, шестой и седьмой информационные входы мультиплексора соединены с входом пуска устройства и входом задания режима работы устройства соответственно, при этом инверсньй вход второго элемента И соединен с шиной задания режима регенерации управляемой памяти, входы сброса первого и второго триггеров соединены с входом сброса уст-- ройства, информационные входы счетчика соединены с шиной задания объема управляемой памяти, выход первого элемента И соединен с входом считывания управляемой памяти, вход синхронизации регистра микрокоманд соединен с первым входом синхронизации устройства, второй вход синхронизации которого соединен с вторым входом третьего элемента И блока управления и прямым входом четвертого элемента И блока управления, выход третьего элемента И блока управления соединен с вторым входом первого элемента И блока, управления и прямым входом второго элемента И блока управления, выход первого элемента И блока управления соединен с вторым входом элемента ИЛИ

блока управления, выходы первого и второго элементов И группы элементов И соединены с выходами подтверждения начала работы устройства и подтверждения работы устройства соответственно, а выходы четвертого и пятого элементов И соединены с вхо - дами запрета записи и чтения управляемой памяти соответстве - нно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство КЭШ-памяти | 1988 |

|

SU1675881A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

Изобретение относится к вычислительной технике и может быть использовано в составе процессора ЭВМ. Цель изобретения - расширение функциональных возможностей за счет обеспечения динамического режима работы управляемого блока памяти. Устройство содержит блок управления, выполненный на процессоре, блок памяти, два триггера и пять элементов И. При обращении к управляемой записи, например, сигналами Запись, Чтение, Регенерация эти сигналы проходят до управляемого блока памяти в соответствии с программой, хранимой в пятом блоке управления. 4 ил , 1 табл. с (Л |С со ОО ;о

18

№nf

- KeedKOfff

| Устройство управления памятью | 1983 |

|

SU1119020A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ВЛАЖНОСТИ СЫПУЧИХ МАТЕРИАЛОВ | 1992 |

|

RU2030739C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-07—Публикация

1984-07-19—Подача