Изобретение относится к вычислительной технике, а именно к специализированным вычислителям, и предназначено для выполнения арифметических операций, вычисления ряда алгебраических и тригонометрических функций, решения задач по преобразованию координат.

Известны арифметические устройства специализированных вычислителей.

Одно из известных [а.с. 824195 СССР Матричное вычислительное устройство, 1981 г.] служит для вычисления нескольких (четырех) алгебраических функций. Его недостатком является необходимость использования больших аппаратурных затрат и промышленного выпуска оригинальных интегральных схем в виде специализированных матриц. Кроме того, крайне узок класс алгебраических функций, реализуемых этим устройством.

Наиболее близким по технической сущности является арифметическое устройство для спецвычислителей [а.с. 526891 СССР Арифметическое устройство, 1974 г.].

Оно содержит три сумматора-вычитателя, два регистра сдвига, четыре группы элементов И, две группы элементов ИЛИ, блок памяти, блок сравнения и блок управления, причем первый выход первого сумматора-вычитателя подключен к первому выходу устройства и к первому входу первого регистра сдвига, выход которого подключен к первым входам первой группы элементов И, первый выход второго сумматора-вычитателя подключен к второму выходу устройства и к первому входу второго регистра сдвига, выход которого подключен к первым входам второй группы элементов И, причем выходы первой и четвертой групп элементов И через первую группу элементов ИЛИ подключены к второму входу второго сумматора-вычитателя, выход которого подключен к первому входу блока сравнения, к второму входу блока сравнения подключен первый выход третьего сумматора, а выход блока сравнения подключен к второму входу блока управления.

Недостатком этого устройства является невозможность вычисления широкого круга алгебраических функций (в частности, дробно-рациональных).

Задачей настоящего изобретения является расширение функциональных возможностей устройства.

Технический результат настоящего изобретения - повышение универсальности устройства за счет возможности вычисления алгебраических функций (типа дробно-рациональных).

Технический результат достигается тем, что в предложенном арифметическом устройстве, которое содержит четыре сумматора-вычитателя, два регистра сдвига, четыре группы элементов И, 2 группы элементов ИЛИ, блок сравнения, блок памяти и блок управления. Устройство имеет по четыре входа и выхода. Первый выход первого сумматора-вычитателя подключен к первому выходу устройства и к первому входу первого регистра сдвига, выход которого подключен к первым входам первой группы элементов И, первый выход второго сумматора-вычитателя подключен к второму выходу устройства и к первому входу второго регистра сдвига, выход которого подключен к первым входам второй группы элементов И, первый вход устройства подключен к первому входу третьего сумматора-вычитателя, второй вход которого подключен к выходу блок памяти.

Кроме того, выходы первой и второй групп элементов И через первую группу элементов ИЛИ подключены ко второму входу второго сумматора-вычитателя, выход которого подключен к первому входу блока сравнения, а ко второму входу блока сравнения подключен первый выход третьего сумматора-вычитателя, выход блок сравнения подключен ко второму входу блока управления.

В устройство дополнительно введен четвертый сумматор-вычитатель, первый вход которого соединен с выходом первого сумматора-вычитателя, а второй вход - с четвертым входом устройства, управляющий вход четвертого сумматора-вычитателя связан с выходом блока-управления, выход четвертого сумматора-вычитателя является четвертым выходом арифметического устройства.

Введение дополнительного четвертого сумматора-вычитателя, его связи внутри устройства расширяют функциональные возможности, арифметического устройства в части возможности вычисления алгебраических функций (а именно, дробно-рациональных). Это является новым техническим решением в технике автономных спецвычислителей, поскольку результаты проведенного заявителем анализа аналогов и прототипа не позволили выявить признаки, тождественные существенным признаком данного изобретения.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявленная совокупность блоков, узлов и связей между ними позволяет расширить функциональные возможности арифметического устройства в части вычисления алгебраических функций (типа дробно-рациональных).

Предложенное арифметическое устройство для выполнения вычислительных операций, включая вычисление дробно-рациональных функций, промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических микросхем).

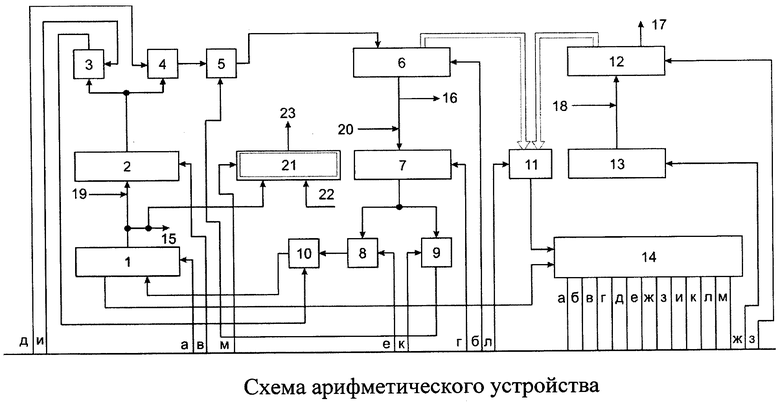

На чертеже приведена структурная блок-схема предлагаемого арифметического устройства. В таблице приведены некоторые алгебраические (дробно-рациональные) функции, дополнительно возможные для реализации в предлагаемом арифметическом устройстве.

Устройство содержит первый сумматор-вычитатель 1, первый регистр сдвига 2, две группы элементов И 3 и 4, группу элементов ИЛИ 5, второй сумматор-вычитатель 6, второй регистр сдвига 7, две группы элементов И 8 и 9, группу элементов ИЛИ 10, блок сравнения 11, третий сумматор-вычитатель 12, блок памяти 13, блок управления 14, (15, 16, 17 и 23 - выходы устройства, 18, 19, 20 и 22 - входы устройства), дополнительно в устройство введен четвертый сумматор-вычитатель 21. Первый выход первого сумматора-вычитателя 1 подключен к первому выходу 15 устройства и к первому входу первого регистра сдвига 2, являющемуся и первым входом 19 устройства, выход регистра 2 подключен к первым входам двух групп элементов И 3 и 4, выходы которых соединены соответственно с первыми входами групп элементов ИЛИ 10 и 5, выходы этих групп элементов ИЛИ соединены соответственно с первым входами сумматоров-вычитателей 1 и 6; первый выход сумматора-вычитателя 6 подключен к второму выходу 16 устройства и первому входу регистра 7, являющимся и вторым входом 20 устройства, выход регистра 7 подключен к первым входам двух групп элементов И 8 и 9, а их выходы подключены соответственно к вторым входам групп элементов ИЛИ 10 и 5. Вторые выходы сумматоров-вычитателей 6, 12 подключены к первому и второму входам блока сравнения 11, выход которого соединен со вторым входом блока управления 14, первый вход которого соединен со вторым выходом сумматора-вычитателя 1; третий выход 17 устройства соединен с одним выходом сумматора-вычитателя 12, вход которого соединен с выходом блока 13 и входом 18 устройства. Одиннадцать выходов блока управления 14 соединены соответственно со вторыми входами сумматоров-вычитателей 1, 6, 12, с вторыми входами регистров сдвига 2, 7, со вторыми входами групп элементов И 3, 4, 8, 9, со входом блока памяти 13 и третьим входом блока сравнения 11.

Кроме того, управляющий вход четвертого сумматора-вычитателя 21 связан с двенадцатым выходом блока управления 14, а первый выход первого сумматора-вычитателя 1 соединен с первым входом четвертого сумматора-вычитателя 21, второй вход и выход которого являются четвертыми входом 22 и выходом 23 всего устройства.

В устройстве использован своеобразный способ вычисления алгебраических (дробно-рациональных) функций путем реализации следующего выражения: F=E±D, где

Действительно, для числителя и знаменателя выражения

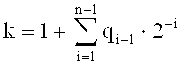

В этом случае искомый результат D окажется равным Ci, к которому будет применено умножение на k (D=k·С) по следующему рекуррентному алгоритму:

где направление итерационного процесса определяется знаком

при этом i=1,2,…,n-1 - номер итерации, n - разрядность чисел. Выполнение условия

Выполнение множительно-делительной операции представляет собой итерационный процесс, реализующий зависимости (1)-(3), и состоит из (n-1) однородных тактов. Далее, результат D с первого выхода 15 первого сумматора-вычитателя (со знаком плюс или минус) по первому входу 22 четвертого сумматора-вычитателя 21. Итоговый результат F=E±D является результатом вычисления алгебраической функции.

Реализация вычисления D происходит так. Число С вводится в первый 1 сумматор-вычитатель, число В - во второй 6 сумматор-вычитатель, а число А - в третий 12 сумматор-вычитатель. В регистрах 2 и 7 путем сдвиговой операции реализуется получение величин С·2-i и В·2-i (i - номер итерации), которые суммируются в соответствии со знаком qi-1 с содержимым сумматоров-вычитателей 1 и 6, в которые они поступают через блоки 3, 10 и 9, 5 соответственно. Знак qi-1 вырабатывается блоком сравнения 11, в котором сравниваются значения А и Bi-1 сумматоров-вычитателей 6 и 12, и сигнал, соответствующий значению qi-1, поступает в блок управления 14, вырабатывающий соответствующие управляющие сигналы. Результат операции

Например, если положить А=х, В=0,5·(x-y), C=y, Е=х-y, то устройство будет способно реализовать функцию

Другие варианты алгебраических дробно-рациональных функций приведены в таблице. Все функции прототипа выполняются без изменений.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 2015 |

|

RU2595906C1 |

| Арифметическое устройство | 2016 |

|

RU2625528C1 |

| Арифметическое устройство | 1974 |

|

SU526891A1 |

| Арифметическое устройство | 1978 |

|

SU746508A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Устройство для вычисления координат | 1978 |

|

SU752350A1 |

| Арифметическое устройство | 1978 |

|

SU780004A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1990 |

|

SU1721613A1 |

| Арифметическое устройство | 1977 |

|

SU728127A2 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1119009A1 |

Изобретение относится к вычислительной технике, для выполнения арифметических операций, вычисления ряда алгебраических и тригонометрических функций, решения задач по преобразованию координат. Технический результат заключается в обеспечении возможности вычисления алгебраических функций типа дробно-рационального. Устройство содержит сумматоры-вычитатели, регистры сдвига, группы логических элементов И, ИЛИ, блок памяти, блок сравнения и блок управления, причем первый выход первого сумматора-вычитателя подключен к первому входу устройства и к первому входу первого регистра сдвига, выход которого подключен к группе элементов И, а первый выход второго сумматора-вычитателя подключен к второму выходу устройства и к первому входу второго регистра сдвига, выход которого подключен к первым входам второй группы элементов И. В устройство дополнительно введен четвертый сумматор-вычитатель, входы которого связаны с выходом первого сумматора-вычитателя, с четвертым входом арифметического устройства соответственно, а выход которого является четвертым выходом всего устройства. 1 ил., 1 табл.

Арифметическое устройство, содержащее три сумматора-вычитателя, два регистра сдвига, четыре группы элементов И, две группы элементов ИЛИ, блок памяти, блок сравнения и блок управления, причем первый выход первого сумматора-вычитателя подключен к первому выходу устройства и к первому входу первого регистра сдвига, выход которого подключен к первым входам первой группы элементов И, первый выход второго сумматора-вычитателя подключен к второму выходу устройства и к первому входу второго регистра сдвига, выход которого подключен к первым входам второй группы элементов И, первый вход устройства подключен к первому входу третьего сумматора-вычитателя, второй вход которого подключен к выходу блока памяти, второй выход первого сумматора-вычитателя подключен к первому входу блока управления, первые восемь выходов которого подключены соответственно к первым входам первого и второго сумматоров-вычитателей, к вторым входам двух регистров сдвига, к вторым входам двух групп элементов И, к третьему входу третьего сумматора-вычитателя и к входу блока памяти, причем выходы первой и четвертой групп элементов И через первую группу элементов ИЛИ подключены к второму входу второго сумматора-вычитателя, выход которого подключен к первому входу блока сравнения, к второму входу блока сравнения подключен первый выход третьего сумматора-вычитателя, выход блока сравнения подключен к второму входу блока управления, девятый, десятый и одиннадцатый выходы которого подключены соответственно к первым входам третьей и четвертой групп элементов И и к третьему входу блока сравнения, выходы второй и третьей групп элементов И через вторую группу элементов ИЛИ подключены к второму входу первого сумматора-вычитателя, вторые входы третьего и четвертой групп элементов И объединены с первыми входами соответственно первой и второй групп элементов И, второй и третий входы устройства подключены соответственно к входам первого и второго регистров сдвига, третий выход устройства поключен к второму выходу третьего сумматора-вычитателя, отличающееся тем, что в него дополнительно введен четвертый сумматор-вычитатель, первый и второй входы которого соединены с выходом первого сумматора-вычитателя и с четвертым входом устройства соответственно, управляющий вход четвертого сумматора-вычитателя связан с выходом блока управления, а выход четвертого сумматора-вычитателя соединен с четвертым выходом устройства.

| US 3971925 A, 27.07.1976 | |||

| Арифметическое устройство | 1986 |

|

SU1451679A1 |

| Арифметическое устройство | 1981 |

|

SU1012240A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

Авторы

Даты

2015-10-10—Публикация

2014-12-30—Подача